## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

### PAULO FRANCISCO BUTZEN

**Leakage Current Modeling in Submicrometer CMOS Complex Gates**

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Renato Perez Ribas Advisor

# **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Butzen, Paulo Francisco

Leakage Current Modeling in Sub-micrometer CMOS Complex Gates / Paulo Francisco Butzen - Porto Alegre: Programa de Pós-Graduação em Computação, 2007.

92 f.:il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR -RS, 2007. Advisor: Renato Perez Ribas.

1. Leakage Current 2. Low-Power Design 3. CMOS. I. Ribas, Renato Perez. II. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-reitor: Prof. Pedro Cezar Dutra da Fonseca

Pró-Reitora de Pós-Graduação: Profa. Valquiria Link Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenadora do PPGC: Profa. Luciana Porcher Nedel

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGMENT**

First, I would like to thank God for my wonderful life.

I would like to thank my family. My parents, Otavio and Gloria, that always look after me, for supporting, and for giving me the best of your heart. Thank you sister Paula, for being my roommate during my undergraduate and master studies, and especially for being my friend from the moment she was born.

Thank you Raquel, for being by my side with love and support since we first met.

I want to thank Professor Renato P. Ribas, my advisor, for the constant and unconditional support in my studies. More than my advisor, you are a good friend. I also want to express my gratitude to Professor Andre Reis, my co-advisor and friend, for all support since my first scholarship back in 2002, and to Professor Chris Kim, at the University of Minnesota, for have accepted me during my internship in his laboratory and for showing me other aspects of the research.

I would like to thank my colleagues from Nangate UFRGS Research Lab and University of Minnesota VLSI Research Lab for the good friendship and the excellent working environment.

Thank you my friends for giving me assistance to get through the difficulties. I want to thank you all for making my life so happy and fulfilled of emotion.

Finally, I acknowledge the CNPq for the scholarship during this Master.

## **TABLE OF CONTENTS**

| LIST                | Γ OF ABREVIATIONS                                 | 6  |

|---------------------|---------------------------------------------------|----|

| LIST                | Γ OF FIGURES                                      | 7  |

| LIST                | Γ OF TABLES                                       | 9  |

| ABS                 | STRACT                                            | 10 |

| RES                 | SUMO                                              | 11 |

| 1 II                | NTRODUCTION                                       | 12 |

| 2 5                 | STATIC CONSUMPTION                                | 18 |

| 2.1                 | Leakage Current Mechanisms                        | 18 |

| 2.1.1               | Subthreshold Current                              | 18 |

| 2.1.2               | 2 Gate Tunneling Current                          | 19 |

| 2.1.3               | Band-to-Band Tunneling Current                    | 20 |

| 2.2                 | 1                                                 |    |

| 2.2.1               | Dual Threshold CMOS                               | 22 |

| 2.2.2               |                                                   |    |

| 2.2.3               |                                                   |    |

| 2.2.4               | $\mathcal{E}$                                     |    |

| 2.2.5               | Body Biasing                                      | 28 |

| 3 5                 | SUBTHRESHOLD LEAKAGE MODEL                        | 31 |

| 3.1                 | Estimation Based on Conductance Association       | 31 |

| 3.2                 | Subthreshold Leakage Models                       |    |

| 3.2.1<br>3.2.2      |                                                   |    |

| 3.2.2               | (,,,                                              |    |

| 3.2.3<br>3.3        |                                                   |    |

| 3.3.1               | Modeling Subthreshold Leakage in CMOS Logic Gates |    |

| 3.3.1               | $\boldsymbol{\mathcal{E}}$                        |    |

| 3.3.2               |                                                   |    |

| 3.3.3<br><b>3.4</b> | Experimental Results                              |    |

|                     | MODEL INCLUDING GATE OXIDE LEAKAGE                |    |

| 4.1                 | Gate Leakage Behavior                             |    |

| 4.2                 | Previous Gate Leakage Models                      | 53 |

|                     | $\varepsilon$                                     |    |

| 4.3 Gate Leakage Model                                                        | 53 |

|-------------------------------------------------------------------------------|----|

| 4.4 Subthreshold and Gate Oxide Leakage Iteration                             |    |

| 4.5 Experimental Results                                                      |    |

| 5 CONCLUSION                                                                  | 61 |

| REFERENCES                                                                    | 63 |

| APPENDIX A PRESENTATION SLIDES                                                | 68 |

| APPENDIX B MODELAGEM DA CORRENTE DE FUGA EM CÉLULA COMPLEXAS SUB-MICROMÉTICAS |    |

## LIST OF ABREVIATIONS

BDD Binary Diagram Decision

BPTM Berkeley Predictive Technology Model

BTBT Band-To-Band Tunneling

CAD Computer-Aided Design

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processor Unit

DIBL Drain-Induced Barrier Lowering

DVTS Dynamic  $V_{th}$  Scaling

ECB Electron Conduction Band

EVB Electron Valence Band

FBB Forward Body Biasing

GIDL Gate-Induced Drain Leakage

HVB Hole Valence Band

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MTCMOS Multi Threshold CMOS

RBB Reverse Body Biasing

SCE Short Channel Effects

SOI Silicon-On-Insulator

VLSI Very Large Scale Integration VTCMOS Variable Threshold CMOS

## **LIST OF FIGURES**

| Figure 1.1: Power distribution of a 0.5µm CMOS microprocessor                              | . 12 |

|--------------------------------------------------------------------------------------------|------|

| Figure 1.2: Dynamic switching power dissipation scheme in CMOS inverter                    |      |

| Figure 1.3: CMOS inverter short-circuit current                                            |      |

| Figure 1.4: Degraded voltage level as input signal to an inverter results in static biasir |      |

| power consumption                                                                          | _    |

| Figure 1.5: Pseudo-NMOS NAND2 gate                                                         |      |

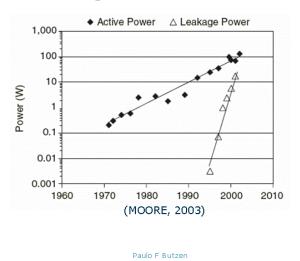

| Figure 1.6: Active and leakage processor power                                             |      |

| Figure 2.1: Major leakage mechanisms in MOS transistor                                     |      |

| Figure 2.2: Three mechanisms of gate dielectric direct tunneling leakage                   | . 20 |

| Figure 2.3: BTBT in reverse-biased pn junction.                                            |      |

| Figure 2.4: Dual V <sub>th</sub> CMOS circuit.                                             |      |

| Figure 2.5: Gate oxide leakage current versus power supply                                 |      |

| Figure 2.6: Two-level multiple static supply voltage scheme                                | . 24 |

| Figure 2.6: Subthreshold leakage current versus number of transistors off in stack         | . 25 |

| Figure 2.7: Subthreshold leakage current versus number of transistors off in stack         | . 25 |

| Figure 2.8: Original (a) and leakage (b) optimized CMOS gate                               | . 26 |

| Figure 2.9: Schematic of MTCMOS circuit                                                    | . 28 |

| Figure 2.10: Schematic of VTCMOS technique.                                                | . 29 |

| Figure 2.11: Schematic of DVTS hardware.                                                   | . 30 |

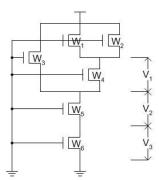

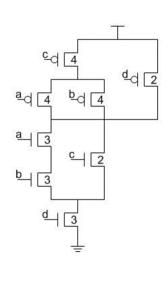

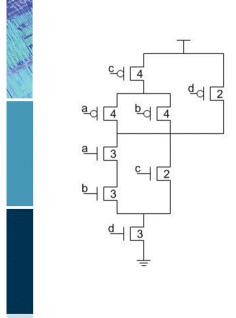

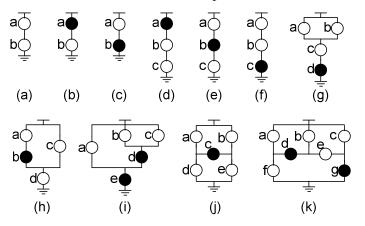

| Figure 3.1: Transistor network with multi-level of series-parallel associations            | . 32 |

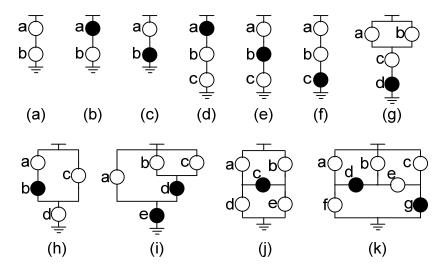

| Figure 3.2: Different transistor arrangements: 3-inputs series-parallel CMOS gates         | . 33 |

| Figure 3.3: Different transistor arrangements: 4-inputs series-parallel CMOS gates         | . 33 |

| Figure 3.4: Subthreshold leakage currents in CMOS structure from Figure 3.3 (h), for       | •    |

| each input vector                                                                          |      |

| Figure 3.5: Average subthreshold leakage current in the different CMOS structures from     | om   |

| Figure 3.2 and Figure 3.3.                                                                 |      |

| Figure 3.6: Two-transistor stack.                                                          |      |

| Figure 3.7: NMOS series-parallel network.                                                  | . 39 |

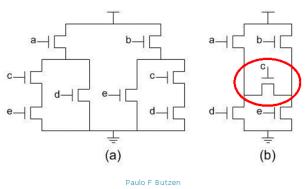

| Figure 3.8: SP (a) and non-SP (b) transistor arrangements of the same logic function       |      |

| Figure 3.9: Influence of on-transistor in off-stack leakage current.                       | . 43 |

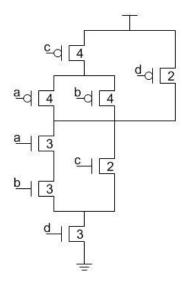

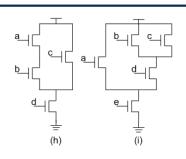

| Figure 3.10: Pull-down NMOS networks.                                                      | . 44 |

| Figure 3.11: Subthreshold leakage average for Figure 3.10 (h), (i) and (j) pull-down       |      |

| networks.                                                                                  |      |

| Figure 3.12: CMOS complex gate, with different transistor sizing, according to Logic       |      |

| Effort.                                                                                    |      |

| Figure 3.13: Variation of subthreshold leakage current in terms of power supply volta      | _    |

| variation                                                                                  | . 48 |

| Figure 3.14: Variation of subthreshold leakage current according to the operating         |

|-------------------------------------------------------------------------------------------|

| temperature variation                                                                     |

| Figure 3.15: Variation of subthreshold leakage current according to the threshold         |

| voltage variation                                                                         |

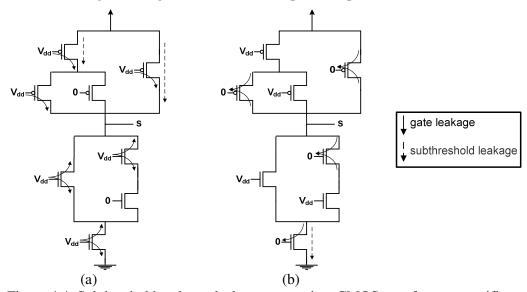

| Figure 4.1: (a) Gate leakage current from the gate to channel and source/drain overlap    |

| region. (b) Gate leakage current from the source/drain overlap region to gate             |

| 50                                                                                        |

| Figure 4.2: Variation of tunneling current density with potential drop across the oxide.  |

| 51                                                                                        |

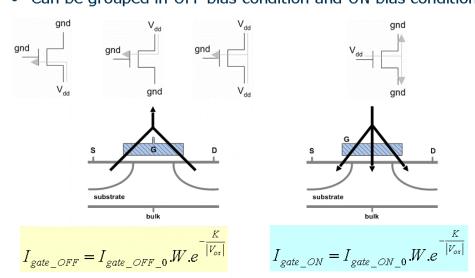

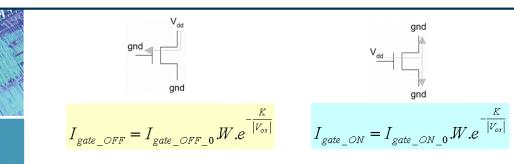

| Figure 4.3: Possible bias condition for NMOS transistors in CMOS logic circuits 52        |

| Figure 4.4: Subthreshold and gate leakage current in a CMOS gate for tow specific         |

| input vectors                                                                             |

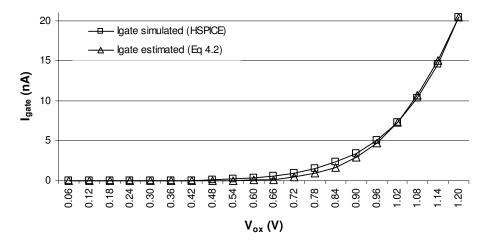

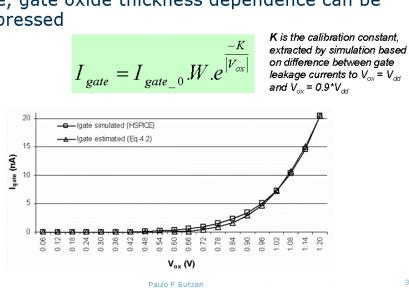

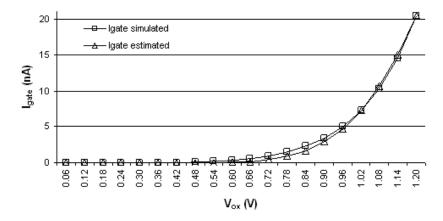

| Figure 4.5: Gate leakage proposed model accuracy compared to HSPICE simulation 54         |

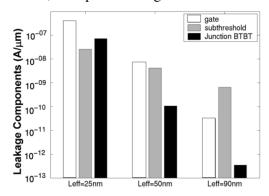

| Figure 4.6: Contribution of different leakage components in NMOS devices at different     |

| technology generation55                                                                   |

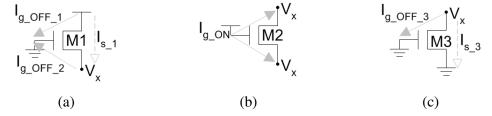

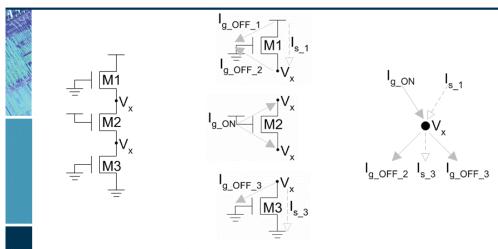

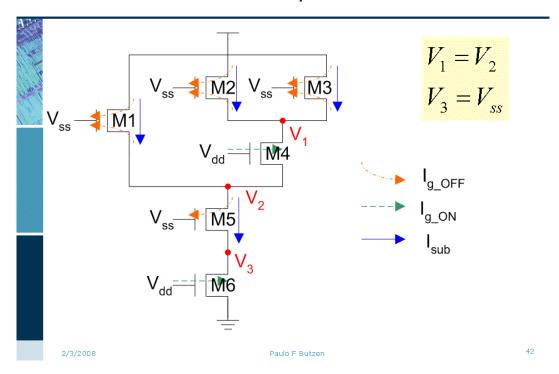

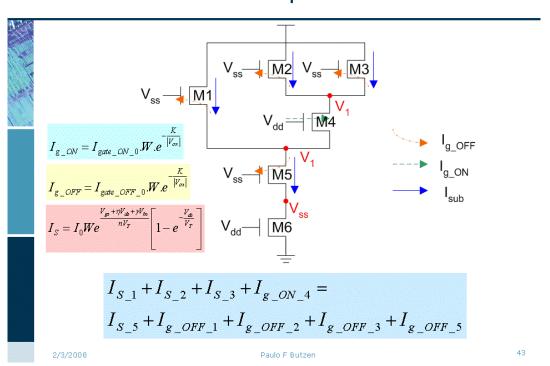

| Figure 4.7: Three stack transistor arrangement                                            |

| Figure 4.8: Leakage currents in each transistor of arrangement depicted in Figure 4.7. 56 |

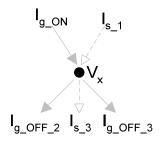

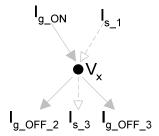

| Figure 4.9: Currents in $V_x$ node                                                        |

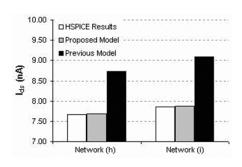

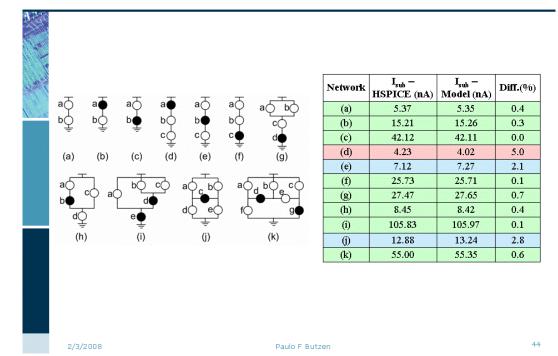

| Figure 4.10: Pull-down NMOS networks                                                      |

| Figure 4.11: CMOS complex gate, with different transistor sizing, according to the        |

| Logic Effort 59                                                                           |

## **LIST OF TABLES**

| Table 2.1: Subthreshold leakage current for 2-input NAND gate                     | 25        |

|-----------------------------------------------------------------------------------|-----------|

| Table 3.1: Normalized subthreshold leakage current in Figure 3.3 (h)              | 34        |

| Table 3.2: Correlation between empirical method and HSPICE for the worst-case     | se and    |

| average leakage normalized values of different CMOS structures from               | n Fig 3.2 |

| and 3.3                                                                           | 35        |

| Table 3.3: Proposed models accuracy for two stacked transistors                   | 38        |

| Table 3.4: Parameters used in the analytical model                                | 43        |

| Table 3.5: Subthreshold leakage current related to the off-networks depicted in   | Figure    |

| 3.10                                                                              | 44        |

| Table 3.6: Input dependence leakage estimation in logic network (h) from Figur    | e 3.10    |

| (pull-down NMOS tree)                                                             | 45        |

| Table 3.7: Input dependence leakage estimation in logic network (i) from Figure   | e 3.10    |

| (pull-down NMOS tree).                                                            | 45        |

| Table 3.8: Input dependence leakage estimation in logic network (j) from Figure   | e 3.10    |

| (pull-down NMOS tree).                                                            | 46        |

| Table 3.9: Subthreshold leakage current related to the CMOS complex gate dep      |           |

| Figure 3.9                                                                        | 47        |

| Table 4.1: Parameters used in the analytical model                                | 58        |

| Table 4.2: Total leakage current related to the off-networks depicted in Figure 4 | .1059     |

| Table 4.3: Total leakage current related to the CMOS gate depicted in Figure 4.   | 11 60     |

## **ABSTRACT**

To maintain performance at reduced power supply voltage, transistor threshold voltages and dimensions have been scaled down for decades. Scaling transistor into the sub-100nm technologies has resulted in a dramatic increase in leakage currents, which have become a significant portion of the total power consumption in scaled technologies, in many case achieving 30-50% of the overall power consumption under nominal operating conditions. For this condition, standby currents in CMOS logic gates represent an important challenge in nanometer technologies, leakage dissipation being a critical factor in low-power design. It means the static power dissipation should be considered as soon as possible in the integrated circuit design flow.

This thesis reviews the major leakage current mechanisms and several reduction techniques. It presents the development of a straightforward method for very fast estimation of subthreshold current in CMOS series-parallel logic gates. This estimation method is based on electrical conductivity association of series-parallel transistor arrangements. Combined with a gate oxide leakage model based on transistor bias condition, it is possible to provide a better prediction of total leakage consumption in transistor networks.

The previous estimation method is fast but it is not focused on accuracy. A new accurate subthreshold and gate leakage current estimation method is also developed based on simplified analytical leakage currents models. Instead of previous works focused on series-parallel device arrangements, this method evaluates the leakage in general transistor networks. The presence of on-switches in off-networks, ignored by previous works, is also considered in the proposed static current analysis. The new leakage model has been validated through electrical simulations, taking into account a 130nm and 90nm CMOS technology, with good correlation of the results, demonstrating the model accuracy.

**Keywords:** Leakage current, Low Power Circuits, CMOS

.

## Modelagem de Corrente de Fugas em Portas Lógicas CMOS Submicrométricas

## **RESUMO**

Para manter o desempenho a uma tensão de alimentação reduzida, a tensão de *threshold* e as dimensões dos transistores têm sido reduzidas por décadas. A miniaturização do transistor para tecnologias sub-100nm resulta em um expressivo incremento nas correntes de fuga, tornando-as parte significativa da potencia total, alcançando em muitos casos 30-50% de toda a potencia dissipada em condições normais de operação. Por estas condições, correntes estáticas em células CMOS representam um importante desafio em tecnologias nanométricas, tornando-se um fator crítico no design de circuitos de baixa potência. Isto significa que dissipação de potência estática deve ser considerada o quanto antes no fluxo de projetos de circuitos integrados.

Esta tese revisa os principais mecanismos de fuga e algumas técnicas de redução. Também é apresentado um modelo de estimativa rápida da corrente de *subthreshold* em células lógicas CMOS série - paralelo. Este método é baseado em associações de condutividade elétrica série - paralelo de transistores. Ao combinar com o modelo de estimativa da corrente de fuga de *gate* baseada nas condições estáticas dos transistores é possível fornecer uma melhor predição da corrente de fuga total em redes de transistores.

O modelo de estimativa anterior é rápido porem seu foco não esta na precisão. Um novo e preciso modelo para corrente de fuga de *subthreshold* e de *gate* é também apresentado baseado em modelos analíticos simplificados das correntes de fuga. Ao contrario do modelo anterior que era destinado a redes de transistores serie – paralelo, o novo método avalia as correntes de fuga em rede de transistores complexas. A presença de transistores conduzindo em redes de transistores não conduzindo, ignorados em trabalhos anteriores, é também avaliado no trabalho proposto. O novo modelo de corrente de fuga foi validado através de simulações elétricas, considerando processos CMOS 130nm e 90nm, com boa correlação dos resultados, demonstrando a precisão do modelo.

Palavras-Chave: Corrente de Fuga, Circuitos de Baixo Consumo, CMOS.

## 1 INTRODUCTION

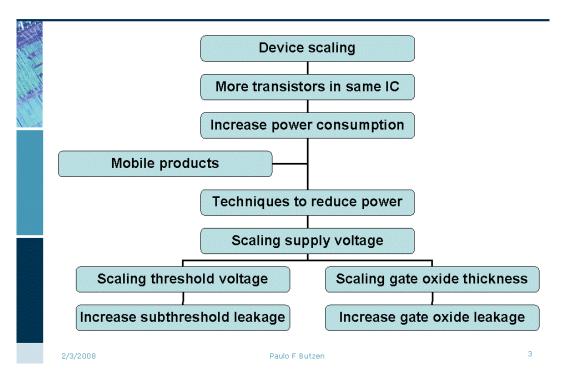

In the past, the major concerns of the VLSI designers were performance and miniaturization. With the explosive growth in portable computing and wireless communication in the last few years, power dissipation has become a critical issue. Problems with heat removal and cooling are worsening because the magnitude of power dissipated per unit area is growing with scaling. Years ago, portable battery-powered applications were characterized by low computational requirement. Nowadays, these applications require the same computational performance as non-portable applications. It is important to prolong the battery life as much as possible. These are two reasons that power dissipation becomes a challenge for circuit designers and a critical factor in the future of microelectronics.

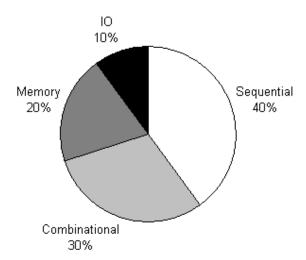

An integrated circuit is composed by sequential circuits, combinational circuits, memories blocks and I/O devices. Each one gives its own contribution to the total power dissipation in integrated circuits. Figure 1.1 shows the approximate power distribution of a microprocessor implemented in 0.5µm CMOS process (GRONOWSKI, 1998). Power consumption is concentrated in the logic circuits, 40 % in sequential blocks and 30 % in combinational blocks. Memory blocks and I/O device represent approximately 30% of the total power. Similar behavior is observed in different microprocessors (TAKAYANAGI, 2005) (LEON, 2007).

Figure 1.1: Power distribution of a 0.5µm CMOS microprocessor (GRONOWSKI, 1998).

There are four sources of power dissipation in digital CMOS circuits, as describe in equation 1.1.

$$P = P_{\text{dynamic-switching}} + P_{\text{short-circuit}} + P_{\text{static-biasing}} + P_{\text{leakage}}$$

(1.1)

where P is the total power dissipation,  $P_{dynamic-switching}$  is the dynamic switching power,  $P_{short-circuit}$  is the short-circuit power,  $P_{static-biasing}$  is the static biasing power and  $P_{leakage}$  is the leakage power.

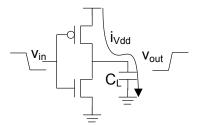

Dynamic switching power dissipation is caused by charging capacitances in the circuit. Considering  $C_L$  the model of routing and input gates capacitance, in a CMOS inverter, for instance, during each low-to-high output transition,  $C_L$  is charged through the PMOS transistor, and a certain amount of energy is drawn from the power supply. Part of this energy is dissipated in the PMOS device and part is stored on  $C_L$ . It is discharged during the high-to-low output transition, and the stored energy is dissipated in the NMOS transistor.

Figure 1.2: Dynamic switching power dissipation scheme in CMOS inverter.

Considering the CMOS inverter, shown in Figure 1.2, and assuming that the input waveform has zero rise and fall times, the energy consumption during low-to-high output transition can be derived by integrating the instantaneous power over the period of interest. Equation (1.2) shows that it draws  $C_L \cdot V_{dd}^2$  Joules from the power supply.

$$E_{V_{dd}} = \int_0^\infty i_{V_{dd}}(t) V_{dd} dt = V_{dd} \int_0^\infty C_L \frac{dV_{out}}{dt} dt = C_L V_{dd} \int_0^{V_{dd}} dV_{out} = C_L V_{dd}^2$$

(1.2)

The charge stored on the load capacitor is equal to  $C_L V_{dd}^2/2$  by equation (1.3). This means that only half of the energy supplied by the power source is stored in  $C_L$ . The other half had been dissipated by the PMOS transistor. The high-to-low output transition dissipates the energy stored on the load capacitance into the NMOS transistor.

$$E_{C_L} = \int_0^\infty i_{V_{dd}}(t) v_{out} dt = \int_0^\infty C_L \frac{dv_{out}}{dt} v_{out} dt = C_L \int_0^{V_{dd}} v_{out} dv_{out} = \frac{C_L V_{dd}^2}{2}$$

(1.3)

To compute the power consumption, it is necessary to take into account how often the circuit is switched. Given a gate switching frequency f, the power drawn from the supply is given by:

$$P_{\text{dynamic-switching}} = C_L V_{dd}^2 f \tag{1.4}$$

The dynamic switching power dissipation was the dominant factor compared with the other components of power dissipation in digital CMOS circuits for technologies down to 0.18µm, where it is about 90% of total circuit dissipation (PARK, 2006).

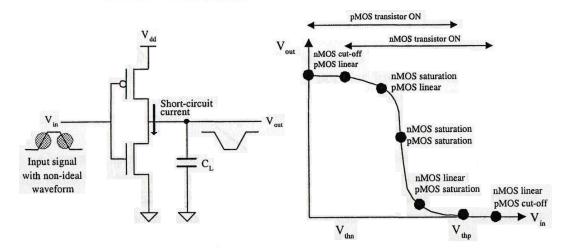

Short–circuit power is the second source of total power dissipation described in equation (1.1). During a transient on input signal, there will be a period in which both NMOS and PMOS transistor will conduct simultaneously, causing a current flow through the direct path existing between power supply and ground terminals. This effect usually happens for very small intervals. In a static CMOS inverter this current flows as long as the input voltage is higher than a NMOS threshold voltage ( $V_{thn}$ ) above ground and lower than a PMOS threshold voltage ( $V_{thp}$ ) below the power supply, as shown in Figure 1.3. It is proportional to the input ramp, the output load, and the transistor size. It can be approximated by (VEENDRICK, 1984), according to equation (1.5)

$$P_{short-circuit} = K(V_{dd} - 2V_{th})^3 \cdot \tau \cdot f \tag{1.5}$$

where K is a constant that depends on the transistor sizes, as well as on the technology,  $V_{dd}$  is the supply voltage,  $V_{th}$  is the threshold voltage,  $\tau$  is the rise or fall time of the input signal, and f is the clock frequency.

Figure 1.3: CMOS inverter short-circuit current (SOUNDRIS, 2002).

This component represents less than 20% of the dynamic switching power consumption if the NMOS and PMOS transistors are sized in order to balance the rise/fall signal slopes at input and output nodes (VEENDRICK, 1984).

Both of the above sources of power dissipation in CMOS circuits are related to transitions at gate terminals and for that reason are collective referred as dynamic power dissipation. On the other hand, the last two sources of power dissipation, static biasing and leakage, are related to the current that flows when the gate terminals are not changing, and are therefore collectively referred as static power dissipation.

Ideally, in the steady state of CMOS circuits there is no static power dissipation. This is the most attractive characteristic of CMOS technology. However, the actual operation of CMOS circuits is slightly different. Degraded voltage levels feeding CMOS gates and pseudo-NMOS logic family, present a current flow from the power supply to ground nodes. This flow is known as static biasing current.

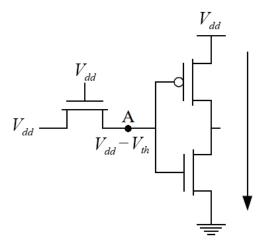

In Figure 1.4, a NMOS pass-transistor drives an inverter. From basic CMOS circuit theory is known that the voltage in node A is degraded ( $V_{dd}$ - $V_{th}$ ). Since the inverter input is high ( $V_{dd}$ - $V_{th}$ ), its output should be low. However, the PMOS transistor will be weakly ON and, thus, present a static biasing current from power supply to ground nodes.

Figure 1.4: Degraded voltage level as input signal to an inverter results in static biasing power consumption.

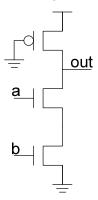

Pseudo-NMOS logic gate consists of a single PMOS transistor, whose gate terminal is always grounded, and a NMOS pull-down network, which implements the boolean function. A pseudo-NMOS NAND gate is depicted in Figure 1.5. The main advantages of the pseudo-NMOS logic family are area and performance due to the inexistence of the PMOS pull-up network. However, when the NMOS pull-down network is conducting, there always exists a static biasing current from the power supply to ground, because the PMOS transistor is always ON.

Figure 1.5: Pseudo-NMOS NAND2 gate.

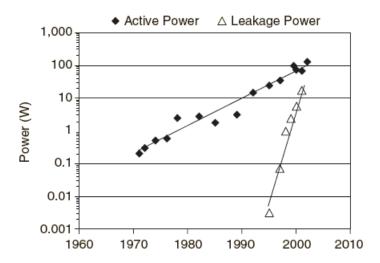

The static biasing current only happen in specific conditions as reported above. Static current that flows from  $V_{dd}$  to ground nodes, without degraded inputs or in pseudo-NMOS logic family is known as leakage power. It is the main factor responsible for power dissipation during idle mode in standard CMOS gates. In past technologies the magnitude of leakage current was low and usually neglected. But as the devices have been being scaled to achieve higher density, performance, and lower dynamic power consumption, the leakage current in the nanometer regime is becoming a significant portion of power dissipation in CMOS circuits, as depicted in Figure 1.6.

Figure 1.6: Active and leakage processor power (MOORE, 2003).

The power consumption reduction in digital systems involves optimization at all levels of design. This optimization includes the technology used to implement digital circuits, the design, the architecture, and the algorithm that are being implemented.

Optimization in technology level are related to materials used in fabrication process, like high-K gate dielectric and metal gates (SINGER, 2007), its dimension and concentration, like oxide thickness and substrate profile, and device structure, like "halo" doping (OGURA, 1980) and silicon-on-insulator (SOI) structures (DONAGHY, 2001). Design level involves optimization in physical and logic design. Place and route, and transistor sizing, are example of physical design optimization. Reduction in swing logic, logic minimization and technology mapping are example of logic design optimization techniques (CHANDRAKASAN, 1995). Architectural level typically presents solutions based on parallel or pipelined structures to achieve the same performance with a reduce supply voltage (ROY, 2000). Algorithm level explores the concurrency to be implemented in a parallel architecture and the minimization of the number of operations to reduce the switching activity, and consequently the dynamic consumption (CHANDRAKASAN, 1995).

When designing VLSI circuits, designers have to respect a power specification. Accurate and efficient power estimation during the design phase is required in order to meet the power specification without a costly redesign process. It is important to estimate both average and maximum power in CMOS circuits at different levels of design abstraction. The average power dissipation is important to determine battery life, while the maximum power demanded is related to circuit reliability issues.

This work tries to provide a deep understanding of the static power dissipation in CMOS circuits.

Different leakage mechanisms contribute to the total leakage current in MOS device. The three major types of leakage mechanisms are subthreshold, gate oxide and reverse-bias pn-junction leakage (BTBT – band-to-band tunneling). In addition to these three major leakage components, there are other ones like gate-induced drain leakage (GIDL) and punchthrough current. Those components can be neglected in normal modes of operation (AGARWAL, 2005). These leakage mechanisms are reported in Chapter 2.

The great majority of digital circuits are designed for the highest performance to satisfy the system frequency requirement. These circuits are typically composed by large gates, logic duplication and high parallel architectures. In this case the leakage power consumption is significant. However, not every application requires a fast circuit to operate at the highest level all the time. Some modules can be in idle mode often, and consequently, there is an opportunity to reduce the leakage power consumed. Chapter 2 also explores different circuit techniques to reduce leakage consumption.

The models to treat the leakage mechanisms (SHEU, 1987) (CAO, 2000) are still too complicated and they are hardly used by circuit designers. Precise simulators, such as HSPICE, can accurately account for leakage current, but they are only proper for small circuits due their solution convergence, explosion of memory and CPU time problems. Faster techniques to estimate the subthreshold and gate leakage current have been proposed in the literature (CHEN, 1998) (YANG, 2005). However, only basic series and parallel arrangements of transistor have been addressed. An improved subthreshold leakage model to be applied in general transistors networks is described in Chapter 3. Gate leakage model is presented in Chapter 4 and included in previous subthreshold model. Final conclusions are presented in Chapter 5.

## 2 STATIC CONSUMPTION

To achieve higher integration density and improved performance, CMOS devices have scaled down in each technology generation. However, static power dissipation has increased drastically with technology scaling and become a significant contributor to the total power dissipation in CMOS circuits. This chapter attempts to review the major leakage mechanisms and design techniques to reduce leakage power consumption in such technologies.

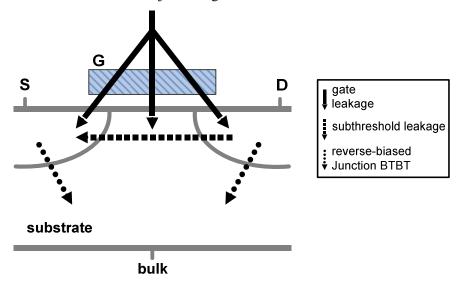

## 2.1 Leakage Current Mechanisms

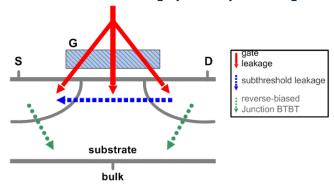

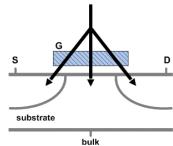

For nanometer devices, leakage current is dominated by subthreshold leakage, gate-oxide tunneling leakage, and reverse-bias pn-junction leakage. Those three major leakage current mechanisms are illustrated in Figure 2.1. There are other leakage components, like gate induced drain leakage (GIDL) and punchthrough current, but those can be neglected in normal mode of operation (AGARWAL, 2005). In this section will be discussed those three major leakage mechanisms.

Figure 2.1: Major leakage mechanisms in MOS transistor.

#### 2.1.1 Subthreshold Current

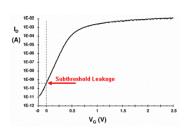

Supply voltage has been scaled down to keep dynamic power consumption under control. To maintain a high drive current capability, the threshold voltage has to be scaled too. However, the threshold voltage scaling results in increasing subthreshold leakage currents. Subthreshold current occurs between drain and source when transistor

is operating in weak inversion region, i.e., the gate voltage is below the threshold voltage.

The drain-to-source current is composed by drift current and diffusion current. The drift current is the dominant mechanism in strong inversion regime, when the gate-to-source voltage exceeds the threshold voltage. In weak inversion, the minority carrier concentration is almost zero, and the channel has no horizontal electric field, but a small longitudinal electric field appears due the drain-to-source voltage. In this situation, the carries move by diffusion between the source and the drain of MOS transistor. Therefore, the subthreshold current is dominated by diffusion current and it depends exponentially on both gate-to-source voltage and threshold voltage.

From the BSIM MOS transistor model (SHEU, 1987), the subthreshold leakage current for a MOSFET device can be expressed as:

$$I_{subthreshold} = I_0 e^{\frac{V_{gs} - V_{th}}{nV_T}} \left[ 1 - e^{-\frac{V_{ds}}{V_T}} \right]$$

(2.1)

where

$$I_0 = \frac{W\mu_0 C_{ox} V_T^2 e^{1.8}}{L}$$

,  $V_T = \frac{KT}{q}$  is the thermal voltage,  $V_{th}$  is the threshold voltage,

$V_{ds}$  and  $V_{gs}$  are the drain-to-source and gate-to-source voltage respectively. W and L are the effective transistor width and length, respectively.  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the carrier mobility and n is the subthreshold swing coefficient.

In short channel devices, source and drain depletion regions penetrate significantly into the channel influencing the field and potential profile inside that. These are known as short channel effects (SCE). Such effects reduce transistor threshold voltage due to the channel length reduction ( $V_{th}$  roll-off) and the DIBL increasing. This results in significant subthreshold current in short channel devices.

#### 2.1.2 Gate Tunneling Current

As mentioned before, the aggressive device scaling in nanometer regime increases short channel effects such as DIBL and  $V_{th}$  roll-off. To control the short channel effects, oxide thickness must also become thinner in each technology generation. Aggressive scaling of the oxide thickness, in turn, gives rise to high electric field, resulting in a high direct-tunneling current through transistor gate insulator.

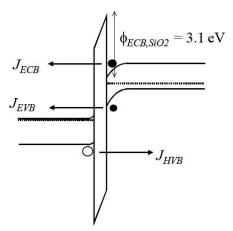

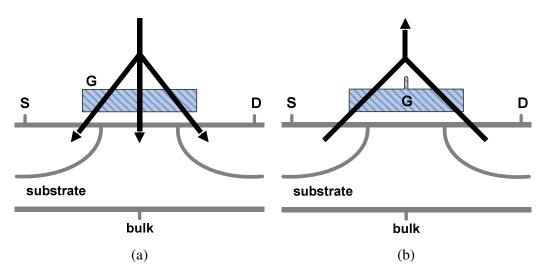

Gate direct tunneling current is due to the tunneling of electrons (or holes) from the bulk and source/drain overlap region through the gate oxide potential barrier into the gate (or vice-versa). This phenomenon is related with the MOS capacitance concept. There are three major gate leakage mechanisms for a MOS structure. The first one is the electron conduction-band tunneling (ECB), which is due to the tunneling of electrons from conduction band of the substrate to the conduction band of the gate (or vice versa). The second one is the electron valence-band tunneling (EVB). It is due to the tunneling of electrons from the valence band of the substrate to the conduct band of the gate. The last one is known as hole valence-band (HVB) tunneling. It is due to the tunneling of holes from the valence band of the substrate to the valence band of the gate (or vice-versa). Figure 2.2 illustrates these three mechanisms.

Figure 2.2: Three mechanisms of gate dielectric direct tunneling leakage (CAO, 2000).

Each mechanism is dominant or important in different regions of operation for NMOS and PMOS transistors. For each mechanism, gate leakage current can be modeled by (ROY, 2003):

$$I_{gate} = W.L.A \left(\frac{V_{ox}}{t_{ox}}\right)^{2} \exp \left(\frac{-B\left(1 - \left(1 - \frac{V_{ox}}{\phi_{ox}}\right)^{\frac{3}{2}}\right)}{\frac{V_{ox}}{t_{ox}}}\right)$$

(2.2)

where W and L are the effective transistor width and length, respectively,  $A = q^3/16\pi^2 h\phi_{ox}$ ,  $B = 4\pi\sqrt{2m_{ox}}\phi_{ox}^{3/2}/3hq$ ,  $m_{ox}$  is the effective mass of the tunneling particle,  $\phi_{ox}$  is the tunneling barrier height,  $t_{ox}$  is the oxide thickness, h is  $1/2\pi$  times Planck's constant and q is the electron charge.

#### 2.1.3 Band-to-Band Tunneling Current

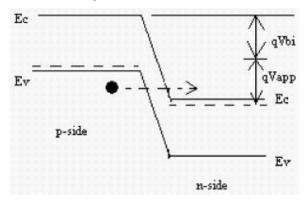

The MOS transistor has two pn junctions – drain and source to well junctions. These two pn junctions are typically reverse biased, causing a pn junction leakage current. This current is a function of junction area and doping concentration. When n and p regions are heavily doped, band-to-band tunneling (BTBT) leakage dominates the reverse biased pn junction leakage mechanism.

A high electric field across a reverse biased pn junction causes a current flow through the junction due to tunneling of electrons from the valence band of the p-region to the conduction band of the n-region, as shown in Figure 2.3.

Tunneling current occurs when the total voltage drop across the junction (applied reverse bias  $(V_{app})$  + built-in voltage  $(\psi_{bi})$ ) is larger than the band-gap. The tunneling current density through a silicon p-n junction is given by (ROY, 2003):

$$J_{BTBT} = A \frac{EV_{app}}{E_g^{1/2}} \exp\left(-B \frac{E_g^{3/2}}{E}\right)$$

(2.3)

where  $A = \sqrt{2m^*q^3}/4\pi^3h^2$ , and  $B = 4\sqrt{2m^*/3hq}$ .  $m^*$  is the effective mass of electron; Eg is the energy-band gap;  $V_{app}$  is the applied reverse bias; E is the electric field at the junction; q is the electron charge; and h is  $1/2\pi$  times the Planck's constant.

Figure 2.3: BTBT in reverse-biased pn junction (ROY, 2003).

Band-to-band tunneling leakage, negligible in current processes when compared to the subthreshold and gate leakages, starts to be taken into account in 25nm technologies (MUKHOPADHYAY, 2005).

The junction tunneling current depends exponentially on the junction doping and the reverse bias across the junction. Forward body bias can be used to reduce the band-to-band tunneling leakage.

## 2.2 Leakage Reduction Techniques

In CMOS circuit, the total power dissipation includes dynamic and static components during the active mode of operation. In the case of standby mode, the power dissipation is due to leakage currents. According to leakage mechanisms described in previous section, leakage power increases dramatically in the scaled devices. Particularly, with reduction of threshold voltage, to achieve high performance, leakage power becomes a significant component of total power consumption in both active and standby modes of operation.

To suppress power consumption in low-voltage circuits, it is necessary to reduce leakage power in both active and standby modes of operation. Reduction in leakage current can be achieved using both process and circuit level techniques. At process level, leakage reduction can be achieved by controlling the dimensions (length, oxide thickness, junction depth, etc.) and doping profile in transistor. At circuit level, several techniques to reduce leakage consumption have been proposed in the literature (ROY, 2003) (GUINDI, 2003) (PARK, 2006).

To reduce leakage currents, these techniques explore supply and threshold voltage leakage dependence, as well as concepts of stacking effect and body bias. Major focus of this section is to present several reduction techniques and the concepts explored in each one.

#### 2.2.1 Dual Threshold CMOS

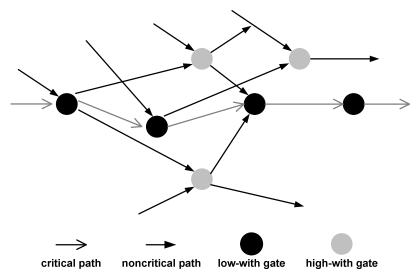

Dual threshold CMOS is a static technique that exploit the delay slack in non-critical paths to reduce leakage power. It provides both high and low threshold voltage transistors in a single chip that are used to deal with the leakage problem.

Fabrication process can achieve a different threshold voltage device by varying different parameters. Changing the channel doping profile, increasing the channel length, changing the body bias, and using a higher gate oxide thickness are examples of fabrications parameters that can be changed to achieve high threshold voltage transistor. Each parameter has its own trade-off in terms of process cost, effect on different leakage components, and short channel effects.

High  $V_{th}$  transistors suppress the subthreshold current, while low  $V_{th}$  transistors are used to achieve high performance. For a logic circuit, the transistors in non-critical paths can be assigned high threshold voltage to reduce subthreshold leakage current, while the performance is not sacrificed by using low  $V_{th}$  transistors in the critical paths (WEI, 1999). It has the same critical delay as the single low  $V_{th}$  CMOS circuits, while leakage power is saving in non-critical paths. Therefore, no additional control circuitry is required, and both high performance and low leakage power can be achieved simultaneously.

Dual threshold CMOS is effective in reducing leakage power during both standby and active modes without delay and area overhead. Researchers have proposed many others design techniques based on dual threshold CMOS. One considers upsizing a high  $V_{th}$  transistor to improve performance, but it is cause an area penalty (PANT, 1998). Figure 2.4 illustrates the basic idea of a dual  $V_{th}$  circuit.

Figure 2.4: Dual  $V_{th}$  CMOS circuit (ROY, 2003).

With the increase in  $V_{th}$  variation and supply voltage scaling, it is becoming difficult to maintain sufficient gap among low  $V_{th}$ , high  $V_{th}$  and supply voltage required for dual  $V_{th}$  design. Furthermore, dual  $V_{th}$  design increases the number of critical paths in a die. It has been shown in (BOWMAN, 2002) that as the number of critical paths on a die increases, within-die delay variation causes both mean and standard deviation of the die frequency distribution to become smaller, resulting in reduced performance.

#### 2.2.2 Supply Voltage Scaling

Supply voltage scaling is used to reduce dynamic and leakage power. It was originally developed for switching power reduction. It is an effective method of consumption reduction due to the quadratic dependence of the switching power in relation to supply voltage. Supply voltage scaling also provides leakage power savings.

Lowering supply voltage provides an exponential reduction in subthreshold current resulting from Drain-Induced Barrier Lowering (DIBL) effect. The DIBL effect tends to become more severe with process scaling to shorter gate lengths. For this reason, the achievable savings by this technique will increase with technology scaling.

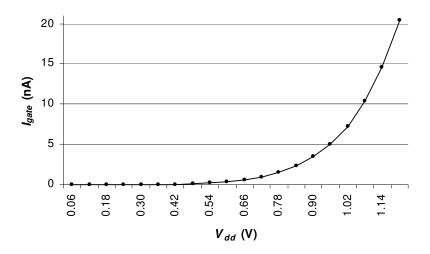

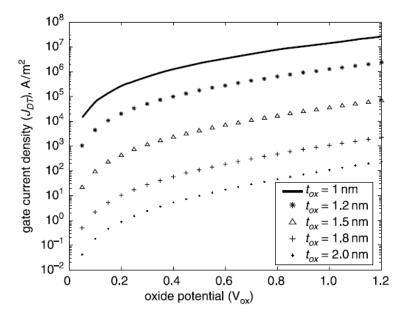

Gate oxide leakage is also affected by this technique. Lowering  $V_{dd}$  will reduces gate leakage even faster than subthreshold leakage (KRISHNAMURTHY, 2002). Figure 2.5 shows how gate tunneling current reduces as  $V_{dd}$  decrease. Thus, this technique saves standby power by decreasing subthreshold and gate leakage currents.

Figure 2.5: Gate oxide leakage current versus power supply.

In theory, the standby power supply for a circuit can decrease to zero, but the circuit will lose performance and all of it states. The optimal point for power savings using this technique is the lowest voltage for which the circuit retains state and does not compromising performance (WANG, 2006).

To achieve low-power benefits without compromising performance, two ways of lowering supply voltage can be employed: static supply scaling and dynamic supply scaling.

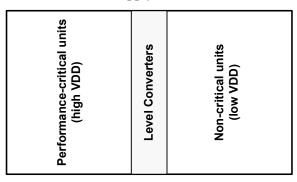

#### 2.2.2.1 Static Supply Scaling

In static supply scaling, multiple supply voltages are used as shown in Figure 2.6. Critical and non-critical paths and/or units of the design are clustered and powered by higher and lower voltages, respectively (TAKAHASHI, 1998). In an extreme case the combinational logic in a circuit can fall all way to zero when the circuit is in idle mode because it does not need to hold state, increasing the power savings. Whenever an output from a low  $V_{dd}$  unit has to drive an input of a high  $V_{dd}$  unit, a level conversion is

needed at the interface. The secondary voltages may be generated off-chip (FUSE, 2001) or regulated on-die from the core supply (CARLEY, 1999).

Figure 2.6: Two-level multiple static supply voltage scheme.

#### 2.2.2.2 Dynamic Supply Scaling

Dynamic supply scaling overrides the cost of using multiple supply voltages by adapting the single supply voltage to performance demand. When performance demand is low, supply voltage and clock frequency are lowered, delivering reduced performance with substantial power reduction (BURD, 2000).

As mentioned before, this technique gets rid of the cost of using multiple supply voltages. However, follow overheads are added when this technique is implemented:

- Circuit has to operate over a wide voltage range;

- Operating system to intelligently determine the processor speed;

- Regulator to generate the minimum voltage for specificspeed.

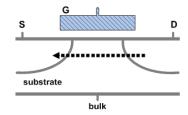

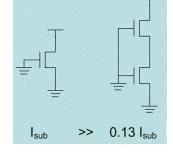

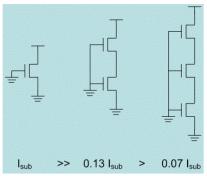

#### 2.2.3 Transistor Stack Effect

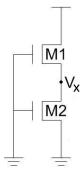

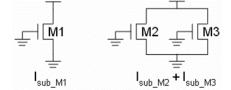

Subthreshold leakage current flowing through a stack of series-connected transistors reduces when more than one transistor in the stack is turned off. This effect is known as the "stacking effect". It is best understood by considering a two transistor stack as illustrated in figure 2.6. When both transistor M1 and M2 are turned off, the voltage at the intermediate node  $(V_X)$  is positive due to small drain current. Positive potential at the intermediate node has three effects:

- 1) Due to the positive source potential  $V_X$ , gate to source voltage of transistor M1  $(V_{gsI})$  becomes negative; hence, the subthreshold current reduces substantially.

- 2) Due to  $V_X > 0$ , body to source potential  $(V_{bsI})$  of transistor M1 becomes negative, resulting in an increase in the threshold voltage (larger body effect) of M1, and thus reducing the subthreshold leakage.

- 3) Due to  $V_X > 0$ , the drain to source potential  $(V_{dsl})$  of transistor M1 decreases, resulting in an increase in the threshold voltage (less DIBL) of M1, and thus reducing the subthreshold leakage.

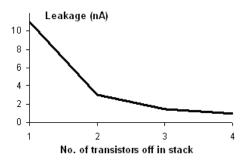

Figure 2.6: Subthreshold leakage current versus number of transistors off in stack.

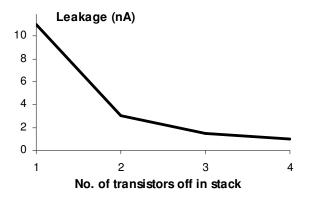

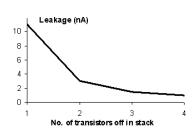

The leakage of a two-transistor stack is about an order of magnitude less than the leakage in a single transistor. Figure 2.7 shows the subthreshold leakage current versus the number of off transistor in a stack.

Figure 2.7: Subthreshold leakage current versus number of transistors off in stack.

#### 2.2.3.1 Input Vector Dependence

Functional blocks such as NAND, NOR or other complex gates readily have a stack of transistors. Due to the stacking effect, the subthreshold leakage through a logic gate depends on the applied input vector. Maximizing the number of off transistors in a natural stack by applying proper input vectors can reduce the standby leakage of a functional block. Table 2.1 presents the input vector leakage dependence in a NAND gate for a 130nm process at 100 °C.

| Input Vector | Leakage current (nA) |

|--------------|----------------------|

| 00           | 3.94                 |

| 01           | 15.25                |

| 10           | 13.65                |

4.57

11

Table 2.1: Subthreshold leakage current for 2-input NAND gate.

Standby leakage power reduction due to the minimum leakage input vector is a very effective way of controlling the subthreshold current in the standby mode of circuit operation. The most straightforward way to find a low leakage input vector is to enumerate all input's combinations. For a circuit with n inputs, there are 2n input states combinations. Due to the exponential complexity with respect to the number of inputs, such an exhaustive method is limited to circuits with a small number of primary inputs. For large circuits, a random search-based technique can be used to find the best input vector.

Gate and band-to-band tunneling leakage are also important in scaled technologies, and can be a significant portion of total leakage. The input vector control technique using a stack of transistors needs to be reinvestigated to effectively reduce the total leakage.

Researchers have shown that with high gate leakage, the traditional way of using stacked transistors fails to reduce leakage and in the worst case might increase the overall leakage (MUKHOPADHYAY, 2003). In scaled technologies where gate leakage dominates the total leakage, using "10" might produce more savings in leakage as compared to "00". The gate leakage depends on the voltage drop across the transistor gate oxide. Applying "00" as the input to a two transistors stack reduces subthreshold leakage and does not change the gate leakage component. It has been shown that using "10" reduces the voltage drop across the terminals, where the gate leakage dominates, thereby lowering the gate leakage while offering marginal improvement in subthreshold leakage (MUKHOPADHYAY, 2003).

Band-to-band tunneling leakage is a weak function of input voltage and hence can be neglect it in this analysis (AGARWAL, 2006)

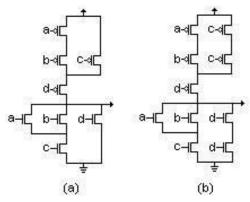

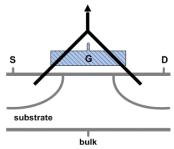

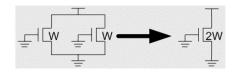

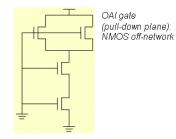

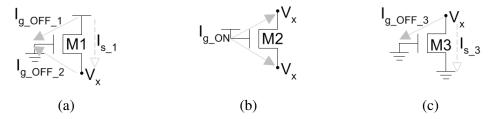

### 2.2.3.2 Stacking Single Switch

In CMOS complex gates, a certain number of transistor stacking (branches), between the supply voltage or ground nodes and the output node, can be observed. Such branches have usually different amounts of transistors. The basic idea of this technique is to duplicate transistors without increasing the longest transistor path or branch, expecting that the worst-case delay of the logic cell remains the same (BUTZEN, 2006). This procedure is applied to both pull-up (PMOS network) and pull-down (NMOS network) separately. Figure 2.8 (a) presents an original circuit and Figure 2.8 (b) illustrates the optimized circuit, resulted from the developed method described above.

Figure 2.8: Original (a) and leakage (b) optimized CMOS gate.

Stacking single switch leakage reduction methodology has been tested for ISCAS85 benchmark c8 circuit gates. The c8 circuit was optimized and synthesized using Berkeley SIS tool and mapped into library 44-6.genlib. This results in a circuit with 490 transistors mapped in 40 gates. These gates are optimizing to leakage reduction through the CAD tool described in previous section. For leakage characterization, the 65nm BSIM4 Berkeley Predictive Technology Model (BPTM, 2007) has been considered. Original and leakage optimized gates are evaluated through a DC simulation using HSPICE. The experimental results are:

In the c8 mapped circuit, the design technique modified 13 gates of the 40 total gates. Considering the area issue, the benchmark circuit had a total of 490 transistors. The design methodology duplicated 22 transistors, 4.5% of total. This represents a leakage current reduction in 32.5% of gates of circuit, increasing only 4.5% of the circuit area. The design methodology also generates a delay penalty due to the transistor duplication. This penalty was considered not so significant, about 2%. Finally, the leakage reduction in the optimized gates ranged from 7% to 22%. The average leakage reduction is around 11%.

#### 2.2.4 Power Gating

Power gating technique uses the power supply voltage as the primary source for reducing leakage current. It refers to using a MOSFET switch (sleep transistor) to cut off, or gate, a circuit from the power rails ( $V_{dd}$  and/or ground) during standby mode. The power gating switch typically is positioned as header between the circuit and the power supply or as footer between the circuit and the ground. During active operation, the power gating switch remains on, supplying the current that the circuit uses to operate. During standby mode, turning off the power gating switch reduces the current dissipated through the circuit.

Turning off the sleep transistor provides leakage reduction for two primary reasons. First, the width of the sleep transistor is usually less than total width of transistors being gated. The smaller width provides a linear reduction in the total current drawn from supply node during standby mode. Secondly, leakage currents diminish whenever stacks of transistors are off due to the source biasing effect.

During active mode, the same effects cause a degradation of circuit performance. Even though the on-resistance of the power gating switch is much less than its off-resistance, it still creates a small positive voltage at the virtual node. Again, these voltages reduce the drive capability and increase the threshold voltage of the NMOS devices through body biasing. Hence, this technique is typically used for paths that are non-critical.

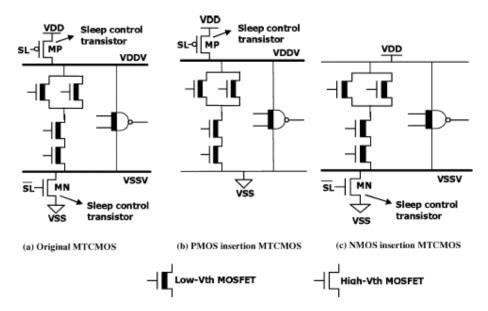

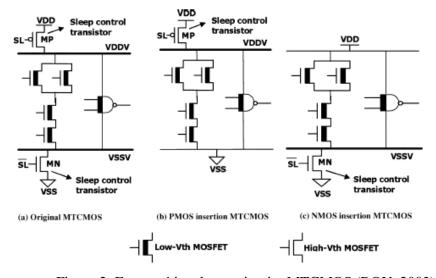

#### 2.2.4.1 MTCMOS

Multi-Threshold CMOS (MTCMOS) is a popular power gating approach that uses high  $V_{th}$  devices for power switches (MUTOH, 1995). Figure 2.9 shows the basic MTCMOS structure, where a low  $V_{th}$  computational block uses high  $V_{th}$  switches for power gating. The low  $V_{th}$  transistor in the logic gate allows them to provide a high performance operation. However, by introducing a series device to the power supplies, MTCMOS circuits incur a performance penalty compared to CMOS circuits. Subthreshold leakage reduction behavior of a MTCMOS circuit is characterized by the threshold voltage and width of sleep transistor and due to the stack effect.

In fact, only one type of high  $V_{th}$  transistor is sufficient for leakage reduction. The NMOS insertion scheme is preferable, since the NMOS on-resistance is smaller at the same width and hence it can be sized smaller than a corresponding PMOS (KAO, 1997).

However, MTCMOS can only reduce leakage power in standby mode and a large insertion of sleep transistors can increase significantly area and delay. Moreover, when data retention is required in standby mode, an extra high  $V_{th}$  memory circuit is needed to maintain the data (SHIGEMATSU, 1997).

Figure 2.9: Schematic of MTCMOS circuit (ROY, 2003).

### 2.2.5 Body Biasing

Reverse body biasing (RBB) has been used in commercial memory chips since the 1970s, in order to mitigate the risk of memory data destruction. In logic chips, on the other hand, the substrate and wells are typically biased stably to the ground and power supply. However, since the 1990s, reverse body biasing has been applied in logic chips for a different reason: power reduction.

The original propose of the substrate biasing was utilized to reduce sub-threshold leakage in standby mode for portable applications. More recently, it has been employed to reduce the maximum power dissipation by lowering  $V_{th}$  (forward body biasing) in active mode, and by compensating  $V_{th}$  variations.

### 2.2.5.1 Variable Threshold CMOS (VTCMOS)

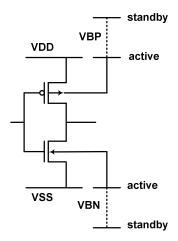

Variable threshold CMOS is a body biasing design technique (KURODA, 1996). Figure 2.10 shows the VTCMOS scheme. To achieve different threshold voltages, this scheme uses a self-substrate bias circuit to control the body bias.

Figure 2.10: Schematic of VTCMOS technique.

In the active mode, VTCMOS technique applies a zero body bias (ZBB). As the subthreshold leakage current depends strongly on threshold voltage, in standby mode, a deep reverse body bias is applied to increase the  $V_{th}$  and save leakage power. However, this reduction technique has an overhead in chip area due to additional routing required to provide the body bias voltage.

Reverse body bias can reduce circuit leakage by three orders of magnitude in a  $0.35\mu m$  CMOS technology (KESHAVARZI, 2001). However, more recent data shows that the effectiveness of RBB to lower  $I_{off}$  decreases as technology scales due to the exponential increase in band-to-band tunneling leakage at the source/substrate and drain/substrate pn junctions (KESHAVARZI, 2001). Moreover, smaller channel length with technology scaling and lower channel doping (to reduce  $V_{th}$ ) worsen the short channel effect and diminish the body effect. This, in turns, weakens the  $V_{th}$  modulation capability of RBB.

For scaled technologies, recent design has been proposed using forward body biasing (FBB) to achieve better current drive with less short channel effect (NARENDRA, 2003). Circuit is designed using high  $V_{th}$  transistor (high channel doping) reducing leakage in standby mode, while FBB is applied in active mode to achieve high performance. Both high channel doping and FBB reduce short channel effect relaxing the scalability limit of channel length due to  $V_{th}$  roll off and DIBL. This result in higher  $I_{on}$  compared to low  $V_{th}$  design for same  $I_{off}$  worst case, improving performance. RBB can also be applied in standby mode together with FBB to further reduce the leakage current.

It has been shown that FBB and  $high-V_{th}$  along with RBB reduces leakage by 20X, as opposed to 3X for the RBB and  $low-V_{th}$  (NARENDRA, 2003). However, FBB devices has larger junction capacitance and body effect, which reduces the delay improvement mainly in stacked circuits.

#### 2.2.5.2 Dynamic Vth Scaling

Not every application requires a fast circuit to operate at the highest performance level all the time. Active leakage techniques exploit this idea to intermittently slow down the fast circuitry and reduce the leakage power consumption as well as the dynamic power consumption when maximum performance is not required.

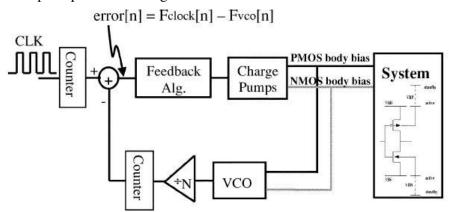

Dynamic  $V_{th}$  scaling (DVTS) scheme uses body biasing to adjust  $V_{th}$  based on the performance demand. (KIM, 2002) This technique uses the same concept of variable threshold CMOS (VTCMOS). While VTCMOS change  $V_{th}$  based on active and standby mode, DVTS modifies the  $V_{th}$  based on circuit performance demand, i.e., during active mode the threshold voltage can be changed depending on the system performance requirement.

The lowest  $V_{th}$  is delivered via zero body bias, if highest performance is required. When performance demand is low, clock frequency is lowered and  $V_{th}$  is raised via reverse body bias to reduce the run-time leakage power dissipation. In cases when there is no workload at all, the  $V_{th}$  can be increased to its upper limit to significantly reduce the standby leakage power. This scheme deliveries just enough throughput for the current workload by tracking the optimal  $V_{th}$ . It is considerably reduces leakage power by intermittently lowing down the circuit. A block diagram of the DVTS scheme and its feedback loop are presented in Figure 2.11.

Figure 2.11: Schematic of DVTS hardware (KIM, 2002).

## 3 SUBTHRESHOLD LEAKAGE MODEL

This chapter reviews subthreshold leakage current models. A simplified model based on conductance association in series-parallel CMOS gates is demonstrated. Moreover, an improved analytical model based on physical parameters is proposed to general networks. It takes into account both drain induced barrier lowering (DIBL) and body effect, and can evaluate any complex gate. All analysis presented in this chapter use NMOS pull-down network. The same analysis is applicable to PMOS pull-up tree. First of all, the simple and straightforward method to fast subthreshold leakage prediction is presented. Next, three analytical subthreshold leakage models reported in the literature are discussed, and then, a detailed and complete analytical model for complex gates is described. Finally, at the end of the chapter, HSPICE simulations are used to validate the improved analytical model and to verify its accuracy.

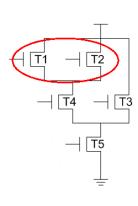

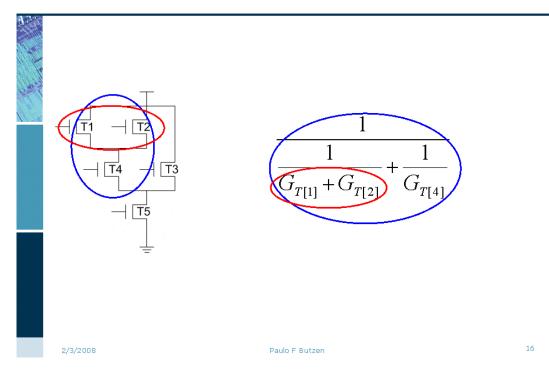

#### 3.1 Estimation Based on Conductance Association

The main objective of this simple method is to provide a normalized current value, related to a reference MOS off-switch, in order to use it as leakage cost of logic networks in technology mapping. It means the relative leakage prediction comparison and ordering of different off-networks is more important than the accuracy improvement in estimating the absolute leakage current values. Making so, the matching task during the mapping is able to take into account, among other design metrics, the static consumption of the logic gates identified in this process. It is crucial in library-free technology mapping (GAVRILOV,1997), where cells are not precharacterized but automatically generated by software on-the-fly during the logic matching, in the concept of using virtual libraries in ASIC design.

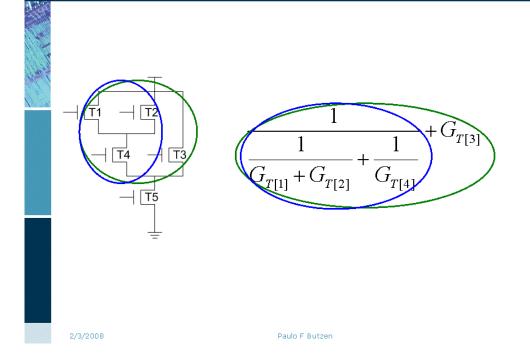

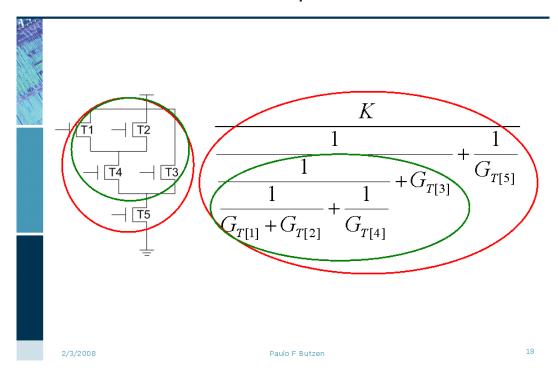

Proposed method is based on the device electrical conductance association, that is, the conduction of parallel devices are summed while in series arrangements the equivalent conductance is inversely proportional to the number of devices. Being  $G_{T[n]}$  the conductance of the n-index transistor in the arrangement, the equivalent conductance  $G_{eq}$  of parallel and series arrangements are given by:

- Parallel  $G_{eq} = G_{T[1]} + G_{T[2]} + ... + G_{T[n]}$

- Series  $Geq = 1/(1/G_{T(1)} + 1/G_{T(2)} + ... + 1/G_{T(n)})$

At this moment, all transistors will be considered with equal size, and thus the individual device conductance  $G_{T[i]}$  can be made unitary, normalized in respect to a reference transistor.

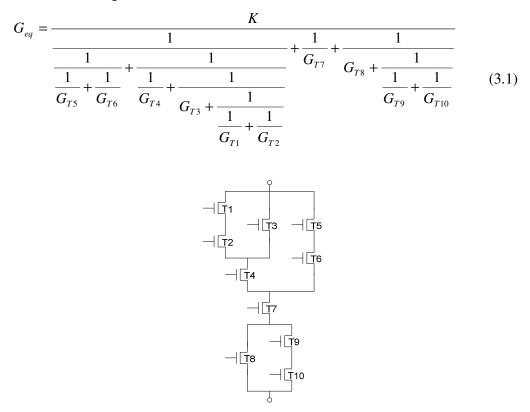

In more complex arrangements, the same principle is suitable for parallel and series associations. To exemplify this method, the transistor network illustrated in Figure 3.1 presents the following calculation:

Figure 3.1: Transistor network with multi-level of series-parallel associations.

In the case of series transistor, the leakage reduction from a single off-device to two stacked off-transistors depends also on the fabrication process parameters (GU, 1996). As a result, a constant K must be included in the last step of the calculation procedure in order to calibrate the final result. This K value is obtained by relating the leakage current of two-stack and single off-device configurations. In this sense, two constants  $K_n$  and  $K_p$  may be derived according to NMOS and PMOS arrangements, respectively.

Furthermore, since NMOS and PMOS transistors present different subthreshold current behavior, such difference may be characterized to include in the same calculation both pull-up PMOS and pull-down NMOS planes in CMOS gates. Such relationship is represented by the constant  $K_{pn}$ .

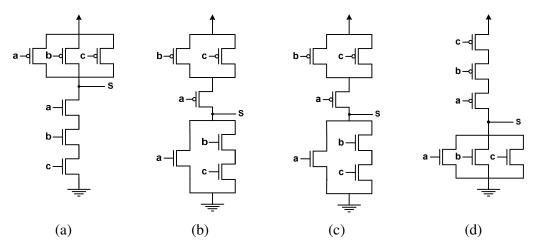

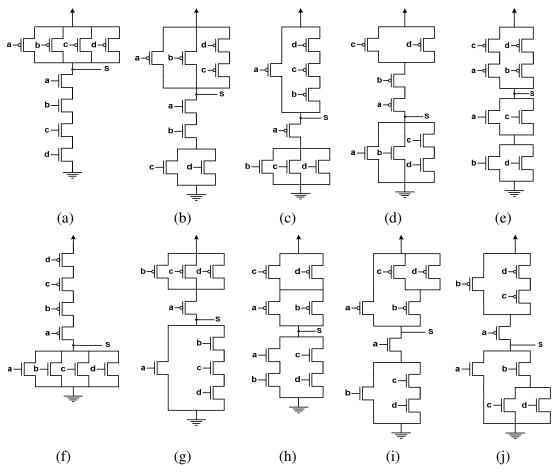

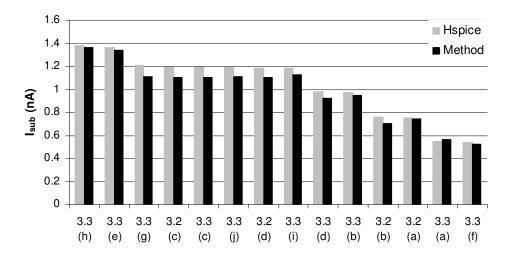

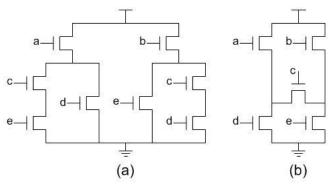

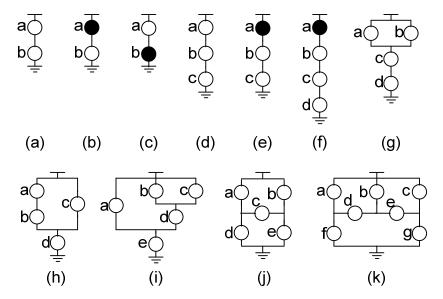

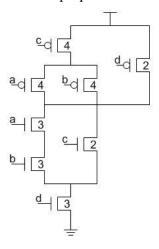

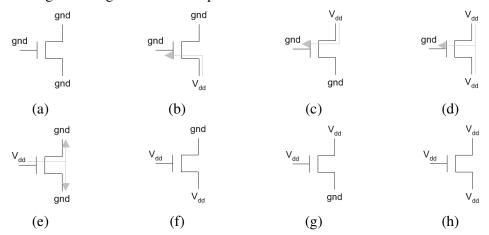

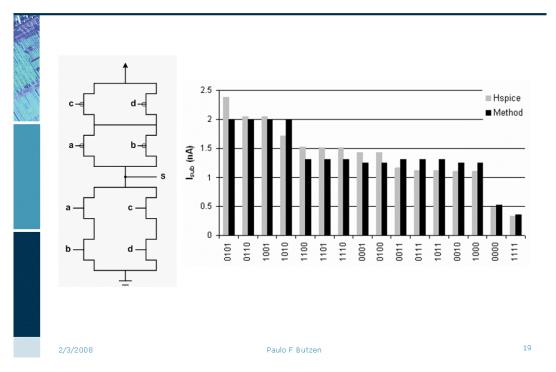

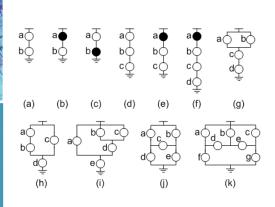

Different CMOS logic gates were evaluated for all input signals combinations, resulting thus in a great variety of off-networks for subthreshold leakage estimation. These CMOS arrangements are shown in Figure 3.2 and Figure 3.3.

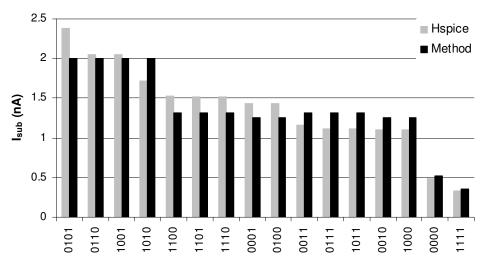

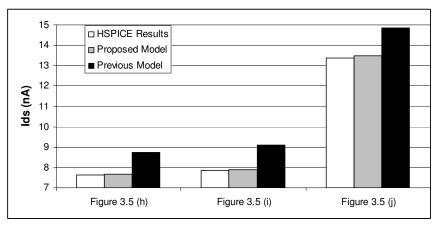

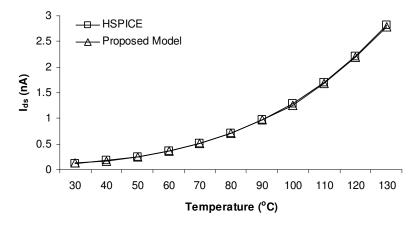

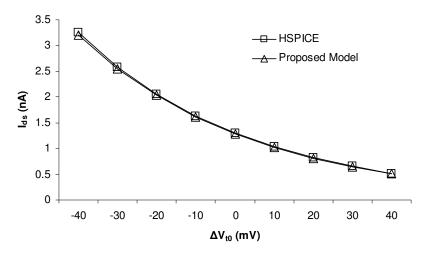

Table 3.1 and Figure 3.4 show results of the CMOS gates depicted in Fig. 3.3 (h), for each input vector. Note that the main goal of this simple method is to identify the less leakage consuming input vector, as well as to compare different CMOS arrangements in order to guide the technology mapping task in terms of static power dissipation. It also can be observed in Table 3.2 and Figure 3.5, where the worst-case and the average current values are given for the cells presented in Figure 3.2 and Figure 3.3.

Figure 3.2: Different transistor arrangements: 3-inputs series-parallel CMOS gates.

Figure 3.3: Different transistor arrangements: 4-inputs series-parallel CMOS gates.

Table 3.1: Normalized subthreshold leakage current in Figure 3.3 (h)

| Input Vector | Hspice<br>Simulation | Proposed<br>Method | Diff (%) |

|--------------|----------------------|--------------------|----------|

| 0000         | 0.49                 | 0.52               | 6.12     |

| 0001         | 1.43                 | 1.26               | 11.89    |

| 0010         | 1.10                 | 1.26               | 14.55    |

| 0011         | 1.16                 | 1.32               | 13.79    |

| 0100         | 1.43                 | 1.26               | 11.89    |

| 0101         | 2.38                 | 2.00               | 15.97    |

| 0110         | 2.05                 | 2.00               | 2.44     |

| 0111         | 1.11                 | 1.32               | 18.92    |

| 1000         | 1.10                 | 1.26               | 14.55    |

| 1001         | 2.05                 | 2.00               | 2.44     |

| 1010         | 1.72                 | 2.00               | 16.28    |

| 1011         | 1.11                 | 1.32               | 18.92    |

| 1100         | 1.53                 | 1.32               | 13.73    |

| 1101         | 1.52                 | 1.32               | 13.16    |

| 1110         | 1.52                 | 1.32               | 13.16    |

| 1111         | 0.33                 | 0.36               | 9.09     |

Figure 3.4: Subthreshold leakage currents in CMOS structure from Figure 3.3 (h), for each input vector.

Table 3.2: Correlation between empirical method and HSPICE for the worst-case and average leakage normalized values of different CMOS structures from Figure 3.2 and Figure 3.3

|         | Worst Case Leakage   |                    | Average Leakage      |                    |

|---------|----------------------|--------------------|----------------------|--------------------|

|         | Hspice<br>Simulation | Proposed<br>Method | Hspice<br>Simulation | Proposed<br>Method |

| 3.2 (a) | 2.29                 | 1.98               | 0.75                 | 0.74               |

| 3.2 (b) | 3.58                 | 3.00               | 0.76                 | 0.70               |

| 3.2 (c) | 2.38                 | 2.00               | 1.19                 | 1.10               |

| 3.2 (d) | 1.65                 | 2.00               | 1.18                 | 1.10               |

| 3.3 (a) | 3.05                 | 2.64               | 0.55                 | 0.56               |

| 3.3 (b) | 2.29                 | 2.00               | 0.97                 | 0.95               |

| 3.3 (c) | 2.41                 | 3.00               | 1.19                 | 1.10               |

| 3.3 (d) | 3.57                 | 3.00               | 0.98                 | 0.92               |

| 3.3 (e) | 2.38                 | 2.00               | 1.36                 | 1.34               |

| 3.3 (f) | 4.76                 | 4.00               | 0.54                 | 0.52               |

| 3.3 (g) | 2.38                 | 2.00               | 1.21                 | 1.11               |

| 3.3 (h) | 2.38                 | 2.00               | 1.38                 | 1.36               |

| 3.3 (i) | 1.88                 | 2.00               | 1.18                 | 1.13               |

| 3.3 (j) | 2.84                 | 3.00               | 1.19                 | 1.11               |

Figure 3.5: Average subthreshold leakage current in the different CMOS structures from Figure 3.2 and Figure 3.3.

#### 3.2 Subthreshold Leakage Models

Several subthreshold leakage current models have been presented during the last decade. This work evaluates three of these models, presented by (NARENDRA, 2006), (GU, 1996) and (ROY, 2000). A brief analysis for a two transistor stack is presented for each model, as well as their advantages and limitations are reported. Based on this initial analysis, the model presented by (ROY, 2000) was selected to be reviewed and improved in order to evaluate CMOS complex gates.

#### 3.2.1 (NARENDRA, 2006) Model

Subthreshold leakage current model reported by (NARENDRA, 2006) is given by:

$$I_{s} = W.I_{1}.10^{\frac{-1}{n} \left[\Delta V_{gs} + \eta \Delta V_{ds} + \gamma \Delta V_{bs}\right]}$$

(3.2)

where W is the effective transistor width,  $I_1$  is the leakage of a single transistor of unit width in an OFF state with  $V_{gs} = V_{bs} = 0$  V and  $V_{ds} = V_{dd}$ .  $\Delta V_{gs}$ ,  $\Delta V_{bs}$  and  $\Delta V_{ds}$  are respectively the gate-drive, body bias and drain-to-source voltage reduced based on above mentioned conditions. n is the subthreshold swing,  $\eta$  is the drain-induced barrier lowering and  $\gamma$  is the body effect coefficient. The above equation assumes that the resulting  $V_{ds} > 3kT/q$ .

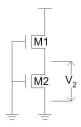

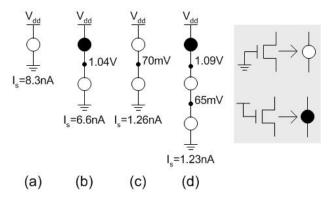

In a two-transistor stack, as shown in Figure 3.6, the subthreshold leakage currents passing through the transistors is given by

$$I_{SM1} = W_1 I_1 . 10^{\frac{-V_2(1+\eta+\gamma)}{n}}$$

(3.3)

$$I_{SM1} = W_1 I_1 .10^{\frac{-V_2(1+\eta+\gamma)}{n}}$$

$$I_{SM2} = W_2 I_1 .10^{\frac{-\eta(V_{dd}-V_2)}{n}}$$

(3.3)

Figure 3.6: Two-transistor stack.

This two-transistor stack reaches its steady state condition when the leakage current in the upper and lower transistors are equal. Under this condition, the voltage V<sub>2</sub> can be expressed as

$$V_2 = \frac{\eta V_{dd} + n \log\left(\frac{W_1}{W_2}\right)}{1 + 2\eta + \gamma}$$

(3.5)

In order to confirm the model accuracy, HSPICE simulations were performed in 0.13μm CMOS process and compared to the theoretical results. The model parameters, n=1.45,  $\eta=0.078$  and  $\gamma=0.17$  are extracted by simulation by using  $V_{dd}=1.2V$ ,

temperature=100°C, minimum transistor width and channel length. Table 3.3 shows the numerical results and proves the accuracy of the theoretical model.

Although the model presents satisfactory accuracy, it is essential to point out that the model assumes the intermediate node voltage to be greater than 3kT/q. This assumption invalidates the model when it is applied to three or more transistor stacks because occasionally the intermediate node voltage is not greater than 3kT/q. This will be showed later.

#### 3.2.2 (GU, 1996) Model

Subthreshold leakage current model reported by (GU, 1996) is given by:

$$I_{S} = I_{0}We^{\frac{V_{gs} - V_{th}}{nV_{T}}} \left[ 1 - e^{\frac{-V_{ds}}{V_{T}}} \right]$$

(3.6)

where  $I_0 = \frac{\mu_0 C_{ox} V_T^2 e^{1.8}}{L}$ ,  $V_T = \frac{kT}{q}$ , W is the effective transistor width, L is the effective

channel length, n is the subthreshold slope coefficient,  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the mobility, and  $V_{th}$  is the threshold voltage expressed by equation (3.7).

$$V_{th} = V_{FB} + \Phi_S + K_1 \sqrt{\Phi_S - V_{bs}} - K_2 (\Phi_S - V_{bs}) - \eta V_{ds}$$

(3.7)

where  $V_{FB}$  is the flat-band voltage,  $\Phi_S$  is the surface-inversion potential,  $K_1$  and  $K_2$  together model the body effect phenomenon, and  $\eta$  is the drain-induced barrier lowering coefficient.

In a two-transistor stack the subthreshold leakage currents passing through the transistors is given by

$$I_{SM1} = I_0 W_1 e^{\frac{V_{FB} + \phi_s - K_1 \sqrt{\phi_s} + K_2 \phi_s}{nV_T}} e^{\frac{\eta V_{dd} - (1 + k_2 - \eta)V_2 - K_1 \sqrt{V_2}}{nV_T}}$$

(3.8)

$$I_{SM2} = I_0 W_2 e^{\frac{V_{FB} + \phi_S - K_1 \sqrt{\phi_S} + K_2 \phi_S}{nV_T}} e^{\frac{\eta V_2}{nV_T}}$$

(3.9)

In order to simplify the analysis, the voltages  $V_{dsI} = V_{dd} - V_2$  and  $V_{ds2} = V_2$  were considered greater than 3kT/q in equations (3.8) and (3.9). This assumption is true as verified in Table 3.3. The intermediate node voltage,  $V_2$ , can be derived by equating the two currents.

$$V_{2} = \frac{\eta V_{dd} + nV_{T} \ln\left(\frac{W_{1}}{W_{2}}\right)}{1 + \frac{K_{1}}{2\sqrt{\Phi_{S}}} - K_{2} + 2\eta}$$

(3.10)

This theoretical model was compared to HSPICE simulation to confirm the model accuracy. The model parameters  $K_1 = 0.7$ ,  $K_2 = 0.15$  and  $\Phi_S = 0.9$  were extracted from

transistor model while n = 1.45 and  $\eta = 0.078$  were achieved through electrical simulation. Model presents good accuracy and the results are showed in Table 3.3.

Despite used in previous example, this model does not have the restriction mentioned in (NARENDRA, 2006) model and can evaluate gates where the intermediate voltage is smaller than 3kT/q. However, the  $V_{th}$  definition is based on physical parameters which are not common to circuit designers.

#### 3.2.3 (ROY, 2000) Model

Subthreshold leakage current model reported by (ROY, 2000) is given by:

$$I_{S} = I_{0}We^{\frac{V_{gs} - (V_{t0} - \eta V_{ds} - W_{bs})}{nV_{T}}} \left[ 1 - e^{\frac{-V_{ds}}{V_{T}}} \right]$$

(3.11)

where  $I_0 = \frac{\mu_0 C_{ox} V_T^2 e^{1.8}}{L}$ ,  $V_T = \frac{kT}{a}$ ,  $V_{t0}$  is the zero-bias threshold voltage, W is the effective

transistor width, L is the effective channel length, n is the subthreshold slope coefficient,  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the mobility,  $\eta$  is the drain-induced barrier lowering coefficient and  $\gamma$  is the linearized body effect coefficient.

In a two-transistor stack the subthreshold leakage currents passing through the transistors is given by

$$I_{SM1} = I_0 W_1 e^{\frac{-V_2 - [V_{t0} - \eta(V_{dd} - V_2) + W_2]}{nV_T}}$$

$$I_{SM2} = I_0 W_2 e^{\frac{-V_{t0} + \eta V_2}{nV_T}}$$

(3.12)

$$I_{SM2} = I_0 W_2 e^{\frac{-V_{t0} + \eta V_2}{nV_T}}$$

(3.13)

and the intermediate node voltage  $V_2$  is expressed as

$$V_2 = \frac{\eta V_{dd} + nV_T \ln\left(\frac{W_1}{W_2}\right)}{1 + 2\eta + \gamma}$$

(3.14)

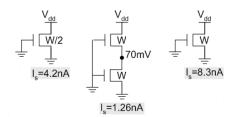

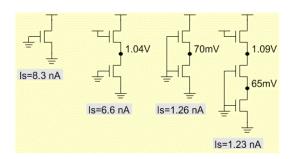

Table 3.3 lists the theoretical model estimation values for the previous example. Its accuracy is verified when compared to HSPICE simulation. The model parameters n=1.45,  $\eta=0.078$ , and  $\gamma=0.17$  were extracted from simulation.

|             | HSPICE<br>Simulation | (NARENDRA, 2006) model | (GU, 1996)<br>Model | (ROY, 2000)<br>Model |

|-------------|----------------------|------------------------|---------------------|----------------------|

| $V_2 (mV)$  | 69.99                | 70.59                  | 68.08               | 70.59                |

| $I_{S}(nA)$ | 1.26                 | 1.21                   | 1.25                | 1.26                 |

Table 3.3: Proposed models accuracy for two stacked transistors

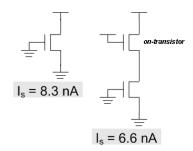

In spite of the three previously presented models having good accuracy compared to HSPICE simulation, there are several restrictions. The model presented by (NARENDRA, 2006) cannot be used in three stacked transistors or in any gate where  $V_{ds}$  cannot be considered greater than 3kT/q. All those models do not present a solution for complex gates as the cell example in Figure 3.2. Additionally, none of the models consider the effect of ON-transistor in OFF-networks.

The model developed in this work evaluates all restrictions previously mentioned. The model presented by (ROY, 2000) is used as a reference because it shows the most familiar equation to circuit designers. In the next session, a detailed and complete model to CMOS complex gates is presented.

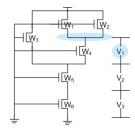

#### 3.3 Modeling Subthreshold Leakage in CMOS Logic Gates

Standard CMOS logic gates are composed of series-parallel transistor networks. As mentioned previously, the total leakage dissipation results from the sum of the current in each branch of off-transistors between the supply voltage and ground node. To present the proposed method, the off-network illustrated in Figure 3.7 can be considered as the entire NMOS pull-down arrangement, or a branch from a more complex CMOS gate. The same analysis is applicable to a PMOS pull-up tree.

From the BSIM MOS transistor model (SHEU, 1987), the subthreshold current for a MOSFET device can be modeled as

$$I_{S} = I_{0}We^{\frac{V_{gs} - (V_{r0} - \eta V_{ds} - W_{bs})}{nV_{T}}} \left[ 1 - e^{\frac{-V_{ds}}{V_{T}}} \right]$$

(3.15)

where  $I_0 = \frac{\mu_0 C_{ox} V_T^2 e^{1.8}}{L}$  and  $V_T = \frac{kT}{q}$ .  $V_{gs}$ ,  $V_{ds}$  and  $V_{bs}$  are the gate, drain and bulk voltage of

the transistor, respectively.  $V_{t0}$  is the zero bias threshold voltage. W and L are the effective transistor width and length, respectively.  $\gamma$  is the body effect coefficient and  $\eta$  is the DIBL coefficient.  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the mobility and n is the subthreshold slope coefficient.

Figure 3.7: NMOS series-parallel network.

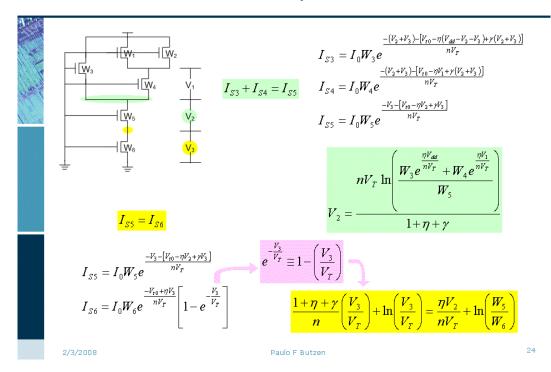

In Figure 3.7, the currents passing through the transistors is given by

$$I_{S1} = I_0 W_1 e^{\frac{-(V_1 + V_2 + V_3) - [V_{t0} - \eta(V_{dd} - V_1 - V_2 - V_3) + \gamma(V_1 + V_2 + V_3)]}{nV_T}}$$

(3.16)

$$I_{S2} = I_0 W_2 e^{\frac{-(V_1 + V_2 + V_3) - [V_{r0} - \eta(V_{dd} - V_1 - V_2 - V_3) + \gamma(V_1 + V_2 + V_3)]}{nV_T}}$$

(3.17)

$$I_{S3} = I_0 W_3 e^{\frac{-(V_2 + V_3) - [V_{r_0} - \eta(V_{dd} - V_2 - V_3) + \gamma(V_2 + V_3)]}{nV_T}}$$

(3.18)

$$I_{S4} = I_0 W_4 e^{\frac{-(V_2 + V_3) - [V_{t_0} - \eta V_1 + \gamma (V_2 + V_3)]}{nV_T}}$$

(3.19)

$$I_{S5} = I_0 W_5 e^{\frac{-V_3 - [V_{t0} - \eta V_2 + W_3]}{nV_T}}$$

(3.20)

$$I_{S6} = I_0 W_6 e^{\frac{-V_{r_0} + \eta V_3}{nV_T}} \left[ 1 - e^{\frac{-V_3}{V_T}} \right]$$

(3.21)

The following derivation assumes that  $V_I >> V_T$  and  $V_2 >> V_T$ , which was confirmed through Hspice simulation. Thus, the term  $[1 - e(-V_{ds}/V_T)]$  in equations (3.16), (3.17), (3.18), (3.19) and (3.20) has been ignored.

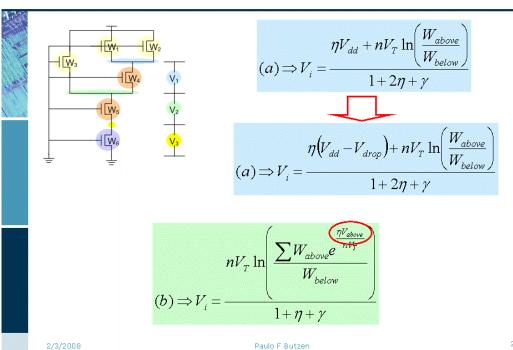

First of all, the currents across the first, the second and the fourth transistors are equalized. By solving the equation  $I_{S1} + I_{S2} = I_{S4}$ , then  $V_I$  is given by

$$V_{1} = \frac{\eta V_{dd} + nV_{T} \ln \left( \frac{W_{1} + W_{2}}{W_{4}} \right)}{1 + 2\eta + \gamma}$$

(3.22)

In next step,  $V_2$  value is obtained by solving the equation  $I_{S3} + I_{S4} = I_{S5}$ .  $V_2$  is given by

$$nV_{T} \ln \left( \frac{W_{3}e^{\frac{\eta V_{dd}}{nV_{T}}} + W_{4}e^{\frac{\eta V_{1}}{nV_{T}}}}{W_{5}} \right)$$

$$V_{2} = \frac{1 + \eta + \gamma}{1 + \eta + \gamma}$$

(3.23)

It is also assumed  $V_3 < V_T$ . As a consequence, the term  $e(-V_3/V_T)$  in (3.21) can be expressed as  $(I - V_3/V_T)$ . Introducing this assumption and making  $I_{S5} = I_{S6}$ ,  $V_3$  is then expressed by follow equation, which is accurately solved after some iteration,

$$\frac{1+\eta+\gamma}{n}\left(\frac{V_3}{V_T}\right) + \ln\left(\frac{V_3}{V_T}\right) = \frac{\eta V_2}{nV_T} + \ln\left(\frac{W_5}{W_6}\right)$$

(3.24)

#### 3.3.1 General subthreshold leakage model