## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

FELIPE DE SOUZA MARQUES

### Technology Mapping for Virtual Libraries Based on Cells with Minimal Transistor Stacks

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Dr. André Inácio Reis Advisor

Porto Alegre, March 2008.

# Livros Grátis

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Marques, Felipe de Souza

Technology Mapping for Virtual Libraries Based on Cells with Minimal Transistor Stacks / Felipe de Souza Marques – Porto Alegre: Programa de Pós-Graduação em Computação, 2008.

Tese (doutorado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2008. Advisor: André Inácio Reis.

1. Mapeamento Tecnológico 2 Síntese Lógica 3 Bibliotecas de Células 4 Bibliotecas Células Virtuais 5 Geradores de Células. I. Reis, André Inácio. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. José Carlos Ferraz Hennemann Vice-Reitor: Prof. Pedro Cezar Dutra Fonseca Pró-Reitora de Pós-Graduação: Profa. Valquiria Linck Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenadora do PPGC: Prof<sup>a</sup> Luciana Porcher Nedel Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## ACKNOWLEDGMENTS

Primeiramente, gostaria de agradecer as pessoas que estiveram diretamente envolvidas no desenvolvimento do meu trabalho de tese. Meu orientador, prof. André Reis, com quem trabalhei desde o mestrado e sempre trouxe grandes contribuições para a realização deste trabalho. Ao prof. Renato Ribas, que apesar de não ser oficialmente co-orientator deste trabalho, atuou como tal e esteve sempre disposto a ajudar no que foi preciso. Quero estender este agradecimento ao colega Leomar Soares da Rosa Junior que também teve uma importante contribuição e que sempre esteve disposto a conversar, seja sobre trabalho, seja sobre questões pessoais. Eu gostaria de agradecer do mesmo modo a todos os colegas com quem eu trabalhei no laboratório da Nangate, em especial ao Pedro e ao Erasmo, pelos esforços para a realização de experimentos.

Também gostaria de agradecer a minha família, meus pais, Sandra e Rogério Marques, e meus irmãos Rodrigo, Diego e Letícia, pois o apoio e carinho deles foram sempre muito importantes em todas as minhas conquistas. Não poderia deixar de agradecer uma pessoa que é fundamental na minha vida, minha esposa, Milena Rota Sena Marques, por todo o companheirismo, compreensão e amor que me deram forças para vencer mais um desafio, além da paciência para agüentar todos os dias de mau humor. Agradeço aos amigos, pelas cervejas, churrascos e conversas, que certamente ajudaram a espairecer nos momentos mais estressantes do doutorado.

É importante também agradecer ao CNPq pela bolsa de doutorado, que, através do Programa Nacional de Microeletrônica, me possibilitou dedicação exclusiva a minha formação acadêmica. A CAPES, agradeço a bolsa de estágio no exterior, que me permitiu colaborar com um excelente laboratório de pesquisa na Universidade de Minnesota, nos Estados Unidos, e ter uma experiência muito relevante para minha formação. Em especial, agradeço ao prof. Sachin Sapatnekar, por ter me dado à oportunidade de trabalhar em seu grupo de pesquisa (Thank you!).

## **TABLE OF CONTENTS**

| LIST  | OF ABBREVIATIONS7                                               |

|-------|-----------------------------------------------------------------|

| LIST  | OF FIGURES                                                      |

| LIST  | OF TABLES 12                                                    |

| ABST  | <sup>•</sup> RACT 13                                            |

| RESU  | JMO14                                                           |

| 1     | INTRODUCTION 15                                                 |

| 1.1   | Motivation and thesis contributions17                           |

| 1.2   | Thesis organization17                                           |

| 2     | TERMINOLOGY AND BASIC CONCEPTS 18                               |

| 2.1   | Boolean logic and logic expressions18                           |

| 2.2   | Logic styles of transistor networks 21                          |

| 2.3   | Minimal length for transistor stacks in standard cell libraries |

| 2.4   | Digital circuits representation 25                              |

| 3     | TECHNOLOGY MAPPING 27                                           |

| 3.1   | Cell libraries                                                  |

| 3.2   | Subject graphs                                                  |

| 3.3   | Conventional technology mapping 33                              |

| 3.3.1 | Graph partitioning 34                                           |

| 3.3.2 | Technology decomposition                                        |

| 3.3.3 | Matching phase                                                  |

| 3.3.4 | Covering phase                                                  |

| 3.4   | Technology mapping for standard cell libraries 3                                         | <b>3</b> 7 |  |  |  |  |

|-------|------------------------------------------------------------------------------------------|------------|--|--|--|--|

| 3.4.1 | Keutzer (1987-a) – DAGON                                                                 | 38         |  |  |  |  |

| 3.4.2 | Kukimoto (1998) – DAG based technology mapping 40                                        |            |  |  |  |  |

| 3.4.3 | Stok (1999) – Wavefront technology mapping 41                                            |            |  |  |  |  |

| 3.4.4 | Mishchenko (2005) – Technology Mapping with Boolean Matching, Supergate<br>and Choices   |            |  |  |  |  |

| 3.5   | Technology mapping for virtual libraries4                                                | 15         |  |  |  |  |

| 3.5.1 | Berkelaar (1988) – The first technology mapping algorithm for ce generators              |            |  |  |  |  |

| 3.5.2 | Reis (1998) – TABA 4                                                                     | 16         |  |  |  |  |

| 3.5.3 | Jiang (2001) – OTR: PTL / CMOS technology mapping                                        | 17         |  |  |  |  |

| 3.5.4 | Correia (2004) – ELIS - Technology mapping for symmetric and asymmetry virtual libraries |            |  |  |  |  |

| 3.6   | Technology mapping methods overview5                                                     | 52         |  |  |  |  |

| 4     | TECHNOLOGY MAPPING USING CMOS GATES WITH MINIMUM<br>TRANSISTOR STACKS                    |            |  |  |  |  |

| 4.1   | Previous technology mapping techniques and CMOS gates with minimum transistor stacks     |            |  |  |  |  |

| 4.1.1 | Cell instances                                                                           | 53         |  |  |  |  |

| 4.1.2 | Tree based and DAG based technology mapping techniques                                   | 55         |  |  |  |  |

| 4.1.3 | The computation of series transistors                                                    | 55         |  |  |  |  |

| 4.1.4 | Contextualizing the problem                                                              | 57         |  |  |  |  |

| 4.2   | VIRMA technology mapping tool5                                                           | 57         |  |  |  |  |

| 4.2.1 | Defining the object function                                                             | 57         |  |  |  |  |

| 4.2.2 | Pre-processing procedures                                                                | 58         |  |  |  |  |

| 4.2.3 | Post-processing procedures                                                               | 50         |  |  |  |  |

| 4.2.4 | VIRMA wavefront technology mapping6                                                      | 50         |  |  |  |  |

| 4.2.5 | VIRMA and k-cuts6                                                                        | 55         |  |  |  |  |

| 4.3   | Final considerations                                                                     | 57         |  |  |  |  |

| 5   | EXPERIMENTS                                    | . 69 |

|-----|------------------------------------------------|------|

| 5.1 | Comparisons between SIS and VIRMA-WF           | . 69 |

| 5.2 | Comparisons between ABC and VIRMA              | . 74 |

| 5.3 | Comparisons between commercial tools and VIRMA | . 76 |

| 6   | CONCLUSIONS AND FUTURE WORKS                   | . 82 |

## LIST OF ABBREVIATIONS

| ABC   | A System for Sequential Synthesis and Verification |  |  |  |

|-------|----------------------------------------------------|--|--|--|

| AIG   | AND-Inverter Graph                                 |  |  |  |

| AND   | AND Boolean operator                               |  |  |  |

| AOI   | AND-OR-Inverter Boolean operator                   |  |  |  |

| BDD   | Binary Decision Diagram                            |  |  |  |

| LC    | Logic Cones                                        |  |  |  |

| CMOS  | Complementary Metal Oxide Semiconductor            |  |  |  |

| CPU   | Central Processing Unit                            |  |  |  |

| CSP   | Complementary Series/Parallel                      |  |  |  |

| DAG   | Directed Acyclic Graph                             |  |  |  |

| EDA   | Electronic Design Automation                       |  |  |  |

| FPGA  | Field Programmable Gate Array                      |  |  |  |

| GND   | Ground drain                                       |  |  |  |

| HDL   | Hardware Description Language                      |  |  |  |

| IC    | Integrated Circuit                                 |  |  |  |

| ISCAS | International Symposium on Circuits and Systems    |  |  |  |

| LLWF  | Library-less Wavefront                             |  |  |  |

| LUT   | Lookup Table                                       |  |  |  |

| NAND  | Inverted AND Boolean operator                      |  |  |  |

| NCSP  | Non-Complementary Series/Parallel                  |  |  |  |

| NMOS  | N-type Metal Oxide Semiconductor                   |  |  |  |

| NOR   | Inverted OR Boolean operator                       |  |  |  |

| NOT   | Inversion Boolean operator                         |  |  |  |

| NP    | Algorithm complexity class                         |  |  |  |

| OR    | OR Boolean operator                                |  |  |  |

| OTR   | Odd-level Transistor Replacement                   |  |  |  |

| PC    | Personal Computer                                  |  |  |  |

| PD    | Maximum number of stacked transistors in the pull-down plane     |

|-------|------------------------------------------------------------------|

| PI    | Primary Input                                                    |

| PMOS  | P-type Metal Oxide Semiconductor                                 |

| PO    | Primary Output                                                   |

| POS   | Product of Sums                                                  |

| PTL   | Pass Transistor Logic                                            |

| PU    | Maximum number of stacked transistors in the pull-up plane       |

| ROBDD | Reduced Ordered Binary Decision Diagram                          |

| RTL   | Register Transfer Language                                       |

| SIS   | Sequential Interactive System                                    |

| SOP   | Sum of Products                                                  |

| SPD   | Sum of PDs in a path                                             |

| SPICE | General-Purpose Circuit Simulation Program                       |

| SPU   | Sumo f PUs in a path                                             |

| STA   | Static Timing Analysis                                           |

| TABA  | Tool for Library Free Technology Mapping                         |

| TSBDD | Terminal-Suppressed Binary Decision Diagram                      |

| VDD   | Power supply voltage                                             |

| VHDL  | Very High Speed Integrated Circuit Hardware Description Language |

| VIRMA | Virtual technology mapping tool                                  |

| VLSI  | Very Large Scale Integration                                     |

| XNOR  | Inverted XOR Boolean operator                                    |

| XOR   | XOR Boolean operator                                             |

|       |                                                                  |

## LIST OF FIGURES

| Figure 2.1: Truth table for the function f and their respective minterms 1 | 19 |

|----------------------------------------------------------------------------|----|

| Figure 2.2: Karnaugh map for the Boolean function f 2                      | 20 |

| Figure 2.3: Multilevel representations 2                                   | 20 |

| Figure 2.4: Correspondence among BDD nodes and multiplexers                | 21 |

| Figure 2.5: PTL transistor network derived from a BDD 2                    | 22 |

| Figure 2.6: Path sensitization in a PTL network 2                          | 22 |

| Figure 2.7: CSP CMOS transistor networks for f 2                           | 23 |

| Figure 2.8: NCSP cell for the Boolean function f 2                         | 24 |

| Figure 2.9: Simulation table of the NCSP cell                              | 25 |

| Figure 2.10: Combinational circuit representations 2                       | 26 |

| Figure 3.1: Digital circuits design metodology 2                           | 28 |

| Figure 3.2: Static library example 2                                       | 29 |

| Figure 3.3: A subset of the lib2.genlib                                    | 30 |

| Figure 3.4: Logic synthesis flow for virtual library technology mapping    | 31 |

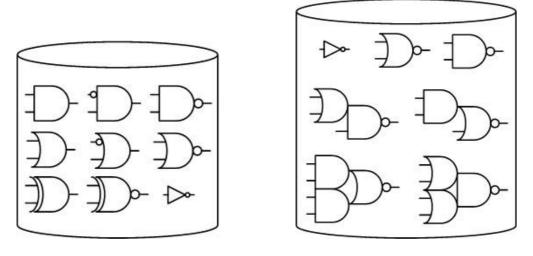

| Figure 3.5: Virtual library examples                                       | 32 |

| Figure 3.6: Graph partitioning 3                                           | 34 |

| Figure 3.7: Technology decomposition                                       | 35 |

| Figure 3.8: Matching generation                                            | 36 |

| Figure 3.9: Calculating cost on the subject graph                          | 37 |

| Figure 3.10: Tree covering result                                          | 37 |

| Figure 3.11: DAGON algorithm flow                                          | 38 |

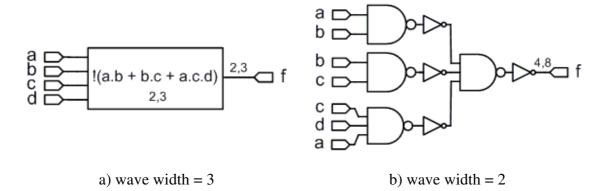

| Figure 3.12: An AOIxxx pattern                                  |    |

|-----------------------------------------------------------------|----|

| Figure 3.13:Geometric interpretation of Figure 3.12.            |    |

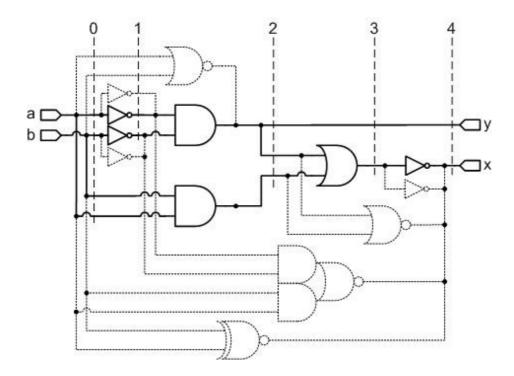

| Figure 3.14: Wavefront algorithm                                |    |

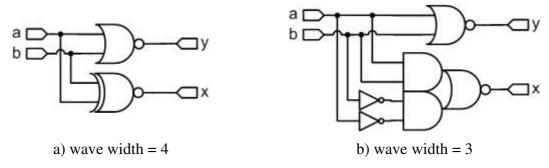

| Figure 3.15: Wavefront resulting circuits                       |    |

| Figure 3.16: An example of an AIG                               |    |

| Figure 3.17: Computation of all k-feasible cuts                 |    |

| Figure 3.18: Graph expression representation                    |    |

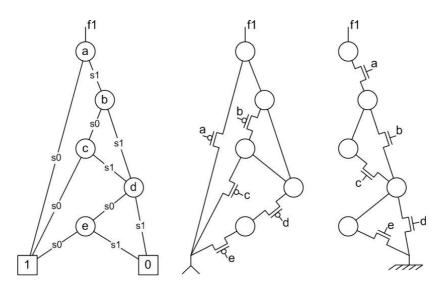

| Figure 3.19: Relation among TSBDD edges and transistor networks |    |

| Figure 3.20: Circuit example                                    |    |

| Figure 3.21: Logic cells generated by OTR algorithm             |    |

| Figure 3.22: Appling the DeMorgan's theorem on n-ary trees.     |    |

| Figure 3.23: Grouping equivalent nodes                          |    |

| Figure 3.24: Embedded decompositions (b,c) in a n-ary tree (a). | 50 |

| Figure 3.25: Cost calculation and the first cut                 | 51 |

| Figure 3.26: Final cover (before inverters minimization).       | 51 |

| Figure 4.1: Cell instances and the lower bounds                 |    |

| Figure 4.2: Computation of serial transistors.                  | 56 |

| Figure 4.3: Cost function modeling                              | 58 |

| Figure 4.4: A set of logic cells                                |    |

| Figure 4.5: Creating the subject graph                          | 59 |

| Figure 4.6: Inverters removal and phase assignments             | 59 |

| Figure 4.7: Levelizing the subject graph.                       |    |

| Figure 4.8: Adjusting polarities of the circuit nets            |    |

| Figure 4.9: Main algorithm of VIRMA-WF                          | 61 |

| Figure 4.10: Matching generation window.                        |    |

| Figure 4.11: Matching algorithm                                 |    |

| Figure 4.12: Covering algorithm.                                | 63 |

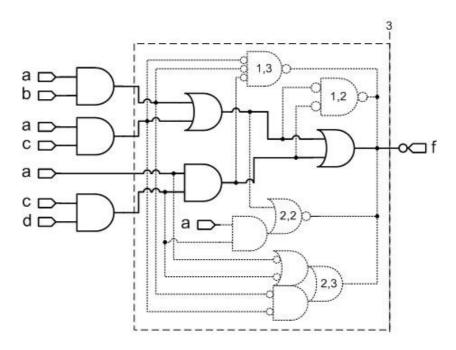

| Figure 4.13: Function inversion during the mapping process            | 3 |

|-----------------------------------------------------------------------|---|

| Figure 4.14: Decomposed circuit                                       | 4 |

| Figure 4.15: Best matches generated by VIRMA-WF.                      | 4 |

| Figure 4.16: Circuit mapped with VIRMA-WF6                            | 5 |

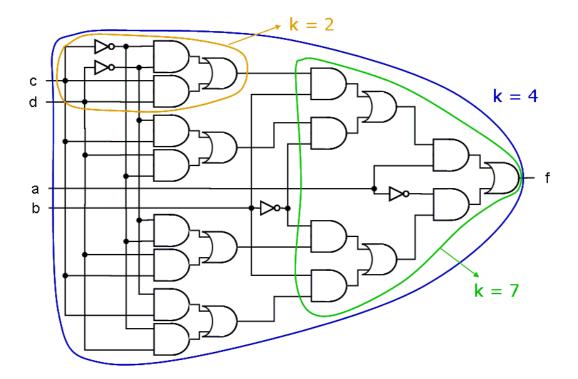

| Figure 4.17: K-cuts example 6                                         | 6 |

| Figure 4.18: 4-input XOR gates                                        | 6 |

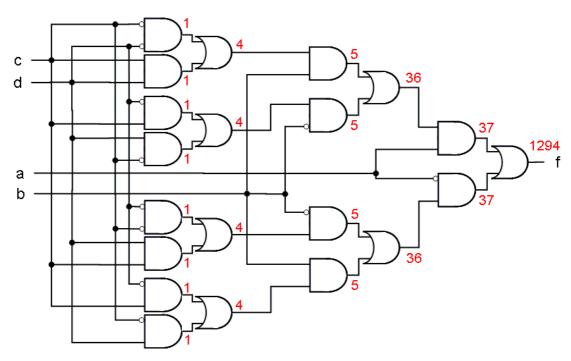

| Figure 4.19: Computing the number of possible structural combinations | 7 |

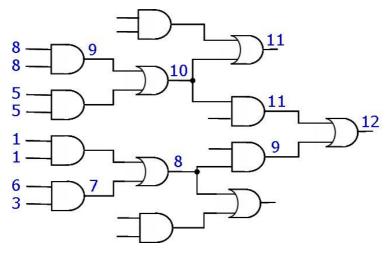

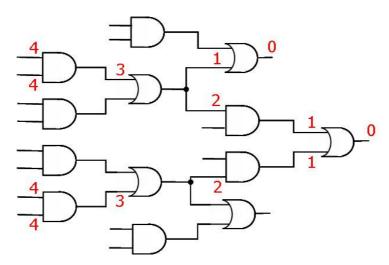

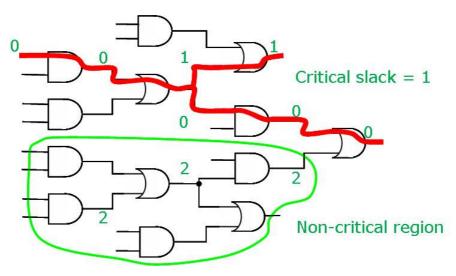

| Figure 5.1: Computing node levels (from inputs to outputs)            | 3 |

| Figure 5.2: Computing reverse node levels (from outputs to inputs)    | 3 |

| Figure 5.3: Identifying timing critical regions                       | 3 |

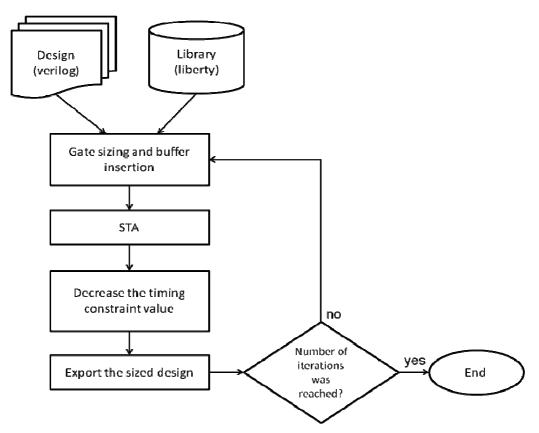

| Figure 5.4: Buffering and sizing frame work                           | 7 |

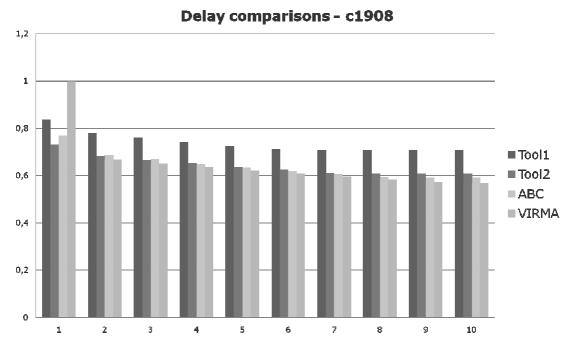

| Figure 5.5: Delay comparisons using the benchmark circuit c1908       | 8 |

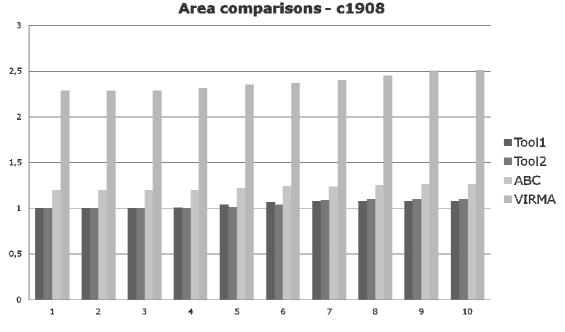

| Figure 5.6: Area comparisons using the benchmark circuit c1908        | 8 |

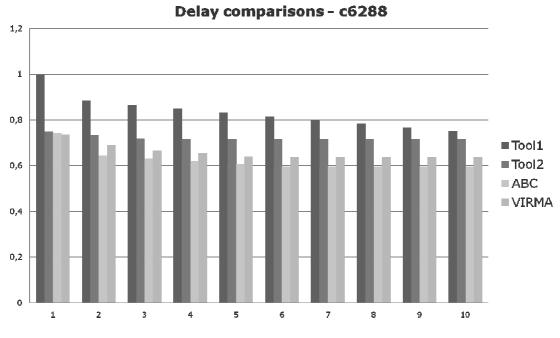

| Figure 5.7: Delay comparisons using the benchmark circuit c6288       | 9 |

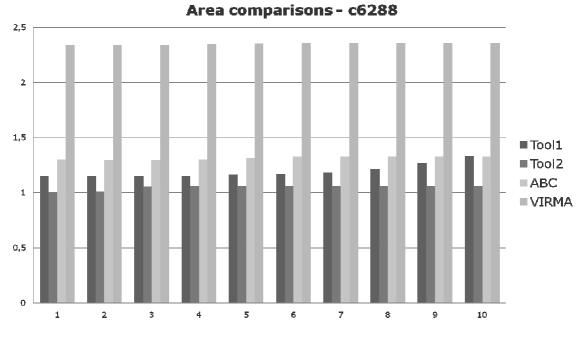

| Figure 5.8: Area comparisons using the benchmark circuit c6288        | 9 |

| Figure 5.9: Characterization problem of NCSP cells                    | 0 |

| Figure 5.10: Area effects of having inverters inside the cell         | 1 |

| Figure 5.11: Delay effects of having inverters inside the cell        | 1 |

## LIST OF TABLES

| Table 3.1: The size of CMOS CSP cell libraries induced by the number of serial transistors |

|--------------------------------------------------------------------------------------------|

| Table 3.2: Differences among previous technology mapping methods.    52                    |

| Table 4.1: Pull-up and pull-down sums in the longest path.    70                           |

| Table 4.2: Delay comparisons among SIS and VIRMA-WF.    70                                 |

| Table 4.3: Area comparisons between SIS and VIRMA-WF.    71                                |

| Table 4.4: SIS and VIRMA-WF runtime.    71                                                 |

| Table 4.5: C6288 circuit results                                                           |

| Table 4.6: Area comparison – Area saving heuristic                                         |

| Table 4.7: Delay comparison – Area saving heuristic                                        |

| Table 4.8: Pull-up and pull-down sums in the longest path.    75                           |

| Table 4.9: Delay comparisons between ABC and VIRMA                                         |

| Table 4.10: Area comparisons between ABC and VIRMA.    76                                  |

| Table 4.11: Number of instances of lower bound cells.    76                                |

| Table 4.12: Close look at the c6288 area report.    80                                     |

## ABSTRACT

Currently, microelectronic technologies enable high degrees of semiconductor integration. However, this integration makes the design, verification, and test challenges more difficult. The circuit design is often the first area under assault by the effects of aggressive scaling in deep-submicron technologies. Therefore, designers have adopted strict methodologies to deal with the challenge of developing high quality designs on a reasonable time. Electronic Design Automation tools play an important role, automating some of the design phases and helping the designer to find a good solution faster. One of the hardest challenges of an integrated circuit design is to meet the timing requirements. It depends on several steps of the synthesis flow. In standard cell based flows, it is directly related to the technology mapping algorithm and the cells available in the library. The performance of a cell is directly related to the transistor sizing and the cell topology. It determines the timing, power and area characteristics of a cell. Technology mapping has a major impact on the structure of the circuit, and on its delay and area characteristics. The quality of the mapped circuit depends on the richness of the cell library. This thesis proposes two different approaches for library-free technology mapping aiming delay reduction in combinational circuits. Both algorithms rely on a cell topology able to implement Boolean functions using minimal transistors stacks. They reduce the overall number of serial transistors through the longest path, considering that each transistor network of a cell has to obey to a maximum admitted chain. The mapping algorithms are integrated to a cell generator that creates cells with minimal transistor stacks. This cell generator is also in charge of performing the transistor sizing. Significant gains can be obtained in delay due to both aspects combined into the proposed mapping tool.

**Keywords:** technology mapping, logic synthesis, virtual cell library, standard cell library, automatic cell generator.

#### Mapeamento tecnológico para Bibliotecas Virtuais Baseado em Células com Cadeias Mínimas de Transistores em Série

### RESUMO

Atualmente, as tecnologias disponíveis para a fabricação de dispositivos eletrônicos permitem um alto grau de integração de semicondutores. Entretanto, esta integração torna o projeto, a verificação e o teste de circuitos integrados mais difíceis. Normalmente, o projeto de circuitos integrados é consideravelmente afetado com a diminuição do tamanho dos dispositivos eletrônicos em tecnologias sub-micrônicas. Conseqüentemente, os projetistas adotam metodologias rígidas para produzir circuitos de alta qualidade em tempo razoável. Ferramentas de auxílio ao projeto de circuitos eletrônicos são utilizadas para automatizar algumas das etapas do projeto, ajudando o projetista a encontrar boas soluções rapidamente. Uma das tarefas mais difíceis no projeto de circuitos integrados é fazer com que o circuito respeite as restrições de atraso. Isto depende de várias etapas do processo de síntese. Em metodologias baseadas em bibliotecas de células, isto está diretamente relacionado ao algoritmo para mapeamento tecnológico e as células disponíveis na biblioteca. O atraso de cada célula depende do tamanho dos transistores e da topologia da rede de transistores. Isso determina as características de atraso, potência e área de uma célula. O mapeamento tecnológico define as principais características estruturais do circuito, principalmente em área, potência e atraso. A qualidade do circuito mapeado depende das células disponíveis na biblioteca de células. Este trabalho propõe um novo método para mapeamento com bibliotecas virtuais para redução de atraso em circuitos combinacionais. Ambos os algoritmos baseiam-se em uma topologia de células capaz de implementar funções Booleanas com cadeias mínimas de transistores em série. Os algoritmos reduzem o número de transistores em série do caminho mais longo do circuito, considerando que cada célula é implementada por uma rede de transistores que obedecem um número máximo de transistores em série. O número de transistores em série é calculado de forma Booleana, garantindo que este seja o número mínimo necessário para implementar a função lógica da célula. Os algoritmos estão integrados a um gerador de células que utiliza tal topologia e realiza o dimensionamento dos transistores. Ganhos significativos podem ser obtidos combinando estas duas técnicas em uma ferramenta para mapeamento tecnológico.

**Palavras-Chave:** mapeamento tecnológico, síntese lógica, bibliotecas de células, bibliotecas de células virtuais, geradores de células.

## **1 INTRODUCTION**

According to the 'Moore's Law' (MOORE, 1965), since the invention of the integrated circuit (IC) in 1958, the number of transistors that can be placed "inexpensively" on an integrated circuit has increased exponentially due to advances on technology scaling. Currently, billions of electronic components can be integrated on a single chip. The processing speed and memory capacity of digital electronic devices almost increases in the same proportion of the number of transistors.

Although deep-submicron microelectronic technologies enable greater degrees of semiconductor integration, such integration makes the design, verification, and test challenges more difficult. The circuit design is often the first area under assault by the effects of aggressive scaling in deep-submicron technologies. Effects like leakage power, noise and electro-migration were considered irrelevant in early technologies. Currently, the analysis of these effects is crucial for a successful design. Therefore, designers have adopted strict methodologies to deal with the challenge of developing high quality designs on a reasonable time. Electronic Design Automation (EDA) tools play an important role, automating some of the design phases and helping the designer to find a good solution faster.

The methodology adopted by most of the EDA flows is based on standard cell libraries. In a typical standard cell based flow the synthesis starts from a high-level description using Hardware Description Languages (HDL), such as VHDL (VHDL ORG, 2008) and Verilog (VERILOG DOT COM, 2008), at Register Transfer Level (RTL). The second step is the logic synthesis that performs several logic manipulation procedures over the high level description resulting in a netlist composed by a set of cells of the standard cell library. The last step is the physical synthesis that places and routes the cells of a netlist on a floorplan. The main advantage of this methodology is that each cell in the library is fully characterized through many simulations, resulting in a set of accurate information about the behavior of the cell. Thereby, the designer can, with the aid of an EDA tool, predict with a very good precision the characteristics of the final circuit.

Even though the available EDA tools perform a good job on finding good solutions for a given design, there are still some open issues in the automation flow. Furthermore, every time that the manufacturing technology process advances to the next generation, new problems come up. It demands a constant update in the available tools or even completely new tools. Hence, there is a high cost associated to the technology process shifting. It requires investments on tools and on manufacturing process. Alternatively, the designer can explore other optimization strategies in order to increase performance and to reduce area and power without changing the technology.

16

One of the big challenges in high-performance circuits design is the timing closure of the combinational logic (or random logic). Usually, combinational logic is not regular enough to be implemented in an intuitive design flow. Furthermore, it can be changed until the last steps of the design cycle. Logic synthesis has been shown to be an effective tool for designing logic circuits, especially for semicustom designs using a standard cell methodology. The computer-aided synthesis of a logic circuit involves two major steps: the optimization of a technology-independent logic representation, using Boolean and/or algebraic techniques, and technology mapping. Logic optimizations are used to modify the structure of a logic description, such that the final structure has a lower cost than the original one. These optimizations are performed before the technology mapping.

Technology mapping is the step of logic synthesis that chooses the cells that will be used to implement a design in a given technology. This step of logic synthesis has a major impact on the structure of the circuit and, consequently, on delay and area characteristics. Most existing techniques are based on static pre-characterized libraries (standard cell methodology), where a set of cells is defined and characterized for a given technology. First methods for technology mapping (KEUTZER, 1987-a) (DETJENS, 1987) (ABOUZEID, 1992) (MAILHOT, 1993) (LIEN, 1992) used trees as the initial description of the circuit to be mapped. More recent methods (LEHMAN, 1997) (KUKIMOTO, 1998) (STOK, 1999) (MISHCHENKO, 2005) are based on Directed Acyclic Graph (DAG) representations that allow duplicating logic to some extent to increase speed. Another important contribution to technology mapping was Boolean matching (MAILHOT, 1993), where the matching of a portion of the circuit and a cell from the library is done by comparing the Boolean function of the candidates, instead of the structure. Structural comparison would not be able to find all matches.

In the early days of technology mapping, it was considered that the use of a cell generator would enable the use of larger virtual (built on demand) cell libraries. Berkelaar (1988) has presented a pioneer work aiming cell generators, which maps decomposed logic expressions onto complex gates. Reis (1997) presented another approach which uses a Binary Decision Diagram (BDD) representation for the circuit network, and performs BDD decomposition using constraints in the number of serial transistors. Each decomposed BDD is mapped onto a static CMOS complex gate. The work in (CORREIA, 2004) dynamically explores many embedded AND/OR decompositions by using n-ary trees for the circuit network representation. Each subtree that is limited by the number of serial transistors is also mapped onto static CMOS cells. In (JIANG, 2001) two techniques for technology mapping are presented. The first method maps circuits to a virtual cell library of complex static CMOS gates. The second technique uses a mixed logic of static CMOS and PTL gates, considering the relation between PTL and BDDs.

Unfortunately, the use of such approaches was not widely verified in a commercial level, even if other references suggest that the increased number of cells in a library could lead to significant improvements in the quality of the final design (KEUTZER, 1987-b) (SCOTT, 1994) (SECHEN, 1996) (GAVRILOV, 1997). A recent approach presented in (ROY, 2005) suggests that the addition of some custom cells to a library can improve the speed of the final circuit.

#### **1.1 Motivation and thesis contributions**

According to the previously statements, one of the hardest challenges of an IC design is to meet the timing requirements. It depends on several steps of the synthesis flow. In standard cell based flows, it is directly related to the technology mapping algorithm and the cells available in the library. The performance of a cell is directly related to the transistor sizing and the cell topology. The transistor sizing also affects the power consumption and, off-course, the cell area.

Recently, some methods for generating efficient cell networks were proposed (KANECKO, 1997) (POLI, 2003) (TANAKA, 2004) (SCHNEIDER, 2005), including a method to compute the minimum number of transistors in series needed to implement an arbitrary Boolean function that was proposed by Schneider (2005). The reduction of the number of series switches leads to timing efficient networks.

The topology presented in (SCHNEIDER, 2005) was only verified at the cell level, lacking of an efficient methodology to evaluate the use of these cell topologies in larger circuits. Motivated by this, this thesis presents two different methods for "VIRtual library technology MApping" (VIRMA) based on DAGs. Both mapping methods combine the method for Boolean computation of the number of series transistors introduced by Schneider (2005) with state of the art technology mapping algorithms inspired by the approaches presented by Stok (1999) and Mishchenko (2005). Significant gains can be obtained in delay due to both aspects combined into the proposed mapping tool.

Since this cell topology was not well explored yet, both algorithms implemented in the VIRMA tool are library-free. It chooses the transistor configuration for the cells that will have to be created through a cell generation tool in a subsequent step. Currently, the VIRMA mapping flow is integrated to a cell generator that implements the techniques proposed in (Rosa, 2008). This cell generator is also in charge of performing the transistor sizing.

#### **1.2 Thesis organization**

The remaining of this thesis is organized as follows: chapter 2 review some general concepts required for a better comprehension of the proposed methods. Specific concepts of technology mapping as well as some previous approaches are described in the chapter 3. The new approaches for library-free technology mapping are presented in the chapter 4. All results obtained through the implemented prototypes are shown in the chapter 5. Finally, conclusions and future works are presented in the chapter 6.

## 2 TERMINOLOGY AND BASIC CONCEPTS

Electronic design automation is divided into many sub-areas. We are particularly interested in logic synthesis and physical synthesis (related to cell generators) concepts. This chapter introduces some of these concepts and definitions that will be used in the following chapters. For next chapters, we assume the knowledge of all definitions described here.

#### 2.1 Boolean logic and logic expressions

The **Boolean domain** (*B*) is defined as a two element set, say,  $B = \{0, 1\}$ , whose elements are interpreted as logical values, typically 0 = false and 1 = true. A Boolean function describes how to determine a Boolean value output based on some logical calculation from Boolean inputs. A **Boolean function** is a function of the form *f*:  $B^n \rightarrow B$ , where  $B = \{0, 1\}$  is a Boolean domain and where *n* is a non-negative integer. In the case where n = 0, the "function" is simply a constant element of *B*. More generally, a Boolean-valued function is a function of the type *f*:  $X \rightarrow B$ , where *X* is an arbitrary set and where *B* is a Boolean domain. If  $X = [n] = \{1, 2, 3, ..., n\}$ , then *f* is a **binary sequence** of length *n*. Therefore, there are  $2^{2^n}$  such functions.

The **support** of a Boolean function is the set of variables that may change the output value of a function. For instance, consider the function f(a,b,c)=ab+a'c. Its support is the set  $\{a, b, c\}$ . An **input vector** is an element defined in Boolean domain and indicates the value of each variable that defines the Boolean space. An input vector  $v \in B^n$  belongs to the **ON-set** of f if and only if f(v) = 1. Otherwise, if f(v) = 0, then v belongs to the **OFF-set** of f. While the vectors  $v_1 = \{1,1,0\}$  and  $v_2 = \{0,1,1\}$  belong to the ON-set of the function f(a,b,c)=ab+a'c, the vector  $v_3 = \{1,0,0\}$  goes into the OFF-set of f(a,b,c).

A logic expression (or equation) is a Boolean function representation. Each function is unique for any application  $f: B^n \to B$  in the whole Boolean space. However, a Boolean function has infinite representations. All Boolean functions can be expressed in a canonical form through sum of products (SOP) or product of sums (POS). A SOP is said canonical when all variables appear in all products. Every instance of a Boolean variable is called literal according to Wagner (2006). A product of literals is formally called cube. For instance,  $\{a, b, c\}$  is a cube interpreted like *a.b.c* or just like *abc*. A minterm is a cube that contains all variables of the function support.

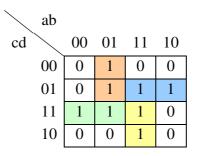

Figure 2.1 shows a truth table and the minterms of the Boolean function f. Equation 2.1 represents f through a SOP in a canonical form. This equation has 32 literals and it is not a minimal SOP. Karnaugh maps (KARNAUGH, 1953) and the Quine-McCluskey method that comes from (QUINE, 1955) and (MCCLUSKEY, 1956) are the main exhaustive optimization techniques for two-level minimization. Although they are not practical algorithms for large circuits, they are easy to use and simple to understand. The Espresso algorithm (McGeer, 1993) is a heuristic method for two-level minimization that is computationally less expensive and presents good results. An example of two-level minimization can be seen in Figure 2.2. It shows the Karnaugh map for the Boolean function f. The minimal cover for the ON-set is composed by four cubes. It can be represented through the Equation 2.2. Equation 2.3 shows the minimal cover for the OFF-set of function f.

$$f = \overline{a}.\overline{b}.c.d + \overline{a}.\overline{b}.\overline{c}.\overline{d} + \overline{a}.\overline{b}.\overline{c}.d + \overline{a}.\overline{b}.c.d + \overline{a}.\overline{b}.\overline{c}.d + \overline{a}.\overline{b}.\overline{c}.d + \overline{a}.\overline{b}.\overline{c}.d + \overline{a}.\overline{b}.c.d + \overline{a}.\overline$$

$$ON - set(f) = \overline{a.c.d} + \overline{a.b.c} + \overline{a.c.d} + \overline{a.b.c}$$

(2.2)

$$OFF - set(f) = a.c.d + a.b.c + a.c.d + a.b.c$$

(2.3)

| a         b         c         d         f           0         0         0         0         0         0 |              |

|---------------------------------------------------------------------------------------------------------|--------------|

| 0 0 0 0 0                                                                                               |              |

|                                                                                                         |              |

| 0 0 0 1 0                                                                                               |              |

| 0 0 1 0 0                                                                                               |              |

| $0  0  1  1  1  \rightarrow$                                                                            | <br>a.b.c.d  |

|                                                                                                         | a.b.c.d      |

|                                                                                                         | <br>a.b.c.d  |

| 0 1 1 0 0                                                                                               |              |

| $0  1  1  1  1  \rightarrow$                                                                            | _<br>a.b.c.d |

| 1 0 0 0 0                                                                                               |              |

| $1  0  0  1  1  \rightarrow$                                                                            | a.b.c.d      |

| 1 0 1 0 0                                                                                               |              |

| 1 0 1 1 0                                                                                               |              |

| 1 1 0 0 0                                                                                               |              |

| $1  1  0  1  1  \rightarrow$                                                                            | a.b.c.d      |

|                                                                                                         | a.b.c.d      |

|                                                                                                         | a.b.c.d      |

Figure 2.1: Truth table for the function *f* and the respective minterms.

Figure 2.2: Karnaugh map for the Boolean function f.

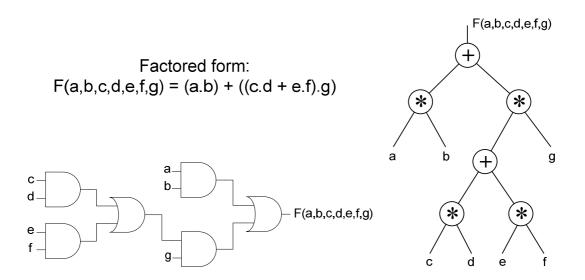

Both equations can also be represented as **factored forms**. According to Brayton (1987), a factored form can be defined as a representation of a logic function that is either a single literal or a sum or product of factored forms. It is very similar to a parenthesized algebraic expression. This parenthesized representation seems to be the most appropriate representation for use in multilevel logic synthesis. As an example, consider the representations in Figure 2.3. The parenthesized expression can be seen as a **logical operator tree**. Any representation with more than two levels is called a multilevel representation. In this example, the logical operator tree has depth four (or four levels).

There are several methods for obtaining different factored forms for a given logic function. These methods range from purely algebraic ones, which are quite fast, to so-called Boolean ones, which are slower but are capable of giving better results. Since obtaining an optimal (shortest length) factorization for an arbitrary Boolean function is an NP-hard problem (MINTZ, 2005), all practical algorithms for factoring are heuristic and provide a correct, logically equivalent formula, but not necessarily a minimal length solution. Brayton (1987) has presented one of the most known heuristics for algebraic factorization. More recently, another heuristic was introduced by Mintz (2005). Usually, it gets significantly better factorizations than former algebraic factoring and are quite competitive with Boolean factoring but with lower computation costs.

Figure 2.3: Multilevel representations.

#### 2.2 Logic styles of transistor networks

A logic gate or logic cell can be defined as a network of transistors (or other electronic/electromagnetic components). The association of these components is used to implement arbitrary Boolean functions. Usually, logic gates are created following a given topology. The most common logic styles are the Pass-Transistor Logic (PTL) and the Complementary Series/Parallel (CSP) CMOS (also known as static CMOS). Independently of the topology, the output of the cell is either connected to *VDD* or *GND* through one or more paths of interconnected transistors. A path from *VDD* to the cell output is called **pull-up path**, while a path from *GND* to the cell output is called **pull-up neth**.

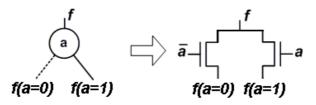

There are several techniques for an automated transistor network generation. Buch (1997), Hsiao (2000), Shelar (2001), Shelar (2002) and Avci (2003) have proposed methods for PTL network generation. Most of them are based on Binary Decision Diagrams<sup>1</sup> (BDDs). Every node of a BDD is a decision point which matches to a two-input multiplexer (refer to Figure 2.4). This element implements the Shannon expansion that is expressed by Equation 2.4. In our BDD representation, the dashed arcs represent the decision for the negative cofactor(f(a=0) in the example of Figure 2.4), while the other arcs correspond to the positive cofactor (f(a=1) in the example). The composition of the cofactors and the decision variable (*a* in this case) are able to express the function *f* through the Shannon expansion. Due to this, a PTL cell can be easily derived from a BDD using pass transistors to build multiplexers. This will be demonstrated in Example 1.

$$f = a.f(a=1) + \overline{a.f(a=0)}$$

(2.4)

Figure 2.4: Correspondence among BDD nodes and multiplexers.

**Example 1**: Consider the function f(a,b,c,d) such that the ON-set and the OFF-set are represented by Equations 2.5 and 2.6, respectively.

$$ON - set(f) = \overline{a}, \overline{b} + \overline{a}, \overline{c} + \overline{b}, \overline{c} + \overline{b}, \overline{d}$$

(2.5)

$$OFF - set(f) = a.b + b.c + a.c.d$$

(2.6)

<sup>&</sup>lt;sup>1</sup> Binary Decision Diagrams were introduced by Lee (1959). The basic idea from which this data structure was created is the Shannon decomposition (SHANNON, 1938). These two concepts resulted in efficient data structure proposed by Bryant (1986). Few years later, Brace (1990) extended it to a strongly canonical form that is so-called *Reduced Ordered Binary Decision Diagram* (ROBDD). In popular usage, the term BDD almost always refers to ROBDDs.

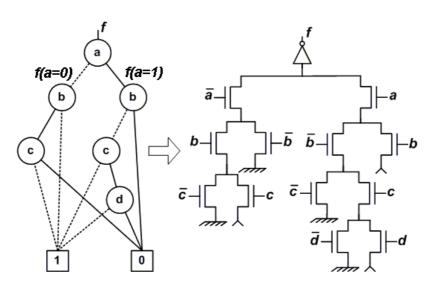

Figure 2.5 shows a BDD that represents the Boolean function f(a,b,c,d) and a possible PTL implementation. Every BDD node was replaced by a pair of transistors implementing a multiplexer that is controlled by the node variable. The resulting transistor network is composed by NMOS transistors only. Moreover, it has an inverter in the cell output that works like a signal amplifier. This way, the assignments for the source nodes (the terminal nodes 0 and 1 of the BDD) are also inverted for a correct implementation. Consider the input vector  $v(a,b,c,d) = \{0, 1, 0, 0\}$ . In the Figure 2.6, this vector activates a path in the BDD that leads to the *terminal node* 1. In the PTL transistor network, a pull-down path is sensitized. Therefore, it gives *VDD* in the inverter output which corresponds to the logical value 1.

Figure 2.5: PTL transistor network derived from a BDD.

Figure 2.6: Path sensitization in a PTL network.

Generally, the number of transistors in PTL cells is linearly proportional to the number of BDD nodes. There are techniques to reduce this number in some special cases. These techniques are discussed in (ROSA, 2006). In PTL cells, the same

intermediate node can be both in a pull-up path and in a pull-down path. When the transistor network has these shared nodes, it is said a **non-disjoint** network. Another important point is the length of the longest path. The maximum number of stacked transistors corresponds to the number of arcs in the longest path in the BDD.

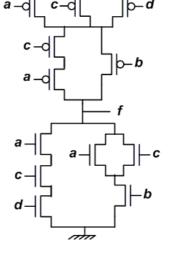

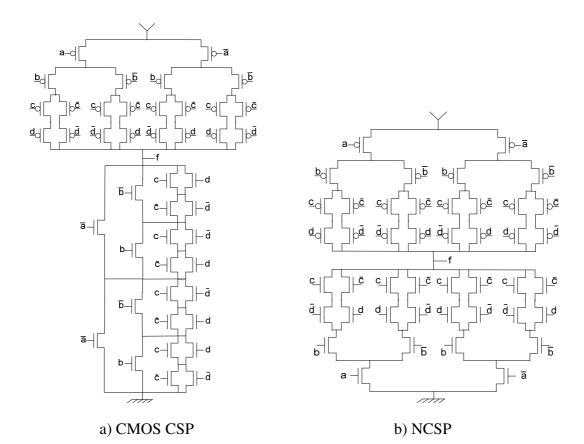

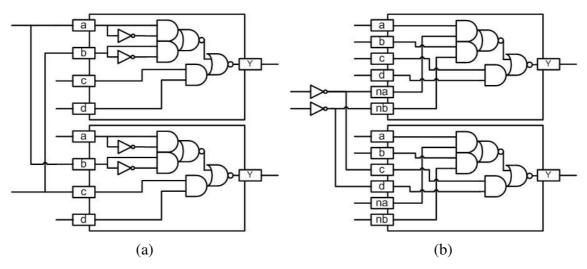

Complementary Series/Parallel cells are implemented using two disjoint transistor planes. The pull-up plane (pull-down plane) corresponds to the set of interconnected transistors between the cell output and VDD (GND). While the pull-up plane is only composed by PMOS transistors, the pull-down plane is composed by NMOS transistors. When the pull-up plane is derived from the ON-set equation of a Boolean function, the topology of the pull-down plane is the series/parallel complement of the pull-up plane. In a similar way, CSP cells can be derived from the OFF-set equation. In this case, the pull-down is derived directly from the equation and the pullup is the series/parallel complement of the pull-down. The topological complementarity assures the logical complementarity of the transistor network. Figure 2.7 shows CSP cells derived from the ON-set and OFF-set equations (Equations 2.5 and 2.6, respectively). In the cell of Figure 2.7a, each pull-up path matches to a cube of the Equation 2.5. The pull-down paths depend on the series/parallel associations of the pullup plane. Notice that the longest pull-up path has two series transistors, while the longest pull-down path has four series transistors. The longest pull-up and pull-down paths of the cell derived from the Equation 2.6 have three series transistors. This illustrates that the length of the longest path can vary for different implementations of the same logic function.

a) cell derived from *ON-set*(*f*)

b) cell derived from *OFF-set(f)*

Figure 2.7: CSP CMOS transistor networks for f.

#### 2.3 Minimal length for transistor stacks in standard cell libraries

For approaches that are intended for cell generators, the number of serial transistors inside a cell is an important parameter. The methods presented by Berkelaar (1988), Gavrilov (1997), Reis (1997), Jiang (2001) and Correia (2004) use a maximum

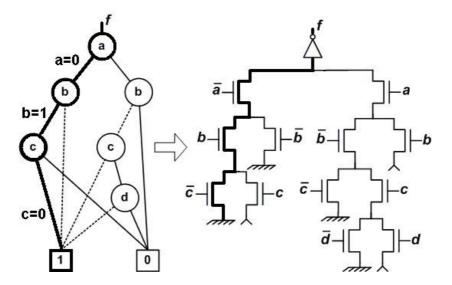

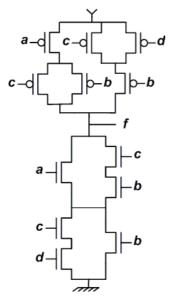

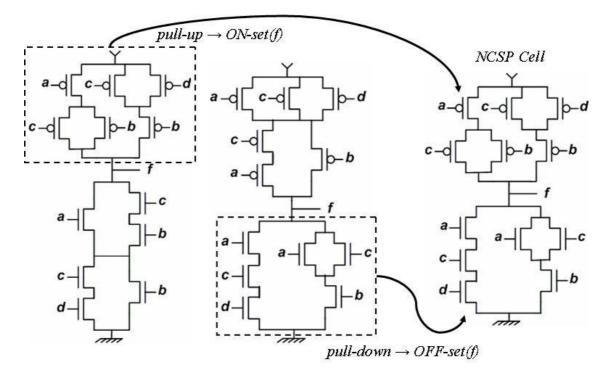

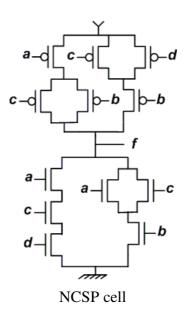

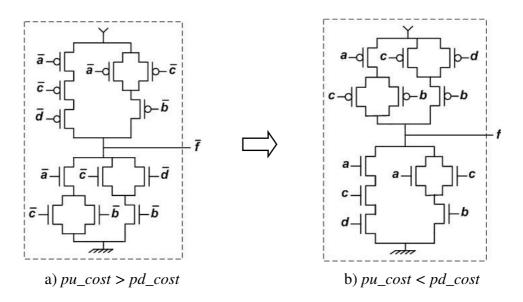

allowed number of transistor in series as a parameter to restrict the size of feasible cells. All these approaches are limited to the use of serial/parallel implementations, and the computation of the number of serially connected transistors is done by serial/parallel association. Schneider (2005) proposes a design methodology to implement complex gates with the exact lower bound for the number serial transistors. More details of this approach can be also found in (SCHNEIDER 2006). It is based on the observation that the number of literals on the smallest cube<sup>2</sup> of the ON-set (OFF-set) prime irredundant cover determines the maximum number of serial transistors of the pull-up (pull-down) plane. Due to their topologies, PTL and CSP CMOS cells do not respect the lower bound in several practical cases. A different topology can be used to implement complex gates with the exact lower bound for the number serial transistors. Such topology is called Non-Complementary Series/Parallel (NCSP), where the minimum cover for the ON-set is used to derive the pull-up plane, and the minimum cover for the OFF-set is used to derive the pull-up plane. These cells do not have topological complementary plans. However, they are logically complementary.

Consider the CSP CMOS cells in Figure 2.7. The NCSP cell which implements the Boolean function f is shown in Figure 2.8. Just like the CSP CMOS cell, the longest pull-down path has three serial transistors. However, the smallest cube of the minimum cover for the ON-set has two literals. Thus, two serial transistors is the length of the longest pull-up path.

Figure 2.8: NCSP cell for the Boolean function *f*.

<sup>&</sup>lt;sup>2</sup> The smallest cube is the one with more literals.

Accordingly to Weste (1994), the usual CSP CMOS has one important characteristic: low static power consumption. Significant power is only drawn when the transistors in the CMOS device are switching between on and off states. Although the pull-up and pull-down networks are not complementary in NCSP, they are logically complementary. Hence, there will not be any viable path connecting *VDD* and *GND* for any input vector. Therefore, the same principles of the CSP CMOS logic are applied to the NCSP logic. Figure 2.9 shows this property through an example. The truth table of the function f was associated to two columns named *VDD* and *GND*. They represent the occurrence of the voltages corresponding to *VDD* and *GND* in the cell output.

| а | b | c | D | f | VDD | GND |

|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 1 | yes | no  |

| 0 | 0 | 0 | 1 | 1 | yes | no  |

| 0 | 0 | 1 | 0 | 1 | yes | no  |

| 0 | 0 | 1 | 1 | 1 | yes | no  |

| 0 | 1 | 0 | 0 | 1 | yes | no  |

| 0 | 1 | 0 | 1 | 1 | yes | no  |

| 0 | 1 | 1 | 0 | 0 | no  | yes |

| 0 | 1 | 1 | 1 | 0 | no  | yes |

| 1 | 0 | 0 | 0 | 1 | yes | no  |

| 1 | 0 | 0 | 1 | 1 | yes | no  |

| 1 | 0 | 1 | 0 | 1 | yes | no  |

| 1 | 0 | 1 | 1 | 0 | no  | yes |

| 1 | 1 | 0 | 0 | 0 | no  | yes |

| 1 | 1 | 0 | 1 | 0 | no  | yes |

| 1 | 1 | 1 | 0 | 0 | no  | yes |

| 1 | 1 | 1 | 1 | 0 | no  | yes |

Figure 2.9: Simulation table of the NCSP cell.

#### 2.4 Digital circuits representation

Digital circuits can be represented in many ways. Graphs<sup>3</sup> are widely used for this purpose. A Directed Acyclic Graph (DAG) is one of the most popular representation for logical circuits. On these structures, each logic gate is represented by a vertex and its connections by edges.

A gate g1 is **fanin** of g2 if the output of g1 is connected to a g2 input. This way, g2 is part of the **fanout** of g1. The **fanout degree** of a logic gate is determined by the number of logic gates connected to its output. For instance, if the logic gate g1 is connected to inputs of the gates g2 and g3 then its fanout degree (or just fanout) is two.

<sup>&</sup>lt;sup>3</sup> In mathematics and computer science graphs are used to model pairwise relations between objects from a certain collection. A graph refers to a collection of vertexes or 'nodes' and a collection of edges that connect pairs of vertexes. Each vertex has at least an incoming edge and an outgoing edge.

When there is no gate with fanout greater than one, the circuit is called fanout-free. Fanout-free regions are also known as **logic cones**.

A path in a graph is an alternate sequence of vertexes such that from each of its vertexes there is an edge to the next vertex in the sequence. Formally, it is a set of vertex and connections  $\{c_0, g_0, c_1, ..., c_n, g_n, c_{n+1}\}$ , where a connection  $c_i, 1 \le i \le n$ , connects the output of  $g_{i-1}$  to an input of  $g_i$ . The connections  $c_0$  and  $c_{n+1}$  corresponds to a **primary input** (PI) and **primary output** (PO), respectively. The **depth** of a graph (circuit) is the maximum number of vertexes (gates) in any path of the graph. Consequently, each vertex has a depth value that is given by the distance from the vertexes. Each logic gate g has a delay d(g) as well as each connection has an associated delay d(c). The delay of path is defined as  $d(P) = \sum_{i=0}^{n} d(g_i) + \sum_{i=0}^{n+1} d(c_i)$ .

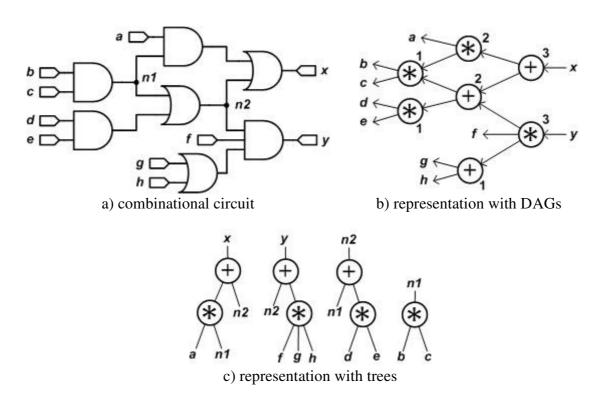

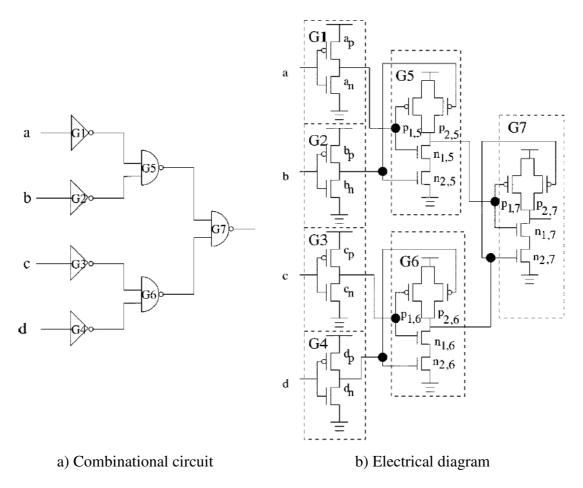

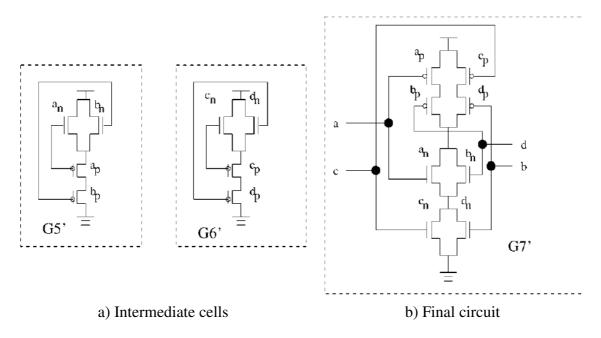

Consider the combinational circuit of Figure 2.10.a. This circuit can be represented by the DAG of Figure 2.10.b. The graph is directed from the primary outputs to the primary inputs. The logic depths, which are numerically represented, can be calculated through a depth-first search algorithm. In this example, the circuit has depth three. The networks n1 and n2 are connected to gates with fanout greater than one. In the DAG, these gates are represented by the vertexes that have more than one arriving edge. The graphical representation of Figure 2.10.b is a more formal way to see the usual graphical representation of Figure 2.10.a. Thus, we will refer DAGs just by using the representation of Figure 2.10.a.

Combinational circuits can also be represented by trees. The trees are a specialized kind of graph where all vertexes have fanout one (they are fanout-free representations). The Figure 2.10.c shows a forest of logical operator trees. Each tree corresponds to a logic cone of the circuit.

Figure 2.10: Combinational circuit representations

### **3** TECHNOLOGY MAPPING

Technology mapping is a foundation of the logic synthesis process. It is used to define the set of elements from a library that will implement a circuit in a given technology. Typically, the objective function aims the optimal use of all gates in the library to produce a circuit with critical-path delay less than a target value and minimum area. It may sound to be an interpretation of the general logic optimization problem. However, the role of technology mapping is to finish the synthesis of the circuit by performing the final gate selection from a particular library. It assumes that the technology-independent circuit has already undergone through a significant Boolean/structural optimization. In general, these algorithms do not change the structure of the circuit radically, for instance, either by finding common expressions between two or more parts of the circuit or reducing the logic depths of the critical paths. They are simplified because they are constrained by the structure of the equations produced by the technology-independent optimizations. This structural dependence has been studied by Chatterjee (2005), and it is also known as *structural bias*.

Most existing techniques for technology mapping are based on precharacterized libraries, and can be classified into four categories: rule-based mapping (GREGORY, 1986), graph matching (KEUTZER, 1987-a), direct mapping (LEGA, 1988) and functional matching (MAILHOT, 1993). Ideally, technology mapping algorithms should be able to satisfy several goals and to handle different libraries. It is a quite hard task since the cell libraries normally have a different set of cells that implements a limited set of logic functions. A library of fixed size restricts the choices for covering a given circuit. Other approaches for technology mapping propose techniques based on cell generators. Instead of having a static library, they assume that arbitrary cells can be generated on the fly through a cell generator, increasing the matching search space.

Besides specifying the technology mapping problem, this chapter shows specific concepts and techniques for technology mapping, such as data structures, technology libraries and some of the existing methods.

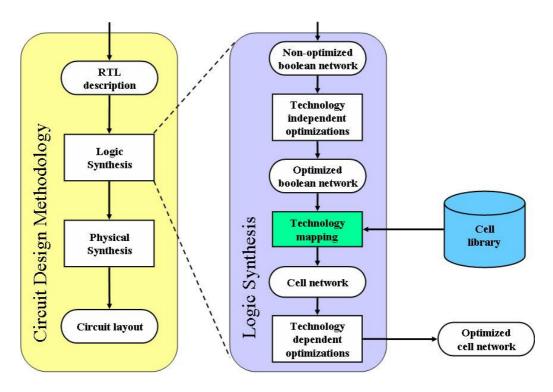

#### 3.1 Cell libraries

A cell library can be defined as a finite set of logic gates that implements different Boolean functions with different *drive strengths* and topologies. Traditionally, the technology mapping methods rely on static precharacterized libraries aiming delay, area and power optimizations. Each cell in the library is fully characterized through many simulations using complex numerical methods. The result of this process is a set of accurate information about the behavior of the cell, concerning timing and power consumption, and its physical area. According to Sechen (2003), the characterization cost of a library is expensive. Hence, commercial libraries are typically composed of few hundred combinational cells and sequential elements like latches and flip-flops for which highly optimized layouts have been optimized for a particular technology. The logic designers are then restricted to using these cells in their circuit designs. Figure 3.1 shows the usual circuit design flow considering technology mapping methodologies based on libraries with a fixed size.

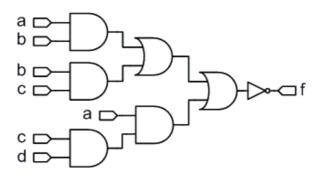

A very simple library is illustrated in Figure 3.2. The cell library names are shown together with their area costs, their function and their DAG representations in terms of two-input AND/OR gates and inverters. The DAG representations correspond to graph patterns used by the matching algorithm. An equivalent library description is given in the Figure 3.3. It corresponds to a subset of the *lib2.genlib* that is distributed with the SIS tool (SENTOVICH, 1992).

Figure 3.1: Digital circuits design methodology.

| Cell  | Cost | Symbol | Primitive graph pattern |

|-------|------|--------|-------------------------|

| INV   | 2    |        |                         |

| NAND2 | 4    |        |                         |

| NAND3 | 6    |        |                         |

| NAND4 | 8    |        |                         |

| NOR2  | 4    |        |                         |

| NOR3  | 6    |        |                         |

| NOR4  | 8    |        |                         |

| AOI21 | 6    |        |                         |

| OAI21 | 6    |        |                         |

| AOI22 | 8    |        |                         |

| OAI22 | 8    |        |                         |

| XOR2  | 10   |        |                         |

Figure 3.2: Static library example.

GATE inv1 928.00 O=!a; PIN a INV 0.0514 999.0 0.4200 4.7100 0.4200 3.6000 GATE xor 2320.00 O=(!a\*b)+(a\*!b); PIN a UNKNOWN 0.1442 999.0 1.7700 5.2300 0.9600 4.6400 PIN b UNKNOWN 0.1381 999.0 1.9400 4.6500 1.1400 5.2200 GATE nand2 1392.00 O=!(a\*b); PIN a INV 0.0777 999.0 0.6400 4.0900 0.4000 2.5700 PIN b INV 0.0716 999.0 0.4600 4.1000 0.3700 2.5700 GATE nand3 1856.00 O=!(a\*b\*c); PIN a INV 0.1000 999.0 0.8900 3.6000 0.5100 2.4900 PIN b INV 0.0828 999.0 0.7100 4.1100 0.4200 2.5000 PIN c INV 0.0777 999.0 0.5600 4.3900 0.3500 2.4900 GATE nand4 2320.00 O=!(a\*b\*c\*d); PIN a INV 0.1030 999.0 1.2700 3.6200 0.6700 2.3900 PIN b INV 0.0980 999.0 1.0900 3.6100 0.6100 2.3900 PIN c INV 0.0980 999.0 0.8200 3.6200 0.5500 2.4000 PIN d INV 0.1050 999.0 0.5800 3.6200 0.3800 2.3900 GATE nor2 1392.00 O=!(a+b); PIN a INV 0.0736 999.0 0.3300 3.6400 0.4500 3.6400 PIN b INV 0.0968 999.0 0.5000 3.6400 0.7000 3.6600 GATE nor3  $1856.00 \ O=! (a+b+c);$ PIN a INV 0.0856 999.0 0.8400 5.0400 1.3000 3.4500 PIN b INV 0.0806 999.0 0.7800 5.0300 1.1400 3.4300 PIN c INV 0.0826 999.0 0.5200 5.0300 0.8400 3.4400 GATE nor4 2320.00 O=! (a+b+c+d); PIN a INV 0.0887 999.0 0.4100 5.9100 1.1600 3.2000 PIN b INV 0.0867 999.0 0.8500 5.9100 1.5300 3.1800 PIN c INV 0.0867 999.0 1.1100 5.9200 1.7500 3.1900 PIN d INV 0.0887 999.0 1.2700 5.9100 1.9400 3.2000 GATE aoi21 1856.00 O=!((a\*b)+c); PIN a INV 0.1029 999.0 0.7500 3.5200 0.6700 2.5300 PIN b INV 0.0908 999.0 0.6700 3.6400 0.6200 2.5200 PIN c INV 0.1110 999.0 0.5800 3.6400 0.2100 1.2800 GATE aoi22 2320.00 O=!((a\*b)+(c\*d)); PIN a INV 0.1019 999.0 0.9200 3.4600 0.9400 2.7900 PIN b INV 0.0908 999.0 0.8400 3.6400 0.8500 2.7900 PIN c INV 0.0958 999.0 0.6100 3.6400 0.4900 2.9300 PIN d INV 0.0988 999.0 0.7000 3.6400 0.5400 2.9300 GATE **oai21** 1856.00 O=!((a+b)\*c); PIN a INV 0.1019 999.0 0.6900 3.9400 0.5300 2.4700 PIN b INV 0.0979 999.0 0.8700 3.9300 0.6300 2.4700 PIN c INV 0.0998 999.0 0.3700 2.0500 0.5700 2.5100 GATE **oai22** 2320.00 O=!((a+b)\*(c+d)); PIN a INV 0.1009 999.0 1.1000 4.0600 0.9000 2.5000 PIN b INV 0.1029 999.0 0.9900 4.0600 0.6800 2.3600 PIN c INV 0.0958 999.0 0.6900 3.6600 0.7400 2.5300 PIN d INV 0.1039 999.0 0.6100 3.6600 0.5600 2.0600

Figure 3.3: A subset of the *lib2.genlib*.

The quality of the mapped circuits is very dependent on the richness of the library in terms of the number of implemented logic functions, drive strengths and topologies. Libraries that implement a large number of Boolean functions lead to better results when compared to sparsely populated libraries. Keutzer (1987-b) analyzed the impact of the library size. He demonstrated that a better area optimization can be achieved using large libraries. As Jiang (2001) has observed, the most recent device

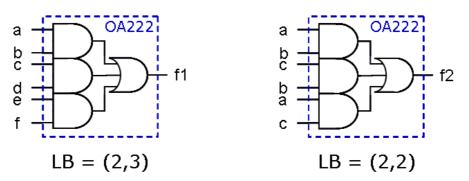

technologies encourage the usage of complex gates in deep-submicron circuits. It leads to better circuit performance. Nevertheless, it complicates the problem of the traditional library-based technology mapping. In order to increase the use of complex gates in the design, the number of implemented Boolean functions has to be increased. The side effect is that this number grows exponentially. Thus, the number of gates in any library of a reasonable size can only capture a small fraction of the total number of possibilities. It makes the traditional technology mapping too restrictive.

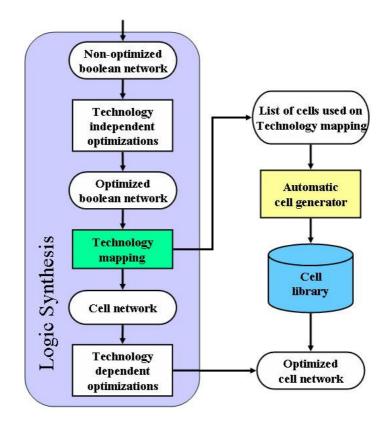

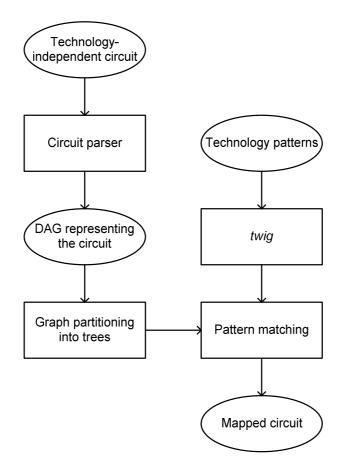

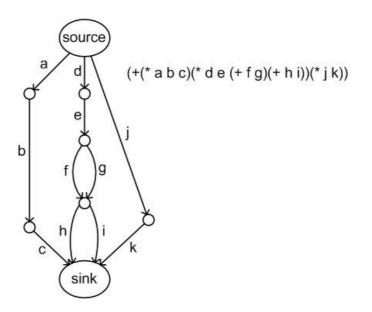

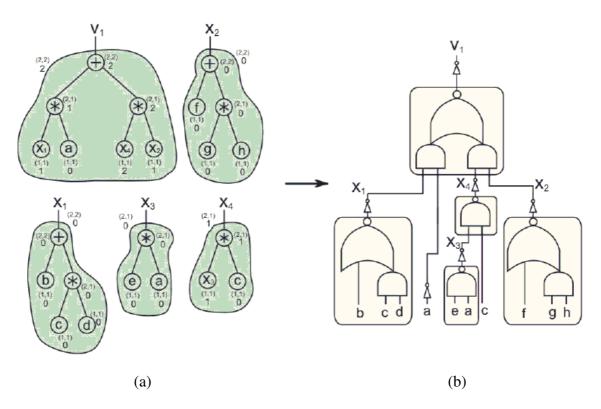

There are approaches for technology mapping based on virtual/dynamic cell libraries (it is also know by library-less technology mapping). These methods assume that each cell in the library is generated on-the-fly by a module generator. Figure 3.4 illustrates the logic synthesis flow of these approaches. The mapping algorithm defines the set of cells used in the circuit implementation. This set is the input for a cell generator which provides the cell layouts that are further used in physical synthesis.

Figure 3.4: Logic synthesis flow for virtual library technology mapping.

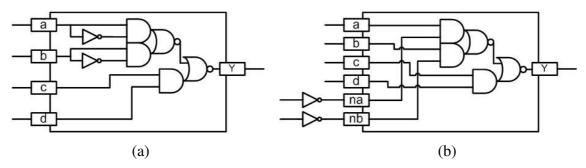

The virtual cell libraries also have a finite number of cells. This number is limited by a set of constraints that represent characteristics of the virtual cells. These constraints can impose topological restrictions such as the maximum number of inputs. For example, consider a library restricted to 2-input cells. It results in the library in Figure 3.5.a. Usually, virtual library-based technology mapping uses the maximum number of series transistor to restrict the pull-up and pull-down planes of each cell. An example of library limited by two transistors in series in both planes is demonstrated in Figure 3.5.b. In this case, the library has only seven cells. Table 3.1 shows the size of the virtual libraries in terms of number of cells. It uses the maximum number of series transistors as constraint to limit the library. These values were calculated considering the CMOS CSP topology. Notice that after the limit of three series transistors the

number of cells is much bigger than a normal static library. For instance, the library (4,4) implements 3,503 distinguished Boolean functions (up to four serial transistors in both planes). This number grows exponentially when increasing the number of serial transistors.

The matching and covering methods used by the traditional technology mappers cannot be applied to virtual libraries since the number of patterns is far too large. A structural/Boolean matching method, which compares the Boolean function of the cells in the library with subfunctions of the circuit representation, operates by choosing a covering that is the best solution over all possible matchings. Therefore, if the number of patterns/cells is large then more comparisons would be necessary, increasing the execution time. Virtual cell libraries do not have patterns for cell representation. There are methods, for example, to calculate the number of serial transistors of a sub-graph of the circuit representation. It is enough to know if the calculated result fits in a set of constraints. Hence, there is no need of a pattern matching algorithm.

a) up to 2-inputs

b) up to 2 serial transistors

Figure 3.5: Virtual library examples.

| Table 3.1: The size of CMOS CSP cell libraries induced by the number of serial |

|--------------------------------------------------------------------------------|

| transistors.                                                                   |

| PU / PD                 | 1 | 2   | 3     | 4       | 5         | 6           |  |

|-------------------------|---|-----|-------|---------|-----------|-------------|--|

| 1                       | 1 | 2   | 3     | 4       | 5         | 6           |  |

| 2                       | 2 | 7   | 18    | 42      | 90        | 186         |  |

| 3                       | 3 | 18  | 87    | 396     | 1,677     | 6,877       |  |

| 4                       | 4 | 42  | 396   | 3,503   | 28,435    | 222,913     |  |

| 5                       | 5 | 90  | 1,677 | 28,435  | 425,803   | 6,084,393   |  |

| 6                       | 6 | 186 | 6,877 | 222,913 | 6,084,393 | 154,793,519 |  |

| Source: (SECHEN, 1996). |   |     |       |         |           |             |  |

Clearly, both the quality of the mapped circuit and the CPU time are related to the size of the library. The main barrier of the virtual library approach is the dependency on a good layout generator and the lack of accurate information about the cell behavior. Due to this, the static precharacterized libraries are still popular in the industry. Currently, there are layout synthesis tools able to automatically generate layout for arbitrary complex gates more accurately and efficiently. The big problem is to find good models to estimate area, timing and power on demand. In this sense, some estimative models have been proposed such as the leakage power estimation method introduced by Butzen (2008).

#### 3.2 Subject graphs

All technology mapping methods are performed over a circuit representation that is called subject graph. Digital circuits can be represented in many ways through different kinds of data structures. Each algorithm uses a well defined structure according to the criteria that will be explored during the technology mapping process. The evolution of the technology mapping algorithms is strongly related to their different subject graph types.

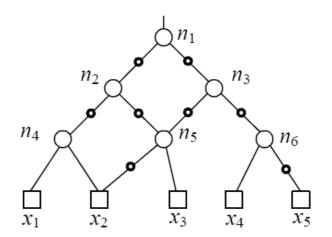

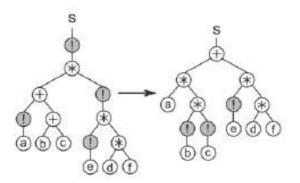

The first technology mapping methods used logical operator trees to represent parts of a circuit. Several import methods found in the literature, including more recent approaches, use this kind of subject graph (KEUTZER, 1987-a) (DETJENS, 1987) (ABOUZEID, 1992) (MAILHOT, 1993) (LIEN, 1992) (LEHMAN, 1997) (REIS, 1999) (ZHAO, 2001) (CORREIA, 2004). The operator trees are very simple data structures, and they are usually used to represent logic cones of a circuit. Therefore, algorithms that use these structures can only find optimal solutions for each part of the represented circuit.

The Binary Decision Diagrams are also used as subject graphs in some technology mapping approaches. There are different types of BDDs, and each one of them has a particular property. The TSBDDs were used in (REIS, 1998) to map circuits with CMOS CSP gates. Some methods, such as the methods presented by Yamashita (1997) and Jiang (2001), use ROBDDs to map circuits to PTL cells. A recent method proposed by Rosa (2006) describes techniques to generate gates in different topologies, including NCSP gates.

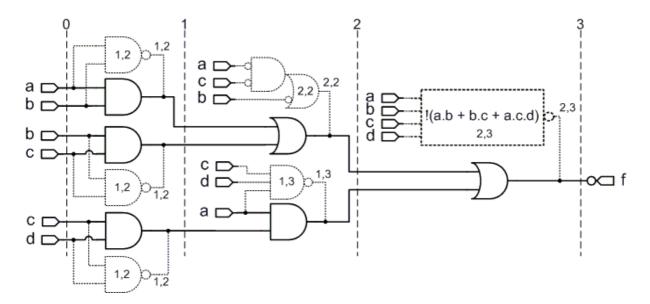

Other methods, such as (KUKIMOTO, 1998) (STOK, 1999) (MISHCHENKO, 2005), are based on DAGs, or similar data structures, that provide a full representation of the circuit. This kind of representation does not impose limits to the boundaries of the logic cones. This way, optimal solutions can have matches that cross nets with multiple fanout.

As discussed above, each technology mapping method uses a well defined subject graph. Generally, it determines the main characteristics of the algorithm and its application. The memory consumption to store the circuit and its matches will depend on the subject graph type. Therefore, the choice of the subject graph can determine the success of a technology mapping algorithm.

#### 3.3 Conventional technology mapping

As mentioned in the beginning of this chapter, the technology mapping chooses a set of logic gates to implement a circuit in a given technology. This set of cells is defined aiming the minimization of an objective function, and it is not an easy task. The majority of the algorithms reduce the technology mapping problem by handling smaller parts of the circuit. Therefore, the result can be (locally) minimal, but generally it does not correspond to global minimal costs. The most conventional approach of technology mapping can be described as a three step procedure: technology decomposition, matching phase and covering phase. The most common methods have trees as subject description. This way, an additional step is required right before the technology decomposition. The initial graph must be partitioned into trees. Next section describes the technology mapping using tree-based approaches.

#### 3.3.1 Graph partitioning

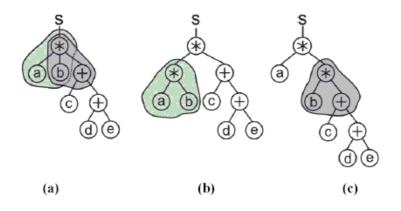

In order to apply the tree-based technology mapping, the graph must be converted in a forest of trees. It can be done by breaking the graph at each multiplefanout point. Each node with fanout greater than one becomes the root of a tree, and fanout of this node becomes a leaf-node of another tree. Thus, this technique does not duplicate nodes in the graph. An example of partitioning is demonstrated in Figure 3.6.

Figure 3.6: Graph partitioning.

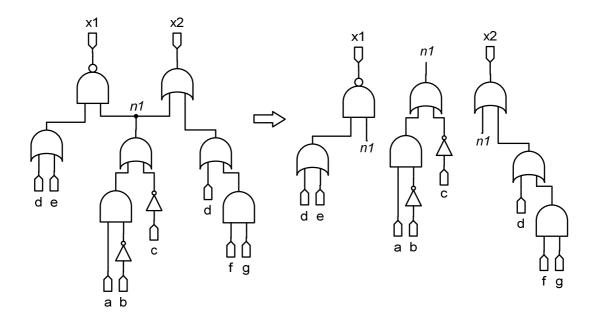

#### 3.3.2 Technology decomposition

The technology decomposition phase translates the graph representation into a subject graph decomposed in simple logic primitives. Any complex gate representation is replaced by a set of primitives normally composed of AND, OR and NOT operators or only AND and NOT operators. The main purpose of this step is to facilitate the matching algorithm task and to increase the graph granularity. The graph is decomposed using the same primitives in which the patterns of the cell in the library are represented. Therefore, the matcher can compare the circuit sub-graphs to the pattern graphs. Figure 3.7 shows an example of technology decomposition in the tree rooted by the node n1. Three different decompositions are shown. In the first one, the subject graph is expressed by AND, OR and NOT operators. All OR nodes can be replaced by a set of AND and NOT nodes in order to reduced the number of distinguished nodes. This is demonstrated in the second subject graph/tree (from left to right). As a last step, another

trick can be used to increase the granularity of the subject graph. A pair of inverter nodes can be added at each input that is not connected to NOT nodes.

Figure 3.7: Technology decomposition.

#### 3.3.3 Matching phase

This step consists in establishing the initial set of candidate matches attempting to match each node of the graph against each pattern of the library. If there are ppatterns in the library and n nodes in the subject graph, then this naive approach has complexity  $O(n \cdot p)$ . Structural matchers look for patterns and sub-graphs that are structurally isomorphic. Some approaches reduce the tree matching problem to the string matching problem. It is possible to find all of the strings that match a given string in time proportional to the length of the longest string in the pattern set. Boolean matchers identify patterns independently of the graph structure. There are several approaches for functional matchers that usually give better results than the structural matchers. However, these methods are expensive in terms of CPU time. Most of them have a limited search space containing Boolean functions with support up to 10 variables.

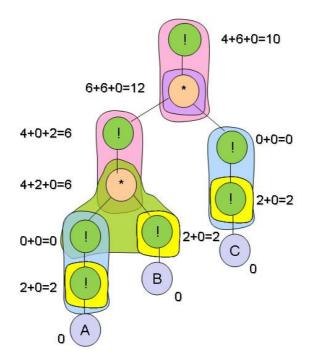

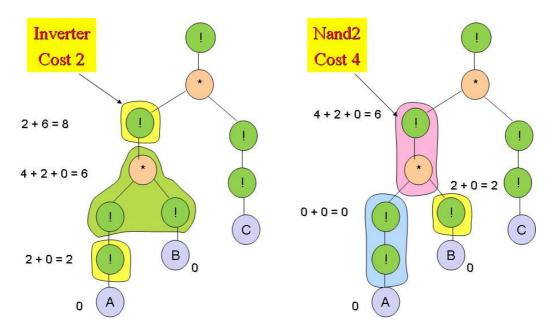

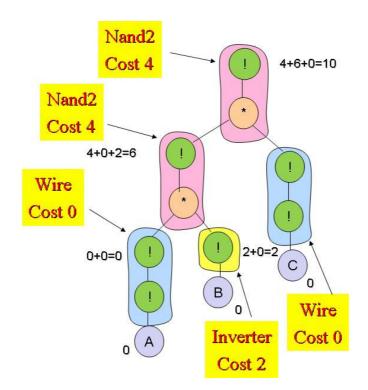

The result of the matching phase is illustrated through Figure 3.8. The subject graph of Figure 3.8 was matched against the library of Figure 3.2. Only the best matches for each node are bound in the graph. All cumulative costs are also shown in Figure 3.8, considering all possible matches.

Figure 3.8: Matching generation.

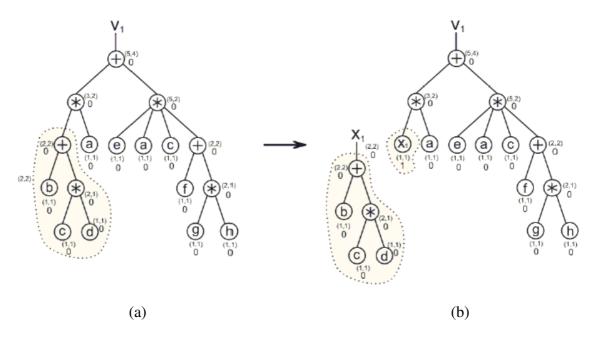

## 3.3.4 Covering phase

The last step of technology mapping is the covering phase. This procedure finds the optimal set of cells for final circuit implementation. Dynamic programming is a general technique for many algorithms which can be applied to the covering problem.

Consider the problem of finding a minimum area cover for a subject tree T. A scalar cost is assigned to each tree pattern, and the cost for a cover is the sum of costs for each pattern in the cover. The minimum-area cover for a tree T can be derived from the minimum-area covers for every node below the root of T. This is the principle of optimality for tree covering and is used as follows to find an optimal cover for T. For every match at the root of the tree the cost of an optimal cover containing that match equals the sum of the cost of the corresponding gate and the sum of the costs of the optimal covers for the nodes which are inputs to the match. For instance, consider the possible covers shown in Figure 3.9. The tree in the right side of the figure represents the minimal cover.

Note that each node in the tree is visited only once through a depth-first search algorithm. It is not necessary to re-compute the optimal cover for each input of each match. Hence, the complexity of this algorithm is proportional to the number of nodes in the subject tree times the maximum number of matches at any node in the subject tree. As result the covering algorithm has linear complexity in the size of the subject tree, and the memory requirements are also linear in the size of the subject tree. The optimal cover of each matched tree is presented in Figure 3.10. Its total cumulative cost is 10.

Figure 3.9: Calculating cost on the subject graph.

Figure 3.10: Tree covering result.

# 3.4 Technology mapping for standard cell libraries

This section reviews some of the main methods for technology mapping based on static precharacterized cell libraries, analyzing how they handle the technology mapping problem, the subject graphs and the objective functions. First, it starts with the first technology mapping method that was presented by Keutzer (1987-a). After, the methods of Kukimoto (1998), Stok (1999) and Mishchenko (2005) are reviewed.

#### 3.4.1 Keutzer (1987-a) – DAGON

The first technology mapping algorithm was presented by Keutzer (1987-a). He has found a relationship between technology mapping and programming language compiler techniques. More specifically, matching graph patterns of a technology independent circuit representation against a library of patterns, such as standard cell libraries, is similar to matching graph patterns of intermediate representations of a computer program against the patterns of an instruction set of a given machine.

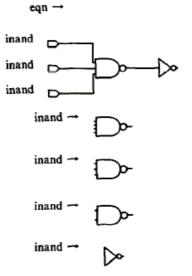

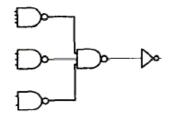

The result is an algorithm for technology mapping, called DAGON, which is able to minimize area, timing or a function of both. The initial description of a circuit is represented by a DAG. This graph is partitioned into a forest of trees that represents all logic cones of the circuit. Each sub-tree of the forest is matched against the library of patterns that are equivalent to technology cells. The tree matching is made by an external tool called *twig* (TJIANG, 1986). This tool was generally used to construct code generators for programming language compilers. This tool needs to be fed with list of patterns that are matched against circuit trees. The pattern list is composed by small trees in the canonical NAND/NOT form. The developers of the patterns are responsible for providing the cost of each one of them. Therefore, given a tree to be matched, the *twig* tool uses these costs to evaluate cost of candidate matches. Once the matches and their costs are bound in the circuit tree, the covering algorithm can select the patterns/cells that will cover the tree/circuit with minimal cost. The whole DAGON mapping flow is summarized by the Figure 3.11.

Figure 3.11: DAGON algorithm flow (KEUTZER, 1987-a).

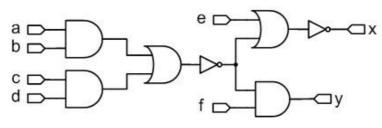

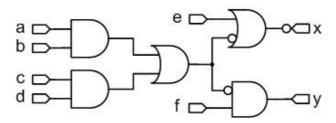

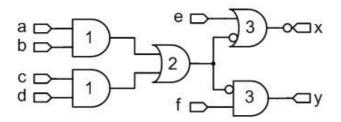

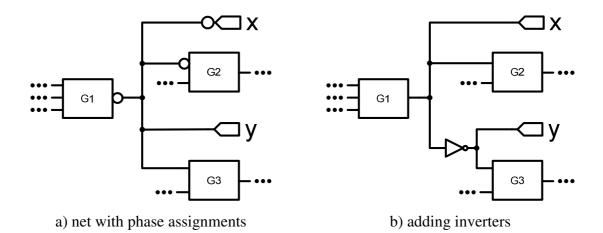

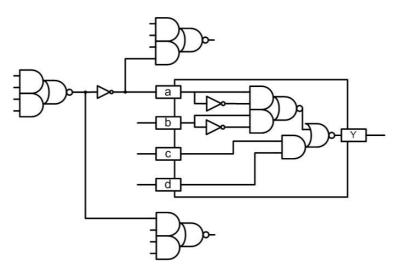

Keutzer gives an example of a set of five patterns for AND-OR-INVERTER (AOI) gates. These patterns can be seen in Figure 3.12. They actually describe sixty-four unique pattern instances from an AOI444 to AOI211. Many of these patterns are symmetric, thus an AOI114 is equivalent to an AOI411. A graphical representation of the set of trees described by these patterns is given in Figure 3.13. Comparing the current cell library descriptions (refer to Figure 3.3) against the library of patterns, we can see that it is a very rudimentary description. It can only describe a single cost value for each pattern while the most recent descriptions are able to describe different costs, even for each cell pin.

Since it uses the tree covering approach, optimal solutions can be found in linear time. The main disadvantage of this method is the size of the library, which is very limited. Moreover, it does not achieve good results regarding timing optimizations since it is a tree based mapping.

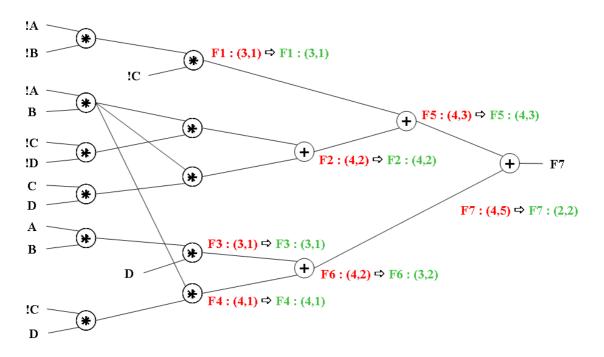

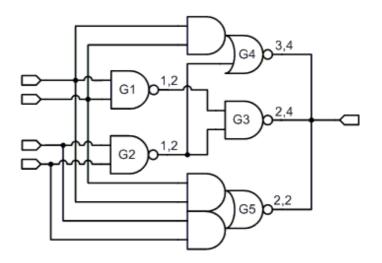

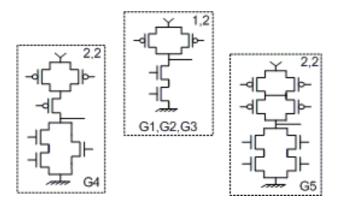

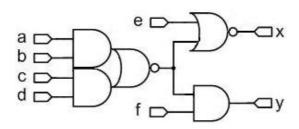

> /\*\*\*\* AOIxxx canonically expressed as not 1 nand\_3 : 1 . nand nand nand \*/ eqn: not(nand 3(inand, inand, inand)) /\*\$\$ refers to the root of the pattern\*/ DEFAULT COST; /\*sum up cost of children\*/ cost.cost\_a[AREA]+=d\_get\_aoi\_area\_cost(\$\$); cost.cost\_a[TIME]+=d\_aoi\_time\_cost(\$\$) cost.cost\_a[AT\_K] += my\_pow(cost.cost a[TIME],cost power) \*cost.cost\_a[AREA]; 3 = { d\_print\_aoi(stdout,\$\$); **}**: inand: nand\_2(eqn,eqn)