## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

SIMONE BAVARESCO

## **On-Silicon Testbench for Validation of Soft** Logic Cell Libraries

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science.

Prof. Dr. Renato Perez Ribas Advisor

Prof. Dr. André Inácio Reis Co-advisor

Porto Alegre, February 2008.

# Livros Grátis

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

### CIP – CATALOGAÇÃO NA PUBLICAÇÃO

Bavaresco, Simone

On-Silicon Testbenh for Validation of Soft Logic Cell Libraries / Simone Bavaresco – Porto Alegre: Programa de Pós-Graduação em Computação, 2008.

15 f.:il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2008. Advisor: Renato Perez Ribas; Co-advisor: André Inácio Reis.

1.Integrated circuit 2.ASIC 3.Digital design 4.Standard cell 5.Library-free technology mapping 6.Soft library 7.Test circuit. I. Ribas, Renato Perez. II. Reis, André Inácio. III. Title.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. José Carlos Ferraz Hennemann Vice-reitor: Prof. Pedro Cezar Dutra Fonseca Pró-Reitora Adjunta de Pós-Graduação: Profa. Valquiria Linck Bassani Diretor do Instituto de Informática: Prof. Philippe Olivier Alexandre Navaux Coordenador do PPGC: Prof. Flávio Rech Wagner Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## ACKNOWLEDGEMENTS

This dissertation is dedicated to the memory of my mother-in-law, Gioconda Madalena Loëblein. In the beginning I was a stranger and even though she helped me and gave me all comfort. She encouraged me in this study and over the last five years she supported me with her love and caring. To get on with her during these years gave me a new appreciation for the meaning and importance of family and friends. She faced her death bravely. Her example and will power kept me working when I wanted to give up.

I would like to express my deepest gratitude to my advisors, Renato Perez Ribas and André Inácio Reis for their excellent guidance, caring, patience, and providing me with an excellent atmosphere for doing research. Especially I would like to thank Renato for urged me by providing critical assistance when all seemed dark and guided me when the project seemed endless.

I would like to thank Nangate for financial support and thank all the staff, in particular, my colleagues from Nangate Lab Research, Caio Alegretti, Mateus Gomes, Leomar da Rosa, Carlos Afonso da Silva, Digeorgia Silva, Paulo Butzen, Felipe Marques and Tiago Cardoso. They were always willing to help and give their best suggestions.

There are many other people who contributed to this dissertation in many ways. My sincere gratitude goes to all my friends, especially José Francisco Szücs, Laura Ghia, Cleber Ughini and Sílvia Osório, who have contributed to my emotional and spiritual well-being over this time. I would like to thank for their love, inspiration and support.

I would also like to thank my parents, my brother, my sisters and brothers-in-law. They were always supporting me and encouraging me with their best wishes.

Finally, I would like to thank my husband, João Daniel Togni, for his support, encouragement, love and caring. He was always there cheering me up and stood by me through the good times and bad. His knowledge, valuable ideas and useful suggestions were also extremely helpful.

## TABLE OF CONTENTS

| LIST  | OF ABBREVIATIONS                                   | 6  |

|-------|----------------------------------------------------|----|

| LIST  | OF FIGURES                                         |    |

| LIST  | OF TABLES                                          | 10 |

| ABST  | TRACT                                              |    |

| RESU  | J <b>MO</b>                                        | 12 |

| 1     | INTRODUCTION                                       |    |

| 2     | BACKGROUND & MOTIVATION                            |    |

| 2.1   | ASIC Flow                                          |    |

| 2.2   | Design Styles                                      | 20 |

| 2.3   | Testing                                            |    |

| 2.3.1 | Defect, fault, failure and error                   |    |

| 2.3.2 | Test Generation, Functional and Structural Testing |    |

| 2.3.3 | Fault models                                       |    |

| 2.4   | Delay test verification                            |    |

| 2.4.1 | Characterization                                   | 25 |

| 2.4.2 | Delay fault testing                                |    |

| 2.5   | Testability and Design-for-Testability             |    |

| 2.6   | How to test a library?                             |    |

| 3     | COMBINATIONAL BLOCK                                | 29 |

| 3.1   | First stage                                        |    |

| 3.1.1 | Implementation                                     |    |

| 3.1.2 | Sample block                                       | 35 |

| 3.2   | Second stage                                       |    |

| 3.3   | Combinational blocks stage analysis                | 40 |

| 3.3.1 | First stage analysis                               | 40 |

| 3.3.2 | Second stage analysis                              | 46 |

| 3.4   | Last considerations                                | 48 |

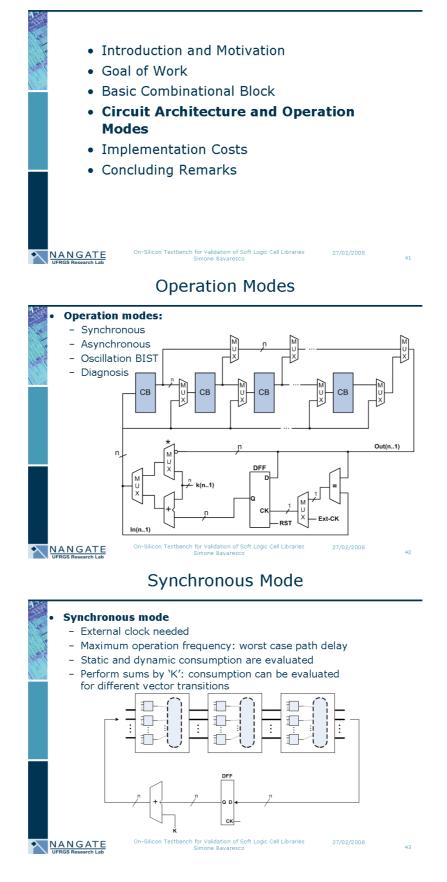

| 4     | CIRCUIT ARCHITECTURE AND OPERATION MODES           | 49 |

| 4.1   | Circuit Architecture                                                                                    | 49  |

|-------|---------------------------------------------------------------------------------------------------------|-----|

| 4.2   | Operation Modes                                                                                         | 51  |

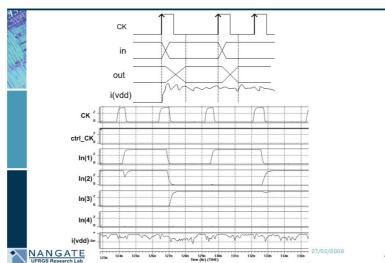

| 4.2.1 | Synchronous Mode                                                                                        | 51  |

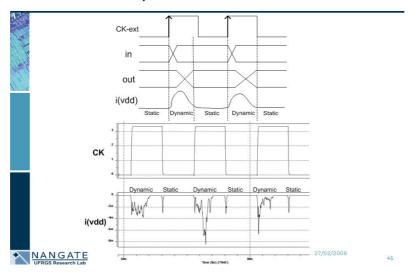

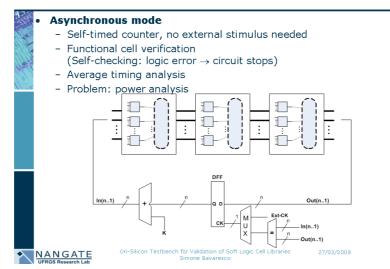

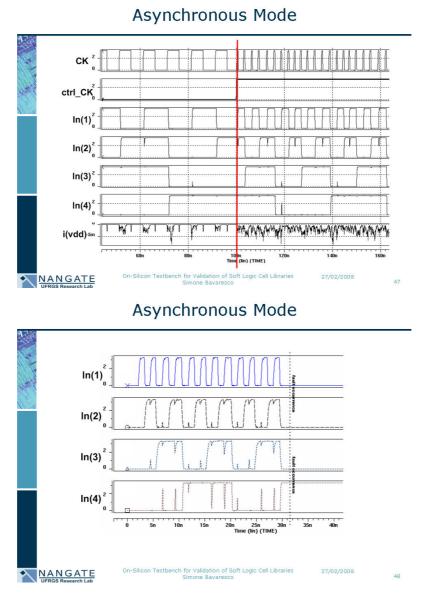

| 4.2.2 | Asynchronous Mode                                                                                       | 53  |

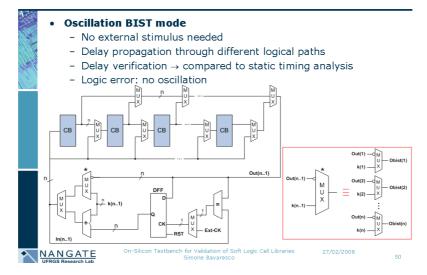

| 4.2.3 | Digital OBIST Mode                                                                                      | 56  |

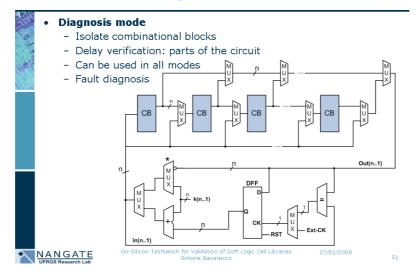

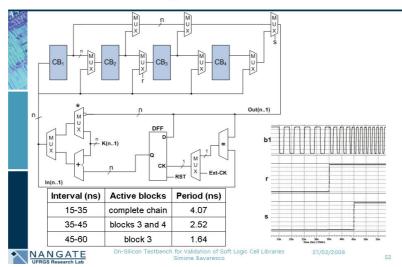

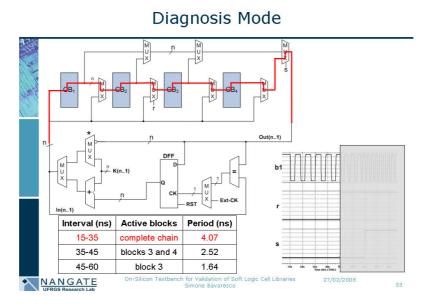

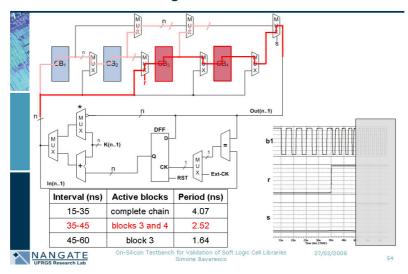

| 4.2.4 | Diagnosis Mode                                                                                          | 60  |

| 4.3   | Overhead Analysis                                                                                       | 61  |

| 5     | CONCLUSIONS                                                                                             | 64  |

| REFE  | RENCES                                                                                                  | 66  |

|       | NDIX A Circuito de teste EM SILÍCIO PARA VALIDAÇÃO DE<br>OTECAS DE CÉLULAS LÓGICAS geradas por software | 70  |

| APPE  | NDIX B Work presentation                                                                                | 78  |

| APPE  | NDIX C Paper submited to ITC'08                                                                         | 101 |

## LIST OF ABBREVIATIONS

| ASIC          | Application Specific Integrated Circuit               |

|---------------|-------------------------------------------------------|

| BIST          | Built-In Self-Test                                    |

| CAD           | Computer-Aided Design                                 |

| CMOS          | Complementary metal-oxide-semiconductor               |

| CUT           | Circuit Under Test                                    |

| DFT           | Design For Testability                                |

| EDA           | Electronic design automation                          |

| FPGAs         | Field Programmable Gate Array                         |

| HDL           | Hardware Description Language                         |

| IC            | Integrated Circuit                                    |

| IP            | Intellectual Property                                 |

| IPO           | In Place Optimization                                 |

| ISCAS         | International Symposium on Circuits and Systems       |

| ITC           | International Test Conference                         |

| IWLS          | International Workshop on Logic and Synthesis         |

| MCNC          | Microelectronics Center of North Carolina             |

| MOS           | Metal-Oxide-Semiconductor                             |

| MPGA          | Metal Programmable Gate Array                         |

| N-equivalent  | equivalent under input Negation                       |

| NP-equivalent | equivalent under input Negation and input Permutation |

| NRE           | Non-Recurring Engineering                             |

| NBTI          | Negative-Bias Temperature Instability                 |

| OBIST         | Oscillation Built-In Self Test                        |

| P-equivalent  | equivalent under input Permutation                    |

| RTL           | Register Transfer Level                               |

| SA            | Stuck-At                                              |

| SoC           | System-on-Chip                                        |

| SPICE         | Simulation Program with Integrated Circuit Emphasis   |

|               |                                                       |

| STA   | Static Timing Analysis                    |

|-------|-------------------------------------------|

| UFRGS | Universidade Federal do Rio Grande do Sul |

| VHDL  | VHSIC Hardware Description Language       |

| VHSIC | Very High-Speed Integrated Circuits       |

| VLSI  | Very Large-Scale Integration              |

|       |                                           |

## LIST OF FIGURES

| Figure 2.1: Levels of design abstraction (GAJSKI, 1988).                                                                                                                    | 18 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2: ASIC design flow diagram (WESTE, 2005) (MARQUES, 2007a)                                                                                                         | 19 |

| Figure 2.3: Overview of IC design styles (MICHELI, 1994) (RABAEY, 2003)                                                                                                     | 20 |

| Figure 2.4: ASIC design flow with library-based technology mapping (MARQUES, 2007).                                                                                         | 22 |

| Figure 2.5: ASIC design flow with library-free technology mapping (MARQUES, 2007).                                                                                          | 22 |

| Figure 2.6: Delay fault testing.                                                                                                                                            | 27 |

| Figure 3.1: Combinational block illustration                                                                                                                                | 29 |

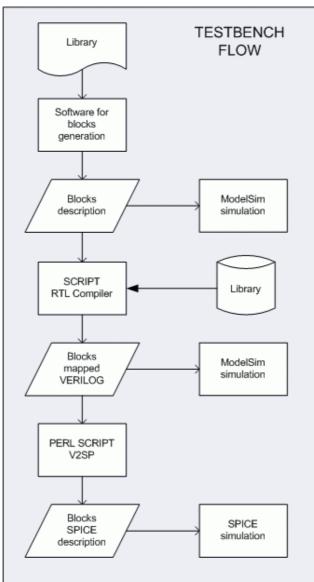

| Figure 3.2: Testbench flow                                                                                                                                                  | 34 |

| Figure 3.3: Sample block                                                                                                                                                    | 35 |

| Figure 3.4: Combinational block with 'check' signal.                                                                                                                        | 38 |

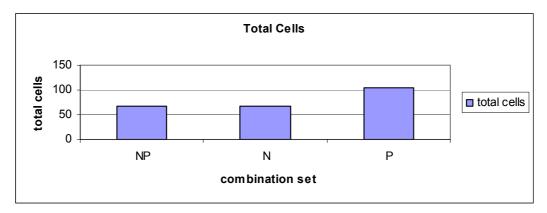

| Figure 3.5: Total cells / combination set.                                                                                                                                  | 42 |

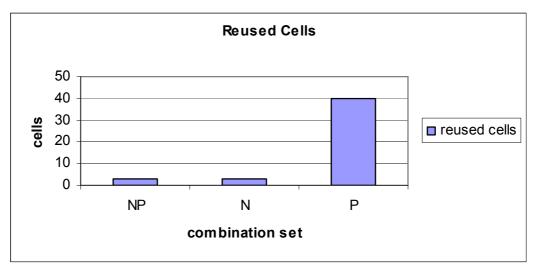

| Figure 3.6: Reused cells / combination set                                                                                                                                  | 43 |

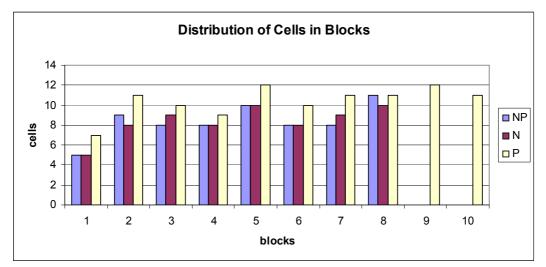

| Figure 3.7: Distribution of cells in blocks.                                                                                                                                | 43 |

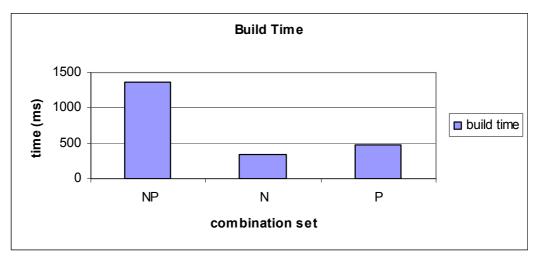

| Figure 3.8: Build time / combination set.                                                                                                                                   | 44 |

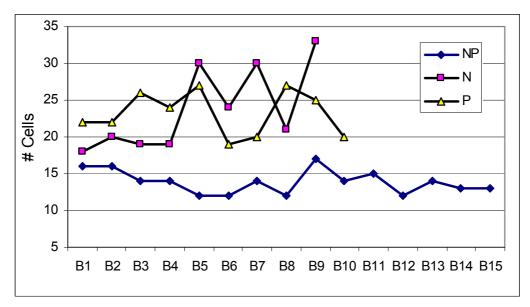

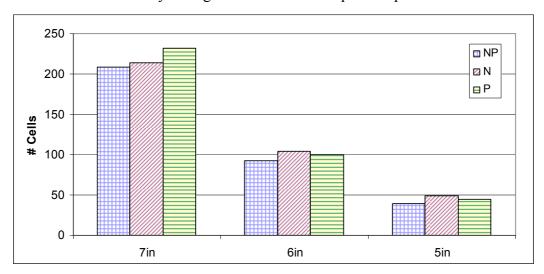

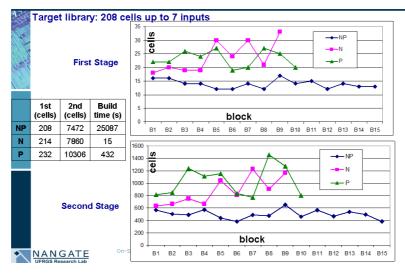

| Figure 3.9: Number of cells per block (first stage) for the combination set using the library 44-6.genlib with 208 cells up to 7 inputs                                     | 44 |

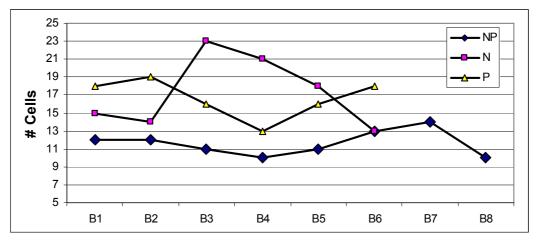

| Figure 3.10: Number of cells per block (first stage) for the combination set using the library 44-6.genlib with 92 cells up to 6 inputs                                     | 45 |

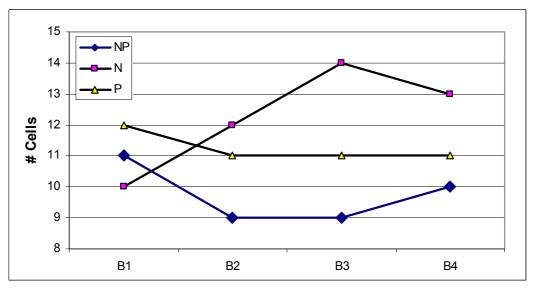

| Figure 3.11: Number of cells per block (first stage) for the combination set using the library 44-6.genlib with 38 cells up to 5 inputs                                     |    |

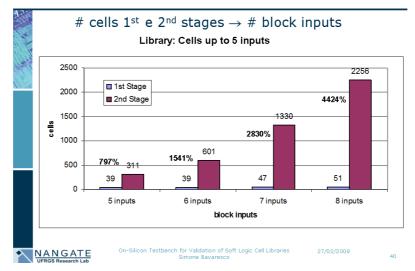

| Figure 3.12: Total cells in the first stage considering the combination set for libraries with different maximum number of cell inputs.                                     | 45 |

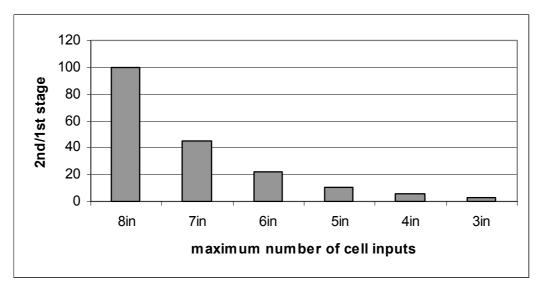

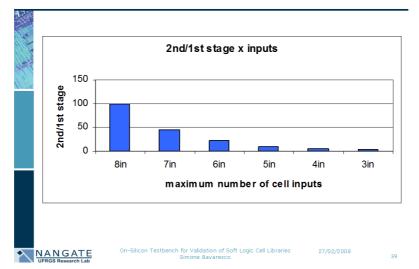

| Figure 3.13: Area overhead measurements: 2nd / 1st stage, versus number of cell inpu                                                                                        |    |

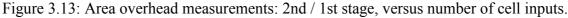

| Figure 3.14: Number of cells used in the 1 <sup>st</sup> and 2 <sup>nd</sup> stages for different number of bloc inputs using library 44-6.genlib (16 cells up to 4 inputs) |    |

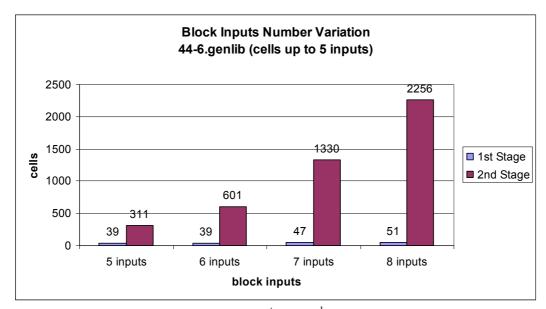

| Figure 3.15: Number of cells used in the 1 <sup>st</sup> and 2 <sup>nd</sup> stages for different number of bloc inputs using library 44-6.genlib (38 cells up to 5 inputs) |    |

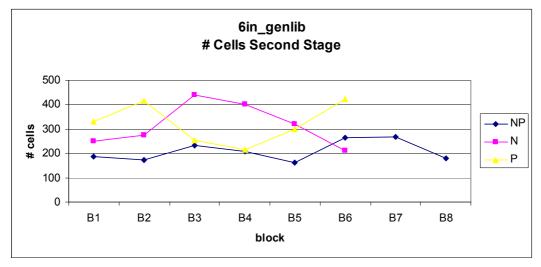

| Figure 3.16: Number of cells per block (second stage) for the combination set using the library 44-6.genlib with 92 cells up to 6 inputs.  |      |

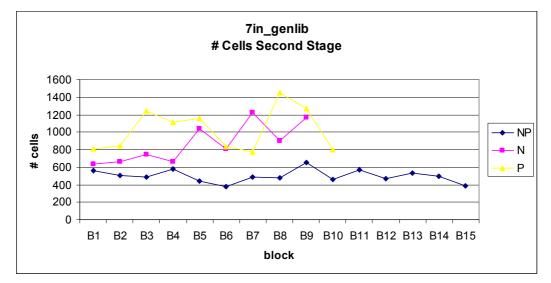

|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.17: Number of cells per block (second stage) for the combination set using the library 44-6.genlib with 208 cells up to 7 inputs. |      |

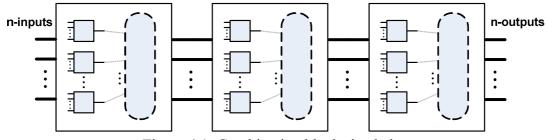

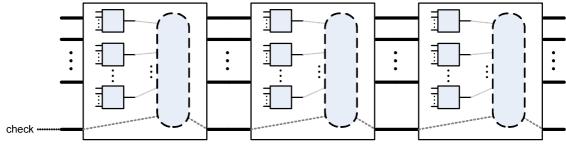

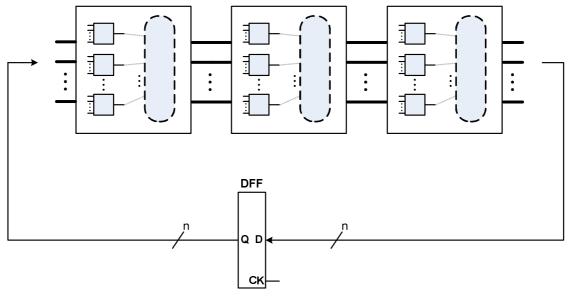

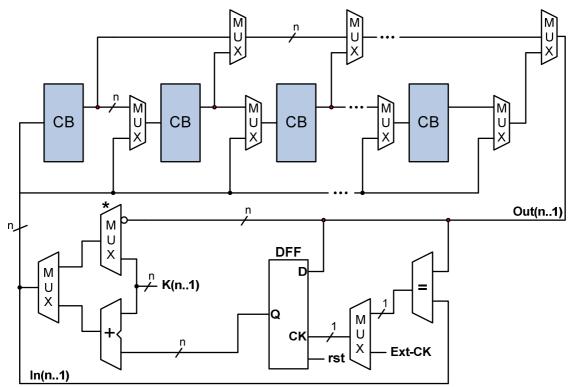

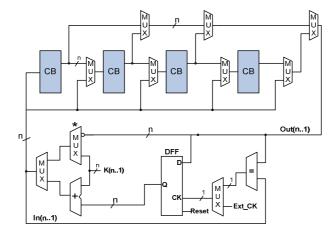

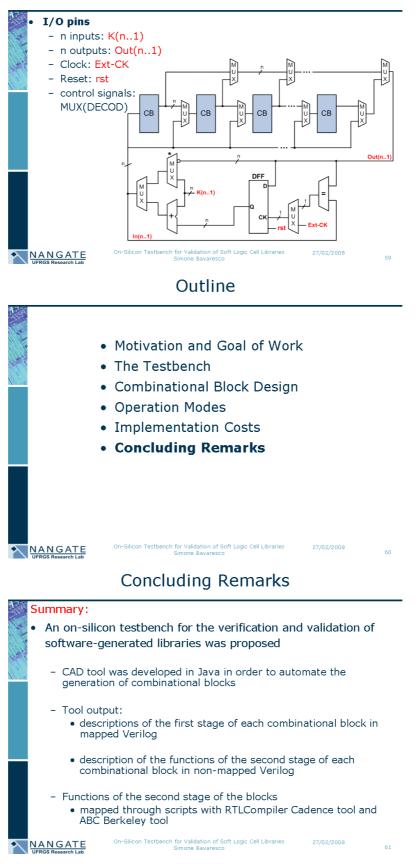

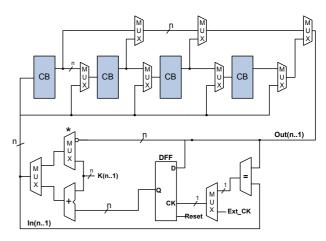

| Figure 4.1: Combination blocks in chain                                                                                                    | . 49 |

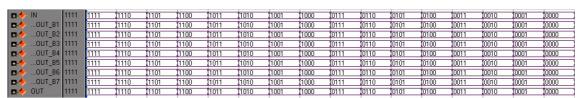

| Figure 4.2: Simulation of combination blocks in chain.                                                                                     | 50   |

| Figure 4.3: Combination blocks in chain with 'check signal'                                                                                | . 50 |

| Figure 4.4: Combination blocks with flip-flop barrier.                                                                                     | . 50 |

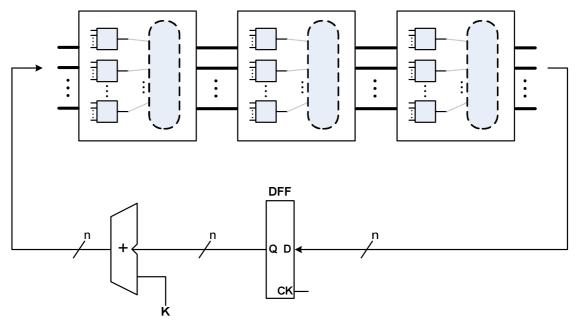

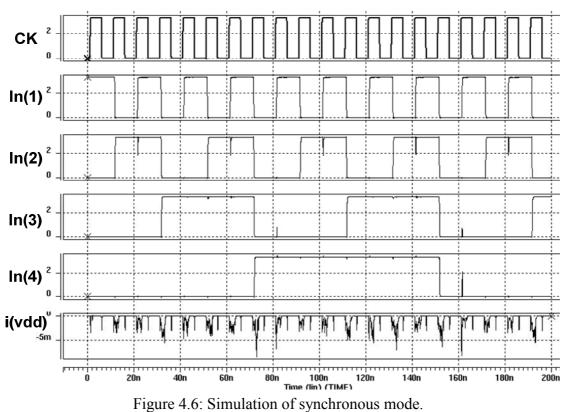

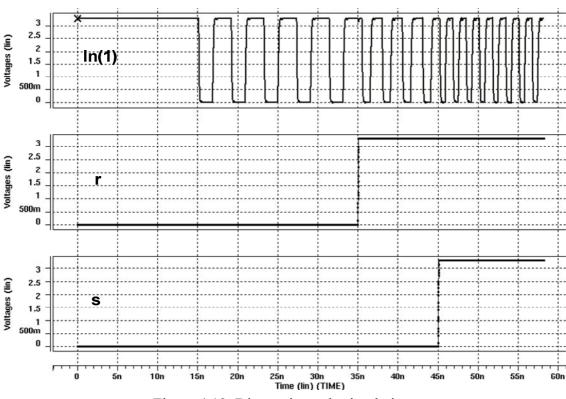

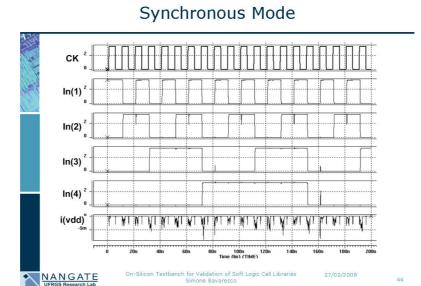

| Figure 4.6: Simulation of synchronous mode                                                                                                 | . 52 |

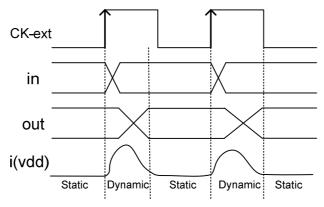

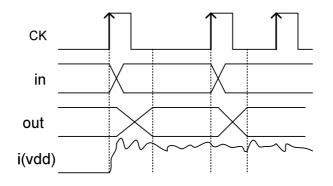

| Figure 4.7: Power consumption in synchronous mode.                                                                                         | . 52 |

| Figure 4.8: Power consumption in the synchronous mode simulation                                                                           | . 53 |

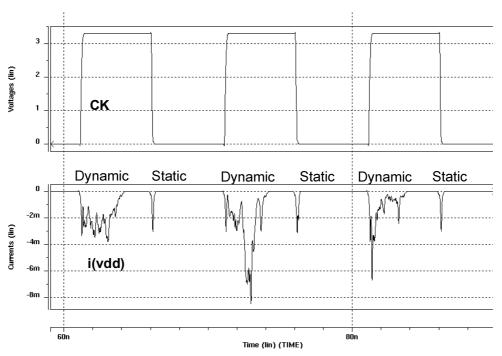

| Figure 4.9: Asynchronous mode                                                                                                              | . 54 |

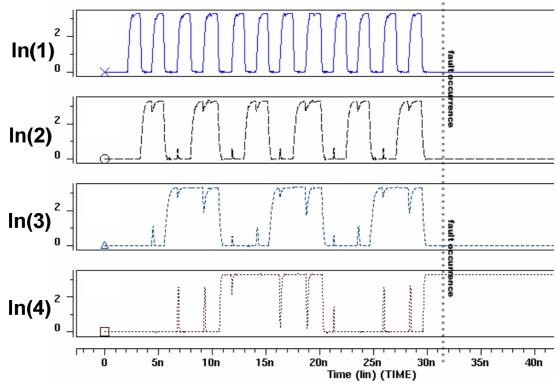

| Figure 4.10: Simulation of synchronous and asynchronous mode                                                                               | . 54 |

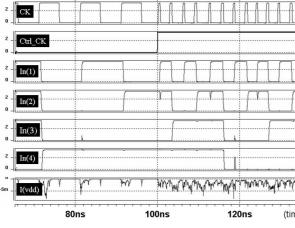

| Figure 4.11: Electrical simulation of fault occurrence during the self-timed counting                                                      | . 55 |

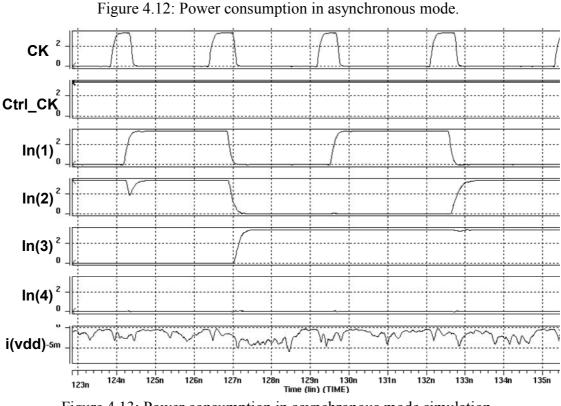

| Figure 4.12: Power consumption in asynchronous mode                                                                                        | . 56 |

| Figure 4.13: Power consumption in asynchronous mode simulation                                                                             | . 56 |

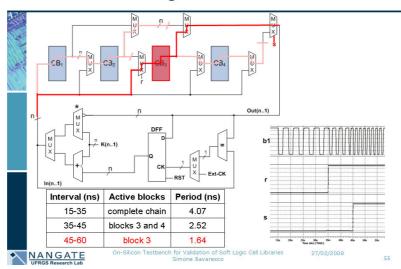

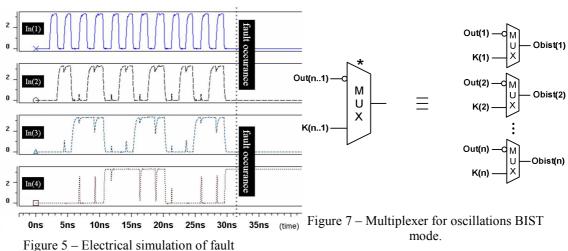

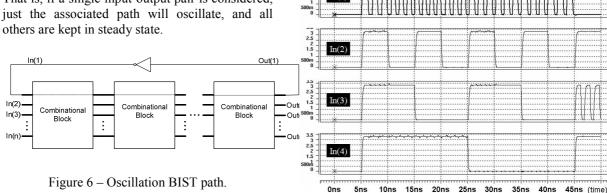

| Figure 4.14: Digital OBIST mode.                                                                                                           | . 58 |

| Figure 4.15: Multiplexer for oscillations BIST mode.                                                                                       | . 58 |

| Figure 4.16: Oscillation BIST path.                                                                                                        | . 58 |

| Figure 4.17: Simulation of digital OBIST mode.                                                                                             | . 59 |

| Figure 4.18: Diagnosis mode                                                                                                                | . 60 |

| Figure 4.19: Diagnosis mode simulation                                                                                                     | . 61 |

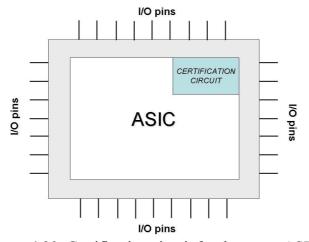

| Figure 4.20: Certification circuit for the target ASIC.                                                                                    | . 62 |

## LIST OF TABLES

| Table 1.1: Using a 64-cell library to synthesize benchmark circuits                                                                                       | 16 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1: Minimum number of cells at the first stage                                                                                                     | 31 |

| Table 3.2: Maximum number of cells at the first stage.                                                                                                    | 31 |

| Table 3.3: Number of combinations of the combination sets                                                                                                 | 33 |

| Table 3.4: Cells with their selected block and cell inputs combinations                                                                                   | 35 |

| Table 3.5: Sample block with 3 cells; C <sub>4</sub> with inputs<br>A1(IN[2]), A2(not_IN[3])) and C <sub>4</sub> with inputs<br>A1(IN[1]), A2(not_IN[3])) | 36 |

| Table 3.6: Block inputs, intermediate vectors and outputs                                                                                                 | 37 |

| Table 3.7: Second stage functions.                                                                                                                        | 37 |

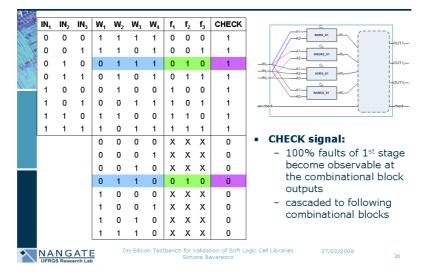

| Table 3.8: Truth table used to synthesize the second stage of a combinational block                                                                       | 39 |

| Table 3.9: Number of combinations tested using NP configuration.                                                                                          | 40 |

| Table 3.10: NP configuration report for the set of 64 cells.                                                                                              | 41 |

| Table 3.11: Number of combinations tested using N configuration                                                                                           | 41 |

| Table 3.12: N configuration report for the set of 64 cells.                                                                                               | 41 |

| Table 3.13: Number of combinations tested using P configuration.                                                                                          | 42 |

| Table 3.14: P configuration report for the set of 64 cells.                                                                                               | 42 |

| Table 4.1: Data of the OBIST mode simulation                                                                                                              | 60 |

| Table 4.2: Data of the diagnosis mode simulation.                                                                                                         | 61 |

## ABSTRACT

Cell-based design is the most applied approach in the ASIC market today. This design approach implies re-using pre-customized cell libraries to build more complex digital systems. Therefore the ASIC design efficiency turns to be bounded by the library in use. The use of automatically generated CMOS logic gates in standard cell IC design flow represents an attractive perspective for ASIC design quality improvement. These soft IPs (logic cells generated by software) are the key elements for the novelty library-free technology mapping, already proposed in literature and now being adopted by the industry. Library-free technology mapping approach, based on the on-the-fly creation of cells, by software, can provide flexibility to IC designers providing an optimized fit in a particular application. However, such approach represents an IC design flow based on logic cells created on-the-fly by software which have not been previously validated in silicon yet, until the target ASIC is prototyped.

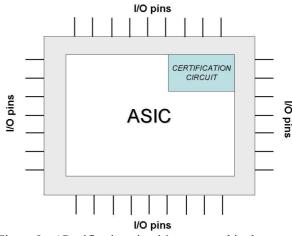

In this work, a specific test circuit (testbench) is proposed to validate the full functionality of a set of logic cells, as well as to verify timing and power consumption behaviors, which can be correlated with design timing and power estimations in order to validate the cell data provided by electrical characterization. The proposed architecture for the test circuit is composed by combinational blocks that ensure full logic verification of every library cell. The basic architecture of the test circuit is slightly modified to allow different operating modes which provide distinct data evaluation using SPICE electrical simulations. Since this test circuit brings little silicon overhead to the final design, it can be implemented together with the target ASIC acting as a 'library certification circuit'.

**Keywords:** Integrated circuit, ASIC, digital design, standard cell, library-free technology mapping, soft library, test circuit

### **RESUMO**

Projeto baseado em células-padrão é a abordagem mais aplicada no mercado de ASIC atualmente. Essa abordagem de projeto consiste no reuso de bibliotecas de células pré-customizadas para gerar sistemas digitais mais complexos. Portanto a eficiência de um projeto ASIC está relacionado com a biblioteca em uso. A utilização de portas lógicas CMOS geradas automaticamente no fluxo de projeto de circuito integrado baseado em células-padrão representa uma perspectiva atraente para melhorar a qualidade de projeto ASIC. Essas células geradas por software são os elementos-chave dessa nova abordagem de mapeamento tecnológico livre de biblioteca, já proposto na literatura e agora adotado pela indústria. O mapeamento tecnológico livre de biblioteca, baseado na criação de células sob demanda, por software, gera flexibilidade aos projetistas de circuitos integrados, fornecendo ajuste otimizado em aplicações específicas. Contudo, tal abordagem representa um fluxo de projeto de circuito integrado são previamente validadas em silício até que o ASIC alvo seja prototipado.

Neste trabalho, um circuito de teste específico é proposto para validar a funcionalidade completa de um conjunto de células lógicas, bem como verificar comportamentos de atraso e consumo, os quais podem ser correlacionados com as estimativas de atraso e consumo do projeto, a fim de validar os dados das células gerados pela caracterização elétrica. A arquitetura proposta para o circuito de teste é composta por blocos combinacionais que garantem a completa verificação lógica de cada célula da biblioteca. A estrutura básica do circuito de teste é ligeiramente modificada para permitir diferentes modos de operação que permitem avaliação de diferentes dados utilizando simulações elétricas SPICE. Visto que o circuito de teste gera pequeno acréscimo de silício ao projeto final, ele pode ser implementado junto com o ASIC alvo, atuando como um 'circuito de certificação de biblioteca'.

**Palavras-Chave:** Circuito integrado, ASIC, projeto digital, célula-padrão, mapeamento tecnológico livre de biblioteca, biblioteca de células geradas por software, circuito de teste.

## **1 INTRODUCTION**

Microelectronics became the key technology of many industry branches like information technology, telecommunication, medical equipment and consumer electronics. The ability of microelectronics to process, transport and store data digitally made many new applications possible. The continuously increasing level of integration of electronic devices on a single substrate has led to the fabrication of increasingly complex systems. An *Integrated Circuit* (IC) is an electronic system consisting of a number of miniaturized electronic devices, such as transistors, resistors, capacitors and inductors, built on a monolithic semiconductor substrate. The large majority of the current ICs are implemented in the Metal-Oxide-Semiconductor (MOS) technology (WESTE, 2005) (RABAEY, 2003).

The integrated circuit technology has progressed tremendously. The increase in the number of transistors that can be integrated in a single die has grown exponentially in the last decades, as predicted by the so called *Moore's law* (INTEL, 2007) (MOORE, 1965). The level of integration of chips has been classified as small-scale (up to 10 gates –half a dozen transistors per gate), medium-scale (up to 1,000 gates), large-scale (up to 10,000) and *very large-scale integration* (VLSI). The term VLSI is used to describe most integrated circuits from the 1980s onward.

At present, many electronic systems require integrated and dedicated components that are specialized to perform a task or a limited set of tasks. These are called *Application Specific Integrated Circuits*, or ASICs.

*Electronic design automation* (EDA) is the category of tools for designing and producing electronic systems. This is sometimes referred to as CAD (*computer-aided design*). The modern ASIC design flow has evolved and increased in complexity just as the devices that are being designed have dramatically increased in complexity. This design flow is now heavily dependent on EDA tools and many of the tasks that were once carried out manually are now automated by EDA tools with little or no manual intervention.

Cell-based design is definitely the most applied approach in the ASIC market today. This design approach implies re-using pre-customized cell libraries to build more complex digital systems. A typical standard cell design environment includes timing and power analysis, as well as automatic generation of circuit layout. In standard cell libraries, three groups of logic cells co-exist: (1) inverters/buffers; (2) combinational and (3) sequential gates. Especially due to the large number of different logic functions and driving strength options needed in typical designs, the largest of the three aforementioned groups turns to be the combinational cells. The creation of handcrafted

standard cell libraries needs skilled designers and requires long development times, even when simply dealing with technology migration for the same set of cells. Each cell is carefully defined and characterized for different input slopes, output loads, and design corners. This practice usually limits the number of cells in libraries due to the high engineering costs involved.

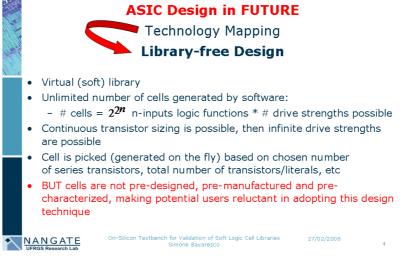

More recently, the library-free technology mapping has been addressed by EDA platforms (GAVRILOV, 1997). It automatically generates on-the-fly the cells required (or identified) by the mapping task. This new technology is based on virtual libraries, whose original cells are not previously designed and physically verified. It means that such virtual libraries are, in fact, tested together with the target ASIC.

Since in a standard IC design flow, the technology mapping is based on predesigned and pre-characterized cells, the ASIC design efficiency turns to be bounded by the library in use. The more cells and drive strength options are available, the larger is the variety of logic functions and circuit performances the designer can implement. Only a library-free technology mapping approach, capable of creating on-the-fly cells that perfectly fit a particular application, can provide such flexibility to IC designers (DEDOOD, 2003) (GAVRILOV, 1997) (KAGARIS, 2007) (MARQUES, 2007) (ROY, 2005) (SCHNEIDER, 2005). The enrichment of a library can be done by adding only new drive strengths (DEDOOD, 2003) or through the addition of new functions with standard series/parallel implementation (GAVRILOV, 1997) or with special transistor topologies (KAGARIS, 2007) (MARQUES, 2007) (SCHNEIDER, 2005) and adding new cells for in-place optimization combining new topology and IPO (in place optimization) sizing (ROY, 2005).

A cell library is usually an ensemble of hundreds of each individual cell. If it is going to function as a whole to provide building blocks for larger designs, not only should each individual cell be correctly designed, but also the synthesized designs based on these library cells should be absent from errors. However, designing a cell library requires carrying out many complex tasks and involving design efforts from a number of engineers. Errors are easily made in this situation. In order to uncover the leftover errors of a cell library, benchmark circuits are usually designed to fulfill this mission. Thus, the quality of a cell library can be substantially improved (LIN, 1999).

Without accurate library validation, ASIC customers cannot be assured that their design will perform to specifications using simulation results alone. The need to correlate simulation precisely to silicon demands the manufacturing, testing and characterization of test circuits specifically designed for that purpose.

In the past, designing of a cell library was usually thought as a discipline in industrial community where the advancement in cell library design is largely made. Since a viable cell library will strengthen a company's competitiveness, the know-how with regard to designing a high quality cell library is not often seen in open literature (AGASTEIN, 1990) (MARTINEZ, 1995) (SCOTT, 1994). However, with ever increasing availability of semiconductor foundry and commercial CAD tools to the university community and advancement in cell-based synthesis technology, more activities in cell library design within university community have been carried out (LIN, 1999) (CHONG, 1992).

There are certainly many interpretations for "high quality cell libraries". A cell library regarded as high quality by one company may not be considered as viable by another company. However, high quality cell libraries possess many common characteristics. Here are listed some of them (LIN, 1999):

- (1) the functionality of each individual cell should be correct in the models for logic synthesis and simulation,

- (2) the timing performance figures of each individual cell claimed in the data sheet or models should be accurate enough,

- (3) the layout of each cell should be free of design rule violations,

- (4) the cells should be best utilized by a synthesis tool, and

- (5) the cells should be able to optimize placement and route of a large design.

The testbench (test circuit) developed in this work enforces (1) and (2) which are essential to a high quality cell library.

The computing evolution, including parallel and distributed processing, allows nowadays the automatic generation and electrical characterization of a huge number of cells in a few minutes, although some design aspects like cell layout compaction are still challenging programmers. However, even if complete back-annotation and design verification are already feasible in a library-free approach, designers are sometimes still skeptical and reluctant to develop products based on software-generated cells that are not previously validated on silicon. This skepticism results from simple things like the lack of knowledge about the reliability of the circuit with respect to degradation due to electromigration (CHRISTIANSEN, 2006) and negative-bias temperature instability (NBTI) (KUMAR, 2007) effects.

The validation and physical characterization of the set of cells, included in a library, are usually done through specific structures and benchmark circuits. Such test structures are composed by ring oscillators, delay chains, counters, and others (LONG, 1984) (BHUSHAN, 2006). They are generally designed in full custom style, and must be carefully built for a specific process.

Benchmark circuits, such as ISCAS'89, MCNC'90, ITC'99 and IWLS'05 benchmarks, on the other hand, correspond to different applications and architectures in order to represent commercial circuits and system blocks, such as purely combinational circuits, finite state machines, arithmetic blocks, and so on. The use of benchmarks for validation and physical characterization of standard cell libraries may lead to two situations: (a) not all cells from the library are used in the benchmark circuit design, and (b) the cells used in this circuit are not stimulated by all possible input combinations, not guaranteeing the complete functionality of these cells. For instance, in Table 1.1, the use of different cells from a library, which contains 64 combinational cells, in the ISCAS benchmark circuit synthesis is observed. Note that, only the 'tv80\_core' benchmark used the entire set of available cells.

| ISCAS Benchmarks* | <i># cells in the circuit</i> | # used cells from library |

|-------------------|-------------------------------|---------------------------|

| c7552             | 1,311                         | 41                        |

| i2c_master_top    | 679                           | 42                        |

| iu                | 9,203                         | 43                        |

| mc_top            | 6,245                         | 58                        |

| tv80_core         | 5,594                         | 64                        |

| wb_conmax_top     | 28,089                        | 43                        |

Table 1.1: Using a 64-cell library to synthesize benchmark circuits.

\*Benchmarks source: http://www.fm.vslib.cz/~kes/asic/iscas, last access on Sep.20<sup>th</sup>, 2007.

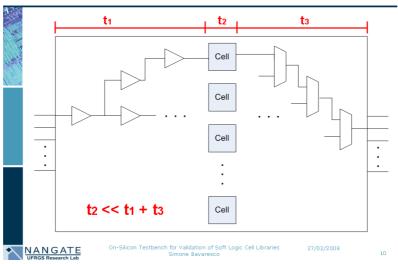

Within this context, a naive manner to achieve library verification consists in designing a circuit that connects all cells in such a way that the primary inputs are shared and individual output signals are multiplexed to reduce the number of circuit primary outputs. This strategy can obviously achieve the desired verification of cell logic behavior but, in addition to multiplexing the cell outputs, it requires buffering to compensate the high capacitance on input nodes, making it difficult to obtain timing and power dissipation data.

An efficient approach to generate a testbench for testing a set of new cells, possibly created on-the-fly, should cover the following aspects:

- (1) to ensure complete functionality test for the instantiated cells;

- (2) to ensure coverage (instantiation) of all the cells to be tested;

- (3) to allow the verification of the accuracy of the models used in the design process;

- (4) to provide means to perform long and medium term reliability tests (needed for electromigration, sufficiency of contacts, NBTI degradation, etc) without additional equipment;

- (5) to have a feasible number of cell instances compared to the set of cells to be tested.

The goal of this work is to propose a methodology to automatically generate testbench circuits for on-silicon soft-library validation meeting the aspects above.

Some works related to this propose can be found in the literature (LIN, 1999) (AGASTEIN, 1990) (MARTINEZ, 1995) (SCOTT, 1994) (CHONG, 1992). The most similar related work, presented by Rung-Bin Lin (LIN, 1999), creates benchmarks to improve the quality of a standard cell library, but such benchmarks are not viable for virtual libraries. It focuses on fixed libraries, not regarding the benchmark size and the automatic generation. It also uses specific structures (ring oscillators, delay chains, counters, and others) to compound the benchmark. Therefore, to the best of our knowledge, previous approaches fail to cope efficiently with this goal.

In this work, a straightforward and efficient testbench methodology is proposed aiming the validation of an entire set of soft-cells in terms of logic and electrical behavior. The presented solution merges well-established design and test concepts to cope with the five aspects mentioned above. A specific combinational block is built to guarantee the logic coverage (aspect 1) of a sub-set of the cells to be validated, and to provide at the output the same bit vector received at its inputs, allowing thus to cascade long chains with these blocks. The use of several blocks allows to instantiate all the cells (aspect 2). The circuit architecture is then composed of such combinational chain in a ring configuration, synchronized by a register barrier. Both synchronous and asynchronous operating modes provide different features for the proposed goals. The ring configuration allows verifying the accuracy of the models, by comparing with the predicted circuit behavior (aspect 3). The oscillation BIST technique is also included in the circuit operation for a wide range of different paths, and allows medium and long term tests (aspect 4). In case of an eventual error, the circuit diagnostic is facilitated through an arrangement of multiplexers. Finally, as the ring oscillator is composed of a variety of cells, the number of instances is not very expensive compared to the initial set of cells (aspect 5), as shown in the overhead section.

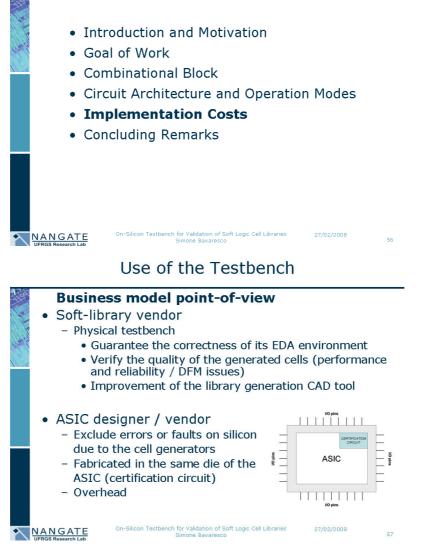

From a business model point-of-view, the methodology presented herein is useful for the soft-library vendor and to the ASIC designer client. For the vendor, it is quite important to dispose of a physical testbench in order to guarantee the correctness of its EDA environment, as well as to verify the quality of the generated cells in terms of performance and reliability, including design-for-manufacturability issues. This is essential for the continuous improvement of the library generation CAD tool. For the ASIC designer, a circuit that validates all distinct cells created on-the-fly to be used in a specific circuit provides means to exclude those errors on silicon due to the cell generators. If this test circuit is fabricated in the same die of the ASIC, it can act as a kind of 'certification circuit' for the soft-library, in different design corners and operating conditions. In this case, the overhead in terms of area and I/O pins is a compromise in fabricating together the test circuit and the ASIC, and the low cost approach presented here is very attractive.

The main concepts related to the work are presented in Chapter 2. In Chapter 3, the basic combinational block is presented. Chapter 4 presents the circuit architecture and its operation modes. Finally, the conclusions are discussed in Chapter 5.

## **2** BACKGROUND & MOTIVATION

In this chapter, the required concepts to the comprehension of this document, such as standard cell design, library-free technology mapping, testing, testability and designfor-testability are briefly explained.

#### 2.1 ASIC Flow

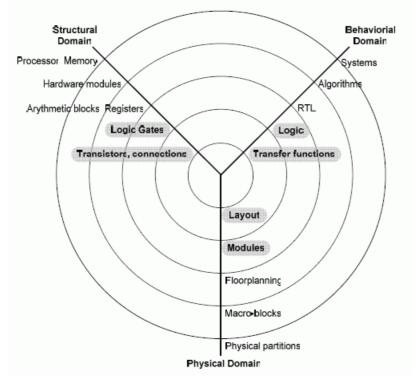

Designing ICs as complex as the ones available nowadays requires engineers working with different levels of abstraction on a system design perspective. Figure 2.1 shows a diagram illustrating these different levels of abstraction known as Y-chart (GAJSKI, 1988). The Y-diagram can be used to illustrate each domain and the transformations between domains at varying levels of design abstraction. The radial lines on the Y-chart represent three distinct design domains: behavioral, structural, and physical. That is a classical tentative, among others, to demonstrate and classify such different working levels.

Figure 2.1: Levels of design abstraction (GAJSKI, 1988).

At the *behavioral domain*, the operation of the system is captured without having to specify the physical implementation. The design starts with a specification. From the specification a behavioral description of the design is then generated. The behavioral synthesis transforms a RTL behavioral description in a hardware description language (HDL), such as VHDL or Verilog. The design is then simulated and tested by applying testbenches to verify the correct behavior as defined by the specification.

The next step is to synthesize the behavioral description. This involves converting the RTL to generic gates and registers, then optimizing the logic to improve speed and area. The behavioral code is synthesized into a structural code using a generic gate library.

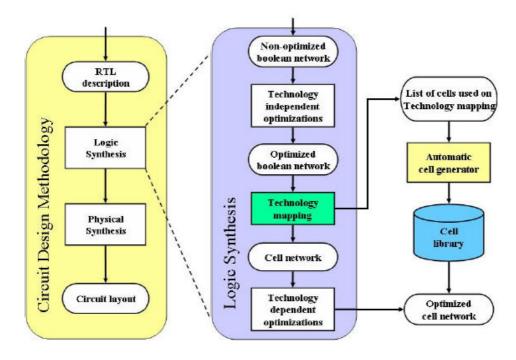

The step known as *logic synthesis* transforms a design from the behavioral to the *structural domain*. In the logic synthesis the task called *technology mapping* or *library mapping* takes a generic HDL gate-level description (boolean network) and translates it to a netlist (cell network) that specifies particular gates in the target library. Thus, the mapping task transforms the generic gate-level description into a gate-level description in the target ASIC technology.

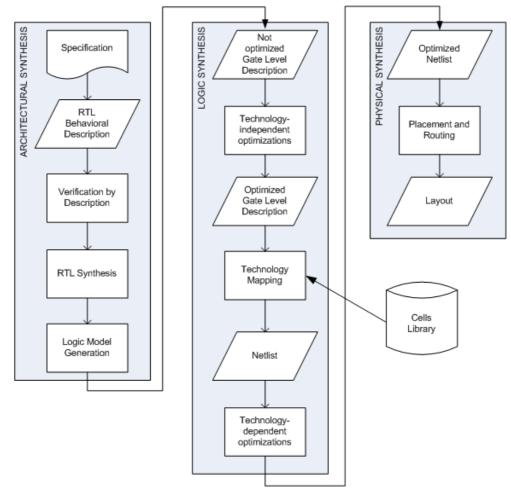

Layout generation is the last step in the procedure of turning a design into a manufacturable database. It transforms a design from the structural to the physical domain. This step is called physical synthesis when the structural netlist is manipulated as physical layout is generated (WESTE, 2005). Figure 2.2 shows a diagram illustrating the ASIC design flow.

Figure 2.2: ASIC design flow diagram (WESTE, 2005) (MARQUES, 2007a).

#### 2.2 Design Styles

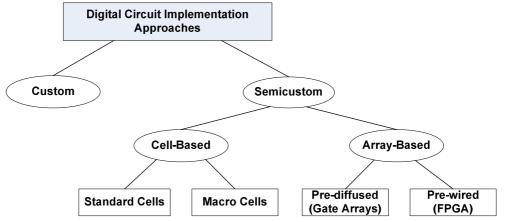

The economic viability of a microelectronics design depends upon a number of conflicting factors, such as production volume, cost, and circuit performance required to be competitive. These economic considerations have stimulated the development of a number of distinct implementation approaches that range from high-performance handcrafted design to fully programmable, medium-to-low performance designs (RABAEY, 2003).

Under these circumstances, different implementation approaches, often called design styles or even methodologies, have been used for microelectronic circuits. They are usually classified as full-custom (custom) and semicustom design styles (MICHELI, 1994). Figure 2.3 provides an overview of the design styles.

Figure 2.3: Overview of IC design styles (MICHELI, 1994) (RABAEY, 2003).

Full-custom design was popular in the early years of microelectronics. Today, the design complexity has confined custom design techniques to specific portions of a limited number of projects, such as processors, chip-sets, and arithmetic units (MICHELI, 1994).

In full-custom design one does logic and physical synthesis in order to attain the highest performance or smallest size, making use of the most advanced technologies (CHEN, 2000).

The benefits of full-custom design in general include reduced area (and therefore recurring component cost), performance improvements and also the ability to integrate (include) analog components and other pre-designed (and thus fully verified) components such as microprocessor cores that form a System-on-Chip (SoC).

The disadvantages of this design style can include increased manufacturing and design time, increased non-recurring engineering (NRE) costs and a much higher skill requirement on the part of the design team.

However, for digital designs only, cell-based semi-custom design together with modern CAD systems can offer considerable performance/cost benefits with much lower risk. Automated layout tools are quick and easy to use, and also can offer the possibility to manually handcraft and optimize any performance limiting aspect of the design. Semicustom designs can be partitioned in two major classes: *cell-based design* and *array-based design*. These classes further subdivide into subclasses, as shown in Figure 2.3. Cell-based design leverages the use of library cells, that can be designed once and stored, or the use of cell generators that synthesize macro-cell layouts from their functional specifications. Array-based design exploits the use of a matrix of configurable elements to implement the logic. Array-based circuits can be classified as pre-diffused and pre-wired, also called *mask programmable* and *field programmable* gate arrays, respectively (MPGAs and FPGAs) (MICHELI, 1994).

This work is included in the context of the *standard-cell design* which is a *cell-based design style*. The idea behind cell-based design is to reduce the implementation effort by reusing a library of cells. The advantage of this approach is that the cells only need to be designed and verified once for a given technology, and can be reused many times, thus amortizing the design cost. The disadvantage is that the constrained nature of the library (especially due to the limited number of cells) reduces the possibility of fine-tuning the design (RABAEY, 2003).

The standard-cell approach standardizes the design entry-level at the logic gate (functional blocks). A library containing a wide selection of logic gates over a range of number of inputs and drive strengths is provided. Besides the basic logic functions, such as inverter, AND/NAND, OR/NOR, XOR/XNOR and flip-flops, a typical library also contains more complex functions such as AOI/OAI (AND/OR-OR/AND-INVERTER), MUX, full-adder, comparator, counter, decoder, encoder, and so on.

The layout of each cell in a specific library has a fixed height, while its width may vary. Thus, the cell can be placed side-by-side, in such a way that their power rails and well regions properly connect to neighbor cells. Standard-cell design uses these functional blocks to achieve high gate density and good electrical performance. The quality of a synthesized design based on standard-cells depends on three components: the synthesis tool, the place and route tools and the target cell library (SCOTT, 1994).

#### Library-free Technology Mapping

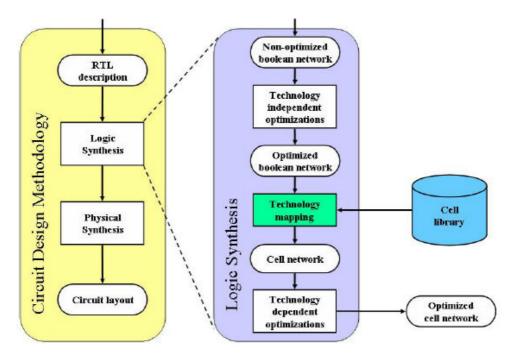

Technology mapping is the choice of the elements from a technology (typically cells from a library) that will be effectively used to implement a given circuit. Technology mapping then transforms the network of functions into a gate level netlist by trying to find an optimal network covering of library gates, with respect to some cost function (CORREIA, 2004).

The library gates used by a technology mapper can be specified using functionality (also known as library-based mapping) or parameters such as the number of inputs and series/parallel devices (also known as library-free mapping).

Figure 2.4 shows the digital circuit design flow regarding the library-based methodology for the technology mapping. In this methodology the quality of the mapped circuit has a directly relation with the library richness. Static libraries usually are not so big, because the cells characterization cost is too elevated (SECHEN, 2003). A commercial library contains no much more than one hundred cells that implement different boolean functions (MARQUES, 2007). The great advantage of this approach is the pre-characterization of the cells and the set of information associated to each cell of the library, which is considered as design cost in the map matching. Usually, this information is about area, delay, input capacitances and power consumption.

Figure 2.4: ASIC design flow with library-based technology mapping (MARQUES, 2007).

Figure 2.5, in turn, shows the digital circuit design flow regarding the methodology library-free for the technology mapping. In this approach, the mapping defines a set of cells that will be used to implement the circuit. This list of cells is then used by an automatic cell generator in order to obtain the implementation of cells to use in the circuit layout.

Figure 2.5: ASIC design flow with library-free technology mapping (MARQUES, 2007).

Thus, the concept of library-free design is based on using a virtual library available through a layout generator instead of using a set of pre-designed cells, like in the library-based design. The set of available cells is given by a user-defined constraint in the number of series transistors. This constraint in the number of series transistors is done for electrical reasons. As the cells are generated on-the-fly, a virtual library contains a great number of poorly characterized cells when compared to a pre-designed standard cell library (REIS, 1998) (REIS, 1999). Therefore, the fact of the cells not being previously designed and physically verified is the main drawback of the library-free technologic mapping and it means that such virtual libraries are, in fact, tested together with the target ASIC. In this work, a circuit for on-silicon verification and validation of digital cell libraries is proposed. This solution uses test concepts that will be presented next.

#### 2.3 Testing

#### 2.3.1 Defect, fault, failure and error

A *defect* in an electronic system is the unintended difference between the implemented hardware and its intended design. A *fault* is a representation of a "defect" at the abstracted function level, reflecting a physical condition that causes a circuit to fail to perform in a required manner. A *failure* is a deviation in the performance of a circuit or system from its specified behavior and represents an irreversible state of a component such that it must be repaired in order to provide the intended design function. A circuit *error* is a wrong output signal produced by a defective circuit. A circuit defect may lead to a fault, a fault can cause a circuit error, and a circuit error can result in a system failure (BUSHNELL, 2000) (WANG, 2006).

#### 2.3.2 Test Generation, Functional and Structural Testing

In order to test a circuit, a set of input patterns is applied to the circuit under test (CUT), and its responses are compared to the known good responses of a fault-free circuit. Each input pattern is called a *test vector*. The goal of *test generation* is to find an efficient set of test vectors that detects all faults considered for that circuit (WANG, 2006).

Traditionally, manufacturing test has been done using *functional testing*. Functional test patterns verify that the model or logic behaves as it was intended. Every entry in the truth table for the combinational logic circuit is tested to determine whether it produces the correct response. Therefore, functional testing is measured by the logic committing the correct action to the applied stimuli. Full functional correctness is the standard expectation and this should be verified at behavioral (RTL) or at gate level of the design with a simulation process (GIZOPOULOS, 2006).

A more practical approach is to select specific test patterns based on circuit structural information and a set of *fault models*. This approach is called *structural testing*. Structural testing is used to verify the topology of the manufactured chip (GIZOPOULOS, 2006). Such testing relies on fault models, which assume that the physical defect will represent itself in a certain way. Structural testing saves time and improves test efficiency, as the total number of test patterns is decreased because the test vectors target specific faults that would result from defects in the manufactured circuit.

Structural testing cannot guarantee detection of all possible manufacturing defects, as the test vectors are generated based on specific fault models. However, the use of fault models provides a quantitative measure of the fault detection capabilities of a given set of test vectors for a targeted fault model. This measure is called *fault coverage* and is defined as:

#### *fault coverage = (number of detected faults) / (total number of faults)*

It may be impossible to obtain a fault coverage of 100% because of the existence of undetectable faults (WANG, 2006). An undetectable fault means there is no test to distinguish the fault-free circuit from a faulty circuit containing that fault. As a result, the fault coverage can be modified and expressed as the *fault detection efficiency*, also referred to as the *effective fault coverage*, which is defined as:

fault detection efficiency = (number of detected faults) / (total number of faults - number of undetectable faults).

#### 2.3.3 Fault models

Manufacturing faults can be of a wide variety and manifest themselves as shortcircuits between signals, short-circuits to the supply rails, and floating nodes. Because of the diversity of defects, it is difficult to generate tests for real defects. In order to evaluate the effectiveness of a test approach, generating and evaluating a set of test vectors, and qualify a good or bad circuit, these faults must be related to the circuit model, i.e. derive a *fault model*.

Generally, a good fault model should satisfy two criteria: (1) it should accurately reflect the behavior of defects, and (2) it should be computationally efficient in terms of fault simulation and test pattern generation (WANG, 2006). Many fault models have been proposed, but no single fault model accurately reflects the behavior of all possible defects that can occur. As a result, a combination of different fault models is often used.

#### 2.3.3.1 Stuck-At Faults

Stuck-at fault is the most common fault model used in fault simulation. Functional testing uses the *single stuck-at model* because of its effectiveness in finding many common defect types. The stuck-at fault models the behavior that occurs if the terminals of a gate are stuck at either a high (stuck-at-1, sa1) or low (stuck-at-0, sa0) voltage.

#### 2.3.3.2 Delay Faults

Fault-free operation of a logic circuit requires not only performing the logic function correctly but also propagating the correct logic signals along paths within a specified time limit. A *delay fault* causes excessive delay along a path such that the total propagation delay falls outside the specified limit.

Timing-related failures may be caused by isolated gate delays or process-related timing problems that accumulate along logic paths and prevent the circuit from functioning at-speed. The timing-related malfunction is characterized by defining the concept of delay faults related to circuit critical paths. Conventional techniques for delay test require two distinct primary input vectors that provoke a transition signal at the fault site and propagate the faulty delay effect to a primary output (ARABI, 1998).

Timing related defects have been modeled as different delay fault models. In *gatedelay fault* and *transition fault* models, a delay fault occurs when the time interval taken

24

for a transition from the gate input to its output exceeds its specified range. The other model is *path-delay fault*, which considers the cumulative propagation delay along a signal path through the CUT, i.e. the sum of all gate delays along the path. The combinational path begins at a primary output or another clocked flip-flop, contains a connected chain of gates, and ends at a primary input or a clocked flip-flop. The specified time range can be the duration of the clock period (or phase) or the vector period. The propagation delay is the time that a signal event (transition) takes to traverse the path (BUSHNELL, 2000).

In a combinational circuit the path that has the longest propagation time from a primary input to a primary output, called *critical path*, determines the operating speed of the circuit. Also in a sequential circuit, the system is free of timing failures if every combinational path between two memory elements propagates its signal in less time than the interval of the operating system clock. In other words, the input signal of every memory element in the system should have a stable signal before the arrival of the active clock edge, obviously not forgetting the setup time of such memory point (registers). To be reliable, at least all critical paths in the system should be tested (ARABI, 1998).

#### 2.4 Delay test verification

Digital circuits are tested by verifying the state malfunction in logic based on a standard fault model, the "stuck-at 0 or 1" fault. This fault model successfully describes most of state malfunction in logic. However, as the structure of logic circuits has become increasingly complex, system-timing failures occur more frequently.

The timing-related malfunction is characterized by defining the concept of delay faults related to circuit critical paths. Conventional techniques for delay testing require two distinct primary input vectors that provoke a transition signal at the fault site and propagate the faulty delay effect to a primary output.

Timing related defects have been broadly modeled as gate delay faults or as path delay faults. The gate delay fault model assumes that the incorrect timing behavior of the circuit is due to excess delays in one or more components in the path. Test vector generators based on gate delay fault model deal with one fault at a time and try to find a test which sensitizes some path trough the fault location such that the transition at the output is affected by the target fault. The path delay fault model considers the propagation delay through one or more paths exceeding the timing constraint. Therefore, this model makes no assumption about the individual component delays. To be reliable, at least all critical paths in the system should be tested.

#### 2.4.1 Characterization

Accurate determination of logic gate propagation delay and its correlation with processing variables and layout design rules is needed to optimize the high-speed performance of actual logic circuits (LONG, 1984). However, accurate wafer-level high speed measurement of timing and delay is limited by the test interface.

Synchronous circuits have been employed for measurement of propagation delay. The maximum clock frequency at which the circuit presents the proper data signature can be directly measured. An average propagation delay per gate can be inferred from the maximum clock frequency through transient simulation or timing analysis. However, synchronous circuits are often much more difficult to evaluate with accuracy because of the high-speed test interface problems, such as reflections and ground noise and because the observed maximum frequency of operation is critically dependent on clock waveform properties such as symmetry, amplitude, and offset. Also, it can be shown that the maximum clock frequency for a given flip-flop type and implementation (NAND, NOR, etc.) will be achieved only at a specific clock symmetry or nonsymmetry.

Therefore, to stay within these limitations, self-test or built-in test circuitry must also be included on all large-scale high-speed ICs to reduce the total number of off-chip interfaces needed to verify functionality at speed.

The design of a test structure for propagation delay measurement must facilitate accuracy and simplicity of measurement and provide correlation between the test structure and actual logic circuits. The "classic" or default asynchronous test structure has generally been the ring oscillator, often configured with minimum fan-in, fan-out and interconnect capacitive loading. Measurement of this circuit is very simple, requiring only power supply, ground, and output connections.

#### 2.4.2 Delay fault testing

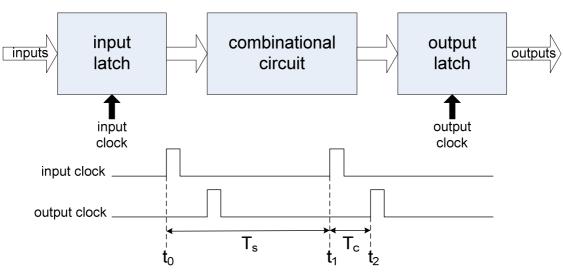

The maximum allowable clock rate is determined by the propagation delays of the combinational logic block between latches. To observe delay defects, it is necessary to create and propagate transitions in the circuit running *at-speed* (at its specified operating frequency).

Creating transitions requires application of a vector pair,  $V = \langle v_1, v_2 \rangle$ , at the inputs of the combinational part of the circuit. The first vector initializes the relevant internal signals to desired initial logic values, while the second vector causes the desired transitions and sensitizes the transition from the target fault site to an output. The test application scheme for combinational circuits is shown in Figure 2.6.

In normal operation, only one clock, the system clock, is used to control the input and output latches and its period is  $T_c$ . In this illustration, the input and output latches are controlled by two different clocks in the test mode: the input and output clocks, respectively. The period of these clocks,  $T_s$ , is assumed to be larger than  $T_c$ . The input and output clocks are skewed by an amount equal to  $T_c$ .

The first vector,  $v_1$ , is applied to primary inputs at time  $t_0$ . The second vector,  $v_2$ , is applied at time  $t_1$ . Time  $T_s = t_1 - t_0$  is assumed to be sufficient for all signals in the circuit to stabilize under the first vector. After the second vector is applied, the circuit is allowed to settle down only until time  $t_2$ , where  $t_2 - t_1 = T_c$ . At time  $t_2$ , the primary output values are observed and compared to a prestored response of a fault-free circuit to determine if there is a defect.

Figure 2.6: Delay fault testing.

Transition fault model, gate fault model and path delay fault modes are the classical fault models that have been used to represent delay defects.

#### 2.5 Testability and Design-for-Testability

Testability is a relative measure of the effort or cost of testing a logic circuit. When considering the testability of designs, two properties are important: controllability and observability. (1) *Controllability* is the ability to establish a specific signal value at each node in a circuit by setting values on the circuit inputs. (2) *Observability* is the ability to determine the signal value at any node in a circuit by controlling the circuit inputs and observing its outputs (ABRAMOVICI, 1990).

The correctness of a combinational circuit can be validated by exhaustively applying all possible *input patterns* and observing the responses. A more feasible testing approach is based on the following premises. Firstly, an exhaustive enumeration of all possible input patterns contains a substantial amount of *redundancy*, that is, a single fault in the circuit is covered by a number of input patterns. Detection of that fault requires only one of those patterns, while the other ones are superfluous. Secondly, a substantial reduction in the number of patterns can be obtained by relaxing the condition that all faults must be detected. For instance, detecting the last single percentage of possible faults might require a huge number of extra patterns, and the cost of detecting them might be larger than the eventual replacement cost. Typical test procedures only attempt 95-99% fault coverage.

By eliminating redundancy and providing reduced fault coverage, it is possible to test most combinational logic blocks with a limited set of input vectors. However, this does not solve the sequential problem. To test a given fault in a state machine, it is not sufficient to apply the correct input excitation since the engine must be brought to the desired state first. This requires a sequence of inputs to be applied. Propagating the circuit response to one of the output pins might require another sequence of vectors.

One way to address the problem is to turn the sequential network into a combinational one by breaking the feedback loop in the course of the test. This is one of the key concepts behind the *scan-test* methodology (ABRAMOVICI, 1990). Another approach is to let the circuit test itself. Such a test, called *self-test*, does not require external vectors and can proceed at a higher speed (RABAEY, 2003).

Design-for-testability – DFT represents design techniques that are required in order to improve the testability of the design for achieving quality and reducing the test cost of the digital circuit, while at the same time simplifying the test, debug and diagnose tasks. By considering testing from the early phases of the design process, it is possible to simplify the whole validation process. *Scan design* and *built-in self-test (BIST)* are examples of design techniques to improve testability. Later these concepts will be better explained in the context of this work.

#### 2.6 How to test a library?

The main question of the work presented herein is "How to test a digital cell library". In particular, when such cells are automatically generated by software, they are directly applied to the target ASIC, and this set of cells tends to be composed by a huge number of different combinational logic gates.

Instead of verifying the correctness of a specific circuit, the objective of this work is to propose a circuit, whose main goal is the verification and validation of each cell presented in a standard cell library. It represents, in fact, a new issue in the test domain where usually test methods are applied to test the functionality of application circuits and systems. In this particular case, the proposed circuit is not useful for any specific application or electronic product, but to test a set of logic cells generated by software to their use in a particular ASIC design.

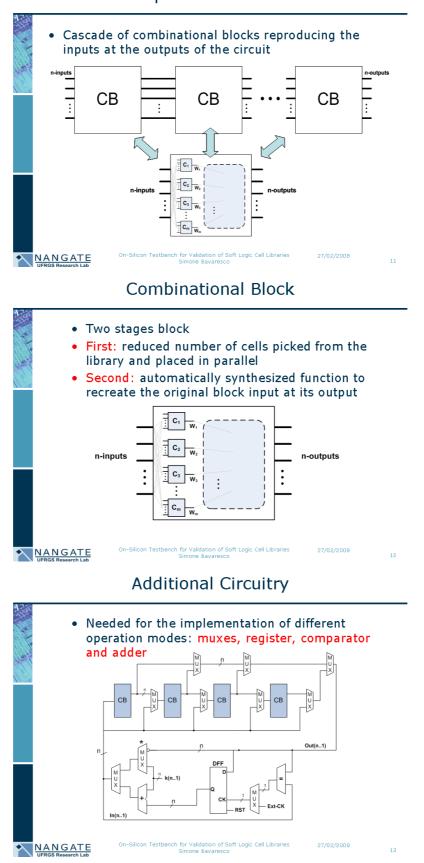

Before discussing the circuit architecture, the structure of the combinational blocks are presented. The combinational blocks represent the basic components of the proposed test circuit.

### **3** COMBINATIONAL BLOCK

This chapter presents the description of the combinational blocks which are the basic structures of the proposed circuit.

In terms of logic cell functionality, three main groups may be identified: (1) inverters and buffers; (2) sequential cells; (3) combinational cells. Group (1) is easily verified since such a kind of cell presents only one input signal. Group (2), in turn, has generally a small and limited number of different latches and flip-flops, facilitating its verification. Moreover, in this group the timing performance is usually more important than the logic functionality that is somewhat trivial in the pass and storage modes. In the case of group (3), the number of cells is generally more expressive than the other ones. Moreover, the number of input nodes in these cells makes the functional test a more complex task due to the  $2^n$  different input combinations, being *n* the number of input nodes.

The most naïve strategy to test the group (3) consists in placing all cells connected in parallel to the same input bus, where all input combinations are applied simultaneously. However, in doing so, input buffering must be considered due to the high node capacitances (great number of inputs connected to the same node). Furthermore, multiplexers should be used at the output signals to reduce the number of output pads. In this approach, timing and power consumption characteristics are not easily verified since the signals propagate only through single cells in testing.

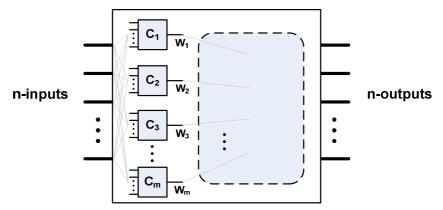

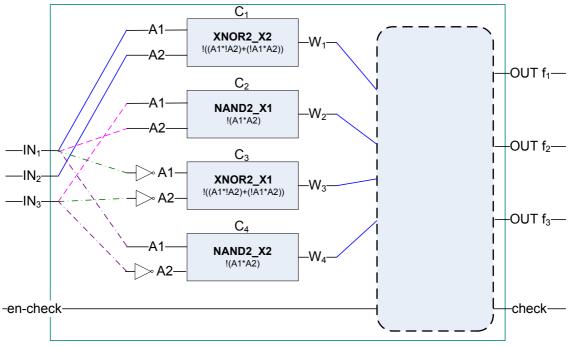

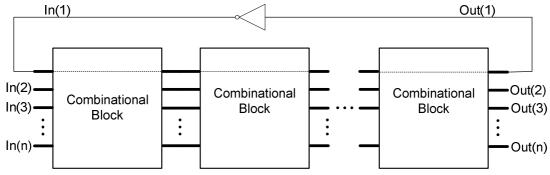

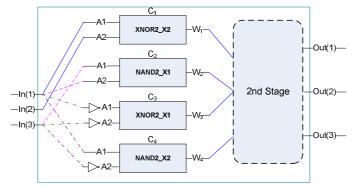

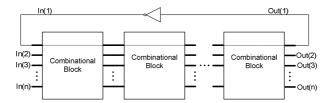

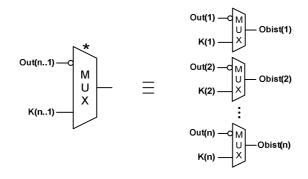

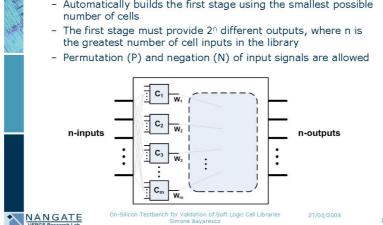

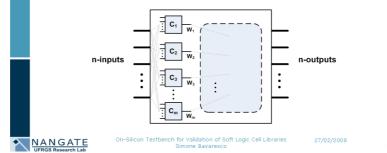

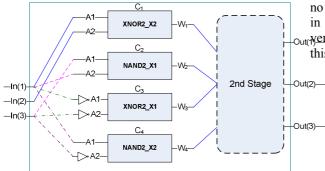

The proposed architecture consists in building combinational blocks that receive an input bus, where all signal combinations are provided, and produce a sequence of output vectors also presenting all possible signal combinations, to be then applied to the next combinational block. The combinational block is illustrated in Figure 3.1.

Figure 3.1: Combinational block illustration.

In order to ensure full logic verification of every library cell, the combinational blocks used in our verification circuit are built according to the following principles:

- a cell from the library is declared verified if it is instantiated such that inputs of the cell consume primary inputs of a combinational block. Polarity is indifferent and the cell can consume the input signals through an inverter or directly;

- every library cell is instantiated at the primary inputs of at least one combinational block, to ensure it is verified;

- block creation continues while there are cells from the library that are not yet declared as verified cells;

- every block instantiates a non-empty subset of non-verified cells at the block inputs, so that more cells receive the verified label. Indeed, the creation of a block is done in a way to maximize the number of cells that passes from the unverified to verified status.

From a block instantiation point of view, the combinational blocks obey to the following principles:

- all possible input combinations are applied to every block;

- every block reproduces the input signals at its outputs, providing thus all possible signal combinations for the next block.

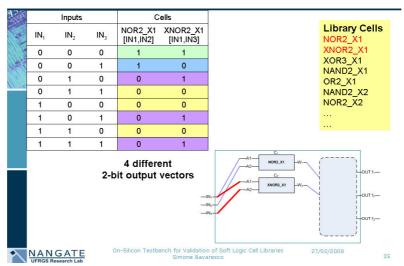

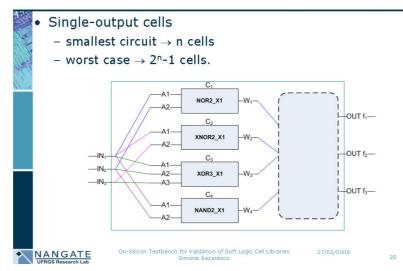

Each combinational block is built using two cascaded stages. The minimum number of signals at the input bus is determined by the greatest number of inputs of a single cell used in the first stage.

The first stage is built with instances of cells placed in one-logic level exercised by all possible input combinations. The number of cells used in the first stage is the sufficient number to create  $2^n$  logic combinations at the output nodes of the first stage.

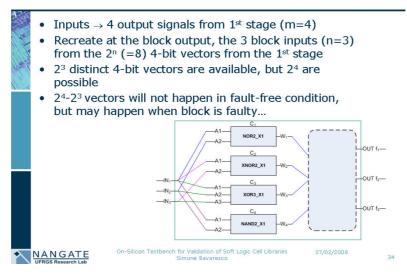

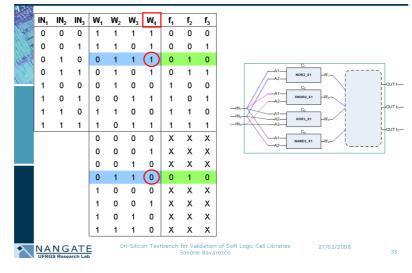

The output signals of verified cells are used as inputs to the second stage, which regenerates the primary inputs. The second stage is composed of synthesized functions with additional cells instances in a multi-logic level.

#### 3.1 First stage

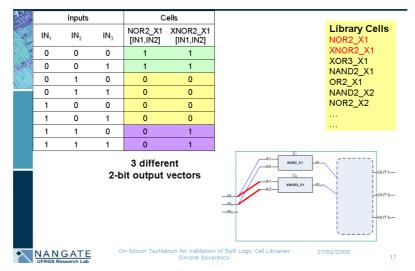

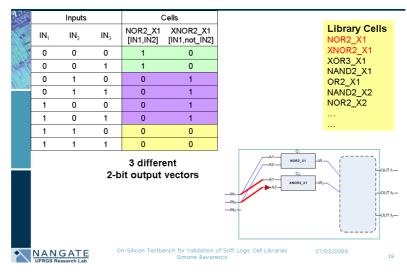

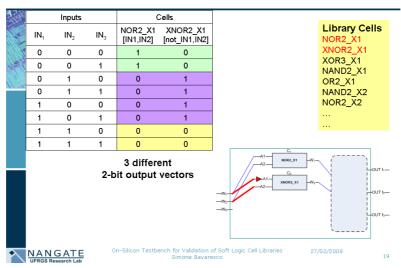

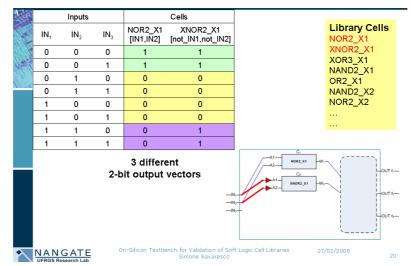

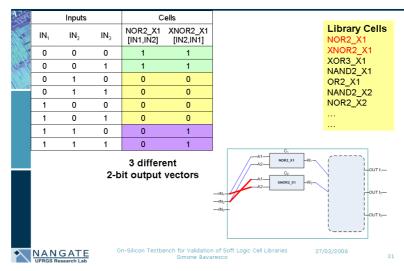

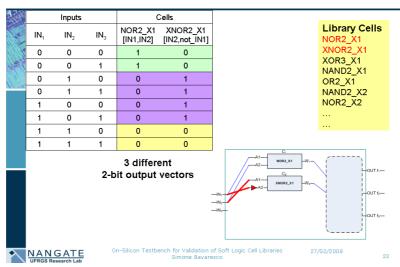

To generate the first stage, the whole set of cells in the library is ordered according to a given criterion; for example alphabetic order, number of inputs, number of 0s and 1s at the output of the logic function, random order, or any other. Once the cells are ordered, non verified cells are picked one-by-one to create a verified instance.

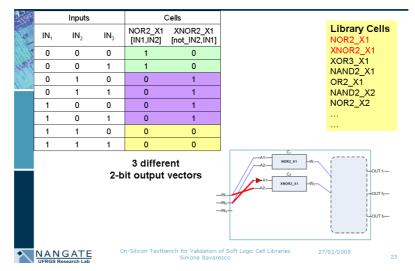

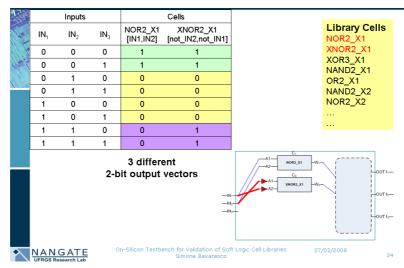

Assuming an n-input block, the goal is to choose a number m of cells in the first stage sufficiently large to produce at least  $2^n$  different m-bit output vectors at the first stage. The  $2^n$  intermediate different combinations (m-bit vectors) are required to reconstruct the original  $2^n$  input vectors (combinations) with a one-to-one correspondence. To achieve this goal, the instance of a new cell considers all possible direct and inverted connections between the block primary inputs and the inputs of each newly selected cell are tried.

For a library where only single-output cells are available, the smallest circuit possible for the first stage has n cells, while the worst case is a first stage containing  $2^{n}$ -1 cells. Verified selected cells may or may not re-appear in the second stage or in other combinational blocks.

30

An example for generation of a 3-bit output vector with the smallest circuit possible for the first stage is shown in Table 3.1. In this case, all cells have the same number of logic values '0' and '1'.

| А | В | С | XOR3_X1<br>(A,B,C) | XOR2_X1<br>(B,C) | XOR2_X2<br>(A,C) |

|---|---|---|--------------------|------------------|------------------|

| 0 | 0 | 0 | 0                  | 0                | 0                |

| 0 | 0 | 1 | 1                  | 1                | 1                |

| 0 | 1 | 0 | 1                  | 1                | 0                |

| 0 | 1 | 1 | 0                  | 0                | 1                |

| 1 | 0 | 0 | 1                  | 0                | 1                |

| 1 | 0 | 1 | 0                  | 1                | 0                |

| 1 | 1 | 0 | 0                  | 1                | 1                |

| 1 | 1 | 1 | 1                  | 0                | 0                |

Table 3.1: Minimum number of cells at the first stage.

This maximum limit of necessary cells is explained by the worst case of a block constitution. If a block must generate 3-bit output vector and has only cells with one logic value '1' available to use, it will be needed at most 7 cells to generate 8 distinct vectors at the output of the first stage as shown in Table 3.2.

| A | В | С | NOR3_X1<br>(A,B,C) | AND3_X2<br>(B,A,!C) | NOR3_X2<br>(!C,A,B) | AND3_X1<br>(C,B,!A) | NOR3_X4<br>(A,C,!B) | OR3_X4<br>(!C,!B,!A) | NAND3_X1<br>(C,!B,A) |

|---|---|---|--------------------|---------------------|---------------------|---------------------|---------------------|----------------------|----------------------|

| 0 | 0 | 0 | 1                  | 0                   | 0                   | 0                   | 0                   | 1                    | 1                    |

| 0 | 0 | 1 | 0                  | 0                   | 1                   | 0                   | 0                   | 1                    | 1                    |

| 0 | 1 | 0 | 0                  | 0                   | 0                   | 0                   | 1                   | 1                    | 1                    |

| 0 | 1 | 1 | 0                  | 0                   | 0                   | 1                   | 0                   | 1                    | 1                    |

| 1 | 0 | 0 | 0                  | 0                   | 0                   | 0                   | 0                   | 1                    | 1                    |

| 1 | 0 | 1 | 0                  | 0                   | 0                   | 0                   | 0                   | 1                    | 0                    |

| 1 | 1 | 0 | 0                  | 1                   | 0                   | 0                   | 0                   | 1                    | 1                    |

| 1 | 1 | 1 | 0                  | 0                   | 0                   | 0                   | 0                   | 0                    | 1                    |

Table 3.2: Maximum number of cells at the first stage.

#### **3.1.1 Implementation**

In general, it is possible to briefly describe the test circuit generation flow as follows. Firstly, a parsing of a library is done for the identification of the existing cells. Thus, these cells are sorted in a list and the construction of the first part of the block begins with the search of cells in the list. In the search task, the cells are tested with some or all inputs combinations in order to target a certain number of output vectors combinations.

The first part of a block is complete when the desired number of distinct output vectors combinations is achieved and then the construction of another one starts. This process continues until all cells of the library have been used at the first stage of one of the blocks.

After the first stage is complete in every block, the functions that will recreate the input vector will be generated. These functions represent the second part of each block.

In this work, the generation of combinational blocks was automated by a specific CAD tool, with parameters to configure the cell list sorting criterion, the number of input/output nodes of the block and the enabling/disabling of the NP equivalences for the cells in the first stage of the blocks. Next, the implementation of this CAD tool will be detailed.

#### (a) Parse

The generation of the combinational blocks starts with the parsing of a Liberty library file or an Eqn file, which is loaded into the tool data structure.

(b) Sort

The initial stage consists in sorting the available cells. This choice will influence on the order in which they will be used later. Cells can be sorted through five methods: (i) alphabetical ordering; (ii) input number; (iii) quantity of minterms; (iv) random ordering; (v) difference between the quantity of zeros and ones of the cell function.

(c) Search

Having the set of cells sorted as desired, the construction of the first stage for a block begins. The order in which the cells are picked from the available list can be set in three different manners: sequentially, alternately (first-last) and randomly.

#### (d) Combinations testing

The first picked cell is put in the block with its original inputs. So, each picked cell, except the first one of the block, is tested with all the combinations of the block and cell inputs – if no stopping criterion is used regarding the number of combinations; or it is tested with some of the block and cell inputs – if using a stopping criterion.

The goal is to achieve the maximum number of different combinations with the addition of each cell. A cell is added to the block, only if its addition creates a new output combination and the combination of cell inputs that generates more different output combination will be selected. Although, if the cell input combination in test generates the maximum number of possible combinations for the given number of cells, the combinations testing stop and the actual combination is used as the cell input combination.

The *block inputs combinations* are defined as the arrange of the block inputs that can be used as cell inputs.

Defined the block input arrange which will be used as cell input, the permutations and/or inversions of this arrange are defined as the *cell inputs combinations*.

There are three sets of combinations that can be tested as cell inputs, given a block input combination:

- N: combinations considering negations.

- P: combinations considering permutations.

- NP: combinations considering negations and permutations.

Given the set of combinations that will be tested as inputs for each cell, the software can follow the standard sequence of the combinations list to test or it is possible to select a combination from the list randomly in order to test. Also for the block inputs combinations, the test can follow the standard sequence of combinations or the combination to test can be selected randomly.

#### (e) Number of test combinations

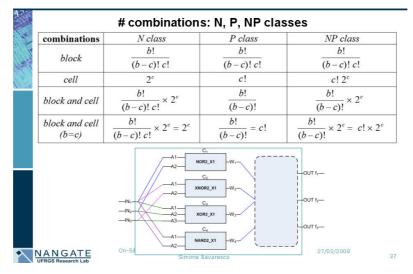

Being *b* the number of block inputs and *c* the number of cell inputs, Table 3.3 shows how to calculate the number of combinations for each combination set.

| combinations                | Ν                                       | Р                        | NP                                             |

|-----------------------------|-----------------------------------------|--------------------------|------------------------------------------------|

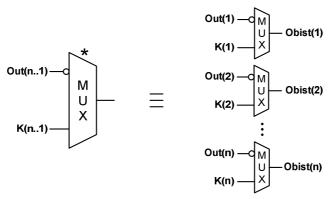

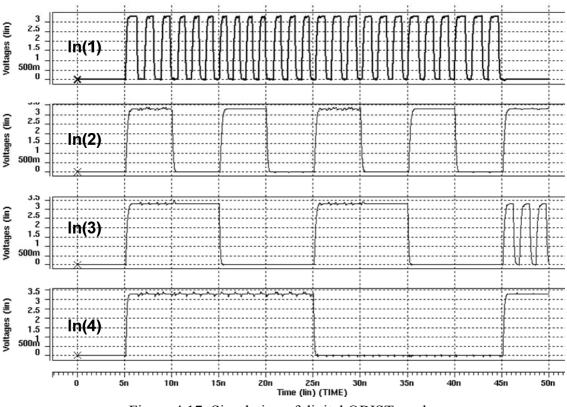

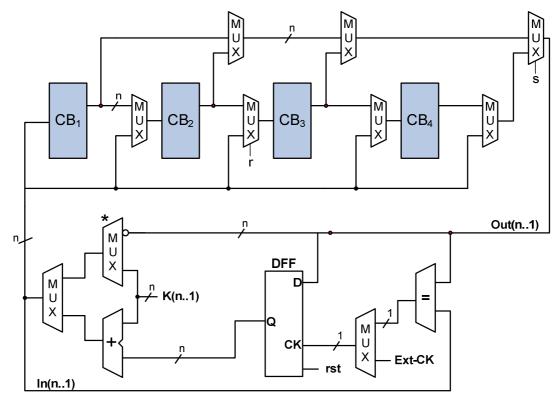

| block                       | $\frac{b!}{(b-c)!  c!}$                 | $\frac{b!}{(b-c)!  c!}$  | $\frac{b!}{(b-c)! \ c!}$                       |