## DISSERTAÇÃO DE MESTRADO

## IMPLEMENTAÇÃO EM VHDL DE UMA BIBLIOTECA PARAMETRIZÁVEL DE OPERADORES ARITMÉTICOS EM PONTO FLUTUANTE PARA SER USADA EM PROBLEMAS DE ROBÓTICA

DIEGO FELIPE SÁNCHEZ GÓMEZ

Brasília, dezembro de 2009

## UNIVERSIDADE DE BRASÍLIA

FACULDADE DE TECNOLOGIA

## **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

### UNIVERSIDADE DE BRASILIA

Faculdade de Tecnologia Departamento de Engenharia Mecânica

### IMPLEMENTAÇÃO EM VHDL DE UMA BIBLIOTECA PARAMETRIZÁVEL DE OPERADORES ARITMÉTICOS EM PONTO FLUTUANTE PARA SER USADA EM PROBLEMAS DE ROBÓTICA

DIEGO FELIPE SÁNCHEZ GÓMEZ

ORIENTADOR: CARLOS HUMBERTO LLANOS QUINTERO

DISSERTAÇÃO DE MESTRADO EM SISTEMA MECÂTRONICOS

Brasília, dezembro de 2009

### UNIVERSIDADE DE BRASILIA

Faculdade de Tecnologia Departamento de Engenharia Mecânica

## DISSERTAÇÃO DE MESTRADO

### IMPLEMENTAÇÃO EM VHDL DE UMA BIBLIOTECA PARAMETRIZÁVEL DE OPERADORES ARITMÉTICOS EM PONTO FLUTUANTE PARA SER USADA EM PROBLEMAS DE ROBÓTICA

### DIEGO FELIPE SÁNCHEZ GÓMEZ

Relatório submetido ao Departamento de Engenharia Mecânica da faculdade de Tecnologia da Universidade de Brasília como parte dos requisitos necessários para a obtenção do grau de Mestre em Sistemas Mecatrônicos

### Banca Examinadora

| Prof. Carlos Llanos Quintero, Dr., ENM/UnB Orientador       |  |

|-------------------------------------------------------------|--|

| Prof. Edward D. Moreno Ordoñez Dr., UFS  Examinador externo |  |

| Prof. Geovany Araujo Borges Dr., ENE/UNB Examinador externo |  |

Brasília 11 de dezembro de 2009

### FICHA CATALOGRÁFICA

SÁNCHEZ G., DIEGO FELIPE

IMPLEMENTAÇÃO EM VHDL DE UMA BIBLIOTECA PARAMETRIZÁVEL DE OPERADORES ARITMÉTICOS EM PONTO FLUTUANTE PARA SER USADA EM PROBLEMAS DE ROBÓTICA [Distrito Federal] 2009.

vii, 87p.  $210 \times 297$  mm (ENM/FT/UnB, Mestre, Sistemas Mecatrônicos, 2009). Dissertação de Mestrado – Universidade de Brasília. Faculdade de Tecnologia.

Departamento de Engenharia Mecânica.

1. Aritmética de Ponto flutuante 2. FPGAs

3. Cinemática de Manipuladores4. Cinemática diretaI. ENM/FT/UnBII. Título (série)

### REFERÊNCIA BIBLIOGRÁFICA

SÁNCHEZ, DIEGO F. (2006). Implementação em VHDL de uma biblioteca parametrizável de operadores aritméticos em ponto flutuante para ser usada em problemas de robótica. Dissertação de Mestrado em Sistemas Mecatrônicos, Publicação ENM.DM-30A/09, Departamento de Engenharia Mecânica, Universidade de Brasília, Brasília, DF, 87p.

### CESSÃO DE DIREITOS

AUTOR: Diego Felipe Sánchez Gómez

TÍTULO:Implementação em VHDL de uma biblioteca parametrizável de operadores aritméticos em ponto flutuante para ser usada em problemas de robótica.

GRAU: Mestre ANO: 2009

É concedida à Universidade de Brasília permissão para reproduzir cópias desta dissertação de mestrado e para emprestar ou vender tais cópias somente para propósitos acadêmicos e científicos. O autor reserva outros direitos de publicação e nenhuma parte dessa dissertação de mestrado pode ser reproduzida sem autorização por escrito do autor.

Diego Felipe Sánchez Gómez SCLN 407 Bloco C, Apartamento 216 70855-030 Brasília-DF-Brasil

### Agradecimentos

Quero agradecer inicialmente a Deus por ter colocado no meu caminho pessoas maravilhosas que fizeram possível o desenvolvimento deste trabalho. A minha mãe, Malely Gómez e aos meus irmãos Johana Sánchez Gómez e José Omar Sánchez Gómez, por seu apoio e estimulo.

Aos professor Carlos Llanos e Mauricio Ayala, no desenvolvimento da pesquissa.

Aos meus colegas e amigos do GRACO, especialmente ao Daniel Muñoz, Jones Yudi, Janier Arias, Ronald Hurtado, Evandro Teixeira, Maria Cristina Gallego pela ajuda, conselhos, também pelas alegrias compartidas e pela companhia nos momentos difíceis.

Á CNPQ (Conselho Nacional de Desenvolvimento Científico e Tecnológico) pelo apoio financeiro deste trabalho. Ao Grupo de automação e Controle (GRACO) e todos meus professores pelo suporte e formação acadêmica.

DIEGO FELIPE SÁNCHEZ GÓMEZ

Este trabalho descreve a implementação em FPGA de uma biblioteca parametrizável em ponto flutuante abrangendo operadores aritméticos e trigonométricos comumente encontrados em aplicações robóticas (a saber, soma, subtração, divisão, raiz quadrada, seno, cosseno e arco-tangente). A biblioteca é parametrizável pelo tamanho da palavra (expoente e mantissa) para o conjunto de operadores. Esta biblioteca foi usada na implementação hardware da cinemática direta de um robô manipulador de configuração esférica com cinco graus de liberdade. No intuito de gerar automaticamente o código VHDL dos operadores em ponto flutuante para diferentes tamanhos de palavra, definida pelo usuário, uma ferramenta CAD foi desenvolvida em MATLAB. Em este contexto, são usados algoritmos baseados em Goldschmidt e Newton-Raphson para calcular as operações de divisão e raiz quadrada. Um análise entre os parâmetros consumo de recursos, consumo de multiplicadores embebidos do FPGA e aspetos relacionados à latência e precisão, para as duas arquiteturas (Goldschmidt e Newton-Raphson), permite escolher a melhor arquitetura para uma aplicação específica. Para ambas implementações são obtidas altas vazões (Mresultados/s). A análise mostra uma vantagem da arquitetura Newton-Raphson sobre a arquitetura Goldschmidt.

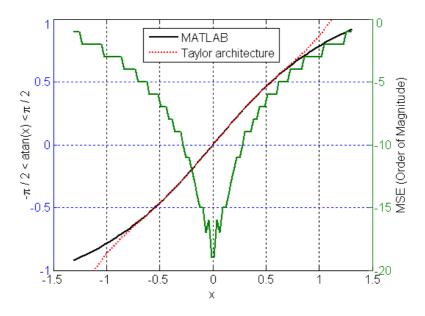

Para o cálculo das funções transcendentais são implementadas duas arquiteturas baseada em CORDIC e expansão em séries de Taylor. Similarmente ao caso da divisão e raiz quadrada, é feito uma análise entre os parâmetros consumo de recursos, consumo de multiplicadores embebidos do FPGA, latência e precisão. A análise mostrou que a arquitetura baseada em expansão em séries de Taylor apresentou um melhor desempenho para o cálculo das funções seno e cosseno. Porém, a arquitetura CORDIC apresenta um melhor desempenho para o cálculo da função arco-tangente. Para validar os circuitos propostos, varias simulações usando MATLAB foram desenvolvidas (os resultados são usados como um estimador estático dos operadores em ponto flutuante). Os resultados do erro quadrático médio (MSE) mostram uma adequada precisão dos operadores implementados.

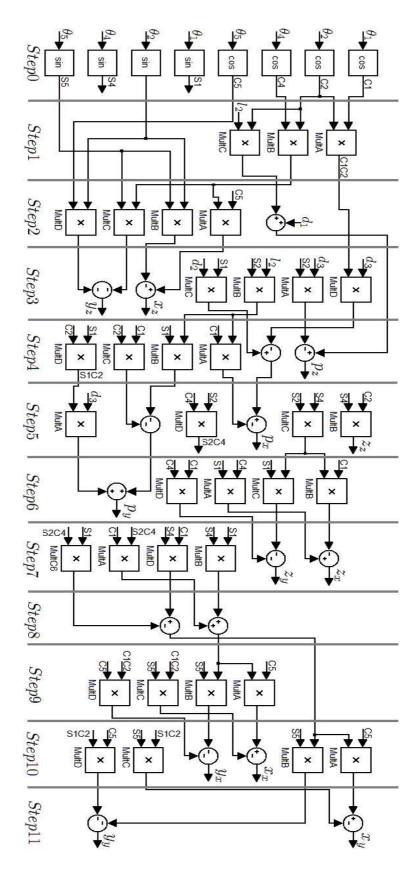

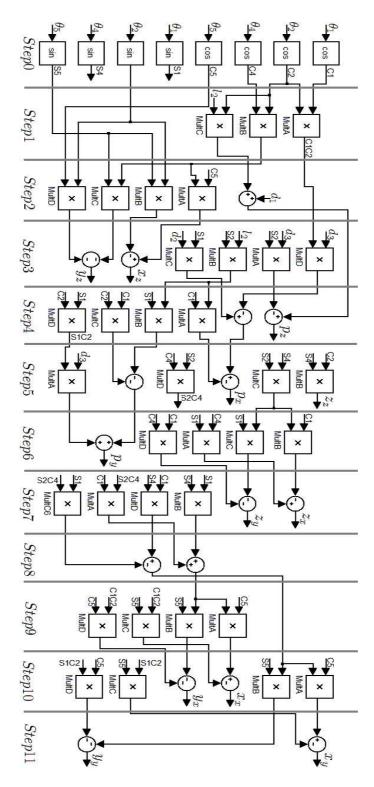

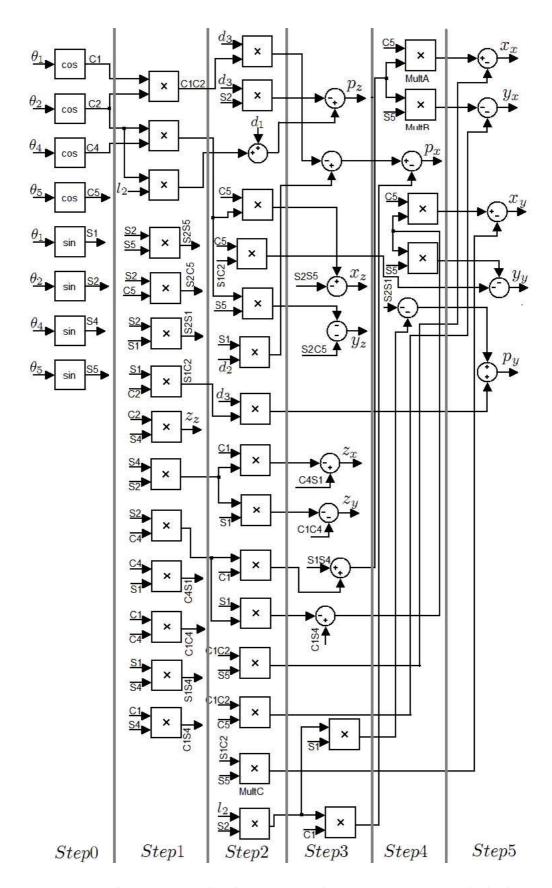

Finalmente, no intuito de validar a funcionalidade do conjunto de operadores, foi desenvolvida uma arquitetura hardware para o cálculo da cinemática direta de um robô manipulador de configuração esférica com cinco graus de liberdade. A arquitetura proposta foi concebida usando uma abordagem de planejamento por restrição de tempo e área. Em este caso, as unidades de ponto flutuante foram usadas, 8 unidades para o cálculo de funções transcendentais (seno e cosseno), e 4 multiplicadores e 2 unidades de soma/subtração para o cálculo de operações aritméticas. Os resultados de síntese mostram que a arquitetura proposta é viável em famílias de FPGAs modernas, nas quais há uma abundancia de elementos lógicos disponíveis. Todos os cálculos foram executados com sucesso e também validados usando os resultados em MATLAB como um estimador estatístico. O tempo de processamento da arquitetura hardware foi comparada com o mesmo modelo cinemático em software, usando um processador hard PowerPC (embebido na FPGA) e uma implementação em MATLAB executada em um processador AMD Atlhon Dual-Core de 2,1GHz. O tempo de cálculo da cinemática direta implementada em hardware é 0,67 µs (relógio de 100MHz), considerando a mesma formulação implementada em software usando um processador PowerPC necessita 1,61ms, executada no mesmo dispositivo FPGA e com o mesmo relógio. Adicionalmente, a implementação em MATLAB gasta 0,013ms (relógio de 2.1GHz).

### ABSTRACT

This work describes an FPGA implementation of a parameterizable floating-point library including arithmetic and trigonometric operators commonly found in robotic applications (namely, addition, subtraction, division, square root, sine, cosine and arctangent). The library is parameterizable by word length (exponent and mantissa) for the set of operators. This library was used in the hardware implementation of a direct kinematics for a robot manipulator with a spherical topology with five degrees of freedom. In order to generate automatically the VHDL code of the floating point operators for different word length representations, which are defined by the designer, a CAD tool were developed in MATLAB. In this context, algorithms based on Goldschmidt and Newton-Raphson has been implemented for calculating both division and square root operators. A tradeoff analysis among the area cost, FPGA embedded multipliers consumption and aspects related to the latency and precision, for both developed architectures (Goldschmidt and Newton-Raphson), allows the choice of the better architecture for a specific application. High throughputs (Mresults/s) are achieved for both implementations. The trade-off analysis shows advantages of the Newton-Raphson over the Goldschmidt architecture.

For computing the transcendental functions two architectures based on CORDIC and Taylor series expansion were implemented. Similarly to the case of the division and square root, a tradeoff analysis among the area cost, FPGA embedded multipliers consumption, latency and precision issues has been developed. The trade-off analysis shows that the architecture based on Taylor series expansion presents a better performance for computing sin a cosine functions. However, the CORDIC architecture presents a better performance for computing the arctangent function. For validating the proposed circuits, several simulations were performed using the MATLAB (these results are used as a statistical estimator of the implemented floating point operators). The Mean Square Error (MSE) results have demonstrated the suitability the precision of the implemented operators.

Finally, in order to validate the functionality of the set of operators, a hardware architecture for computing the direct kinematics for a robot manipulator with a spherical topology with five degrees of freedom was developed. The proposed architecture was designed using a time and area constrained scheduling approach. In this case, cores in floating poitn were used, 8 cores for computing transcendental functions (sine and cosine), 4 multiplier and 2 addition/subtraction cores for computing the arithmetic operations. Synthesis results show that the proposed architecture is feasible for modern FPGAs families, in which there are plenty of logic elements available. The overall computations were successfully performed and also validated using the MATLAB results as a statistical estimator. The processing time of the hardware architecture was compared with the same kinematics model implemented in software, using both a hard PowerPC processor (embedded in the FPGA) and a MATLAB implementation running in an AMD Atlhon Dual-Core at 2.1GHz processor. The computation time to implement the direct kinematics in hardware is  $0.67\mu s$  (clock of 100 MHz), whereas the same formulation implemented in software using a PowerPC processor needs 1.61 ms, running in the same FPGA device and with the same clock. Additionally, the MATLAB implementation spends 0.013 ms (clock of 2.1 GHz).

# SUMÁRIO

| 1 | Intro | DUÇÃO                                                           | 1         |

|---|-------|-----------------------------------------------------------------|-----------|

|   | 1.1   | Generalidades                                                   | 1         |

|   | 1.2   | Descrição do Problema                                           | 2         |

|   | 1.3   | Objetivos                                                       | 4         |

|   | 1.3.1 | Objetivo Geral                                                  | 4         |

|   | 1.3.2 | Objetivos Específicos                                           | 4         |

|   | 1.4   | Justificativa                                                   | 4         |

|   | 1.5   | Resultados Obtidos                                              | 6         |

|   | 1.6   | Organização do Trabalho                                         | 6         |

| 2 | FUNDA | AMENTAÇÃO TEÓRICA                                               | 7         |

|   | 2.1   | Representação Numérica                                          | 7         |

|   | 2.1.1 | Representação em Ponto Fixo                                     | 7         |

|   | 2.1.2 | Representação em Ponto Flutuante                                | 8         |

|   | 2.1.3 | Padrão IEEE-754                                                 | 8         |

|   | 2.2   | Aspectos de Manipuladores Robóticos                             | 12        |

|   | 2.2.1 | O Robô Cartesiano                                               | 12        |

|   | 2.2.2 | O Robô Cilíndrico                                               | 13        |

|   | 2.2.3 | O Robô Esférico                                                 | 13        |

|   | 2.2.4 | O Robô SCARA                                                    | 13        |

|   | 2.2.5 | O Robô articulado                                               | 14        |

|   | 2.3   | Cinemática de Manipuladores                                     | 15        |

|   | 2.3.1 | Cinemática direta de manipuladores                              | 15        |

|   | 2.4   | Computação Reconfigurável                                       | 17        |

|   | 2.4.1 | Arquitetura interna de um FPGA                                  | 19        |

|   | 2.4.2 | Granularidade de Sistemas Reconfiguráveis                       | 20        |

|   | 2.4.3 | Processadores embarcados em FPGAs                               | 21        |

|   | 2.5   | Conclusões do Capítulo                                          | 23        |

| 3 | ALGOI | RITMOS USADOS NA IMPLEMENTAÇÃO DE OPERADORES ARITMÉTICOS EM     |           |

|   | Ponto | FLUTUANTE EM FPGA                                               | <b>25</b> |

|   | 3.1   | Trabalhos Correlatos à Implementação de Operadores Aritméti-    |           |

|   |       | COS DE PONTO FLUTUANTE EM HARDWARE                              | 25        |

|   | 3.2   | Algoritmos de operadores aritméticos básicos em ponto flutuante | 27        |

|                  | 3.2.1 | Soma/Subtração                                                  | 27         |

|------------------|-------|-----------------------------------------------------------------|------------|

|                  | 3.2.2 | Multiplicação                                                   |            |

|                  | 3.2.3 | Divisão                                                         |            |

|                  | 3.2.4 | Raiz Quadrada                                                   |            |

|                  | 3.3   | Algoritmos para implementação de operadores para funções trans- |            |

|                  |       | CENDENTAIS                                                      | 33         |

|                  | 3.3.1 | CORDIC                                                          | 33         |

|                  | 3.3.2 | Expansão em Séries de Taylor                                    | 37         |

|                  | 3.4   | Conclusões do Capítulo                                          | 38         |

| 4                | Овте  | nção da Cinemática Direta do Manipulador e sua Implementa-      |            |

|                  | ÇÃO E | M HARDWARE                                                      | 40         |

|                  | 4.1   | Trabalhos Correlatos à Implementação da Cinemática Direta em    |            |

|                  |       | Hardware                                                        | 41         |

|                  | 4.2   | Modelo cinemático Direto de um Robô Manipulador de Configu-     |            |

|                  |       | ração Esférica                                                  | 41         |

|                  | 4.3   | Verificação da metodologia de cálculo da cinemática direta (o   |            |

|                  |       | CASO DO ROBÔ PUMA)                                              | 43         |

|                  | 4.4   | Uso da metodologia proposta para o robô objeto do estudo        | 46         |

|                  | 4.5   | Implementação em FPGA da cinemática direta                      | 49         |

|                  | 4.6   | Conclusões do Capítulo                                          | 52         |

| 5                | Resui | TADOS                                                           | <b>54</b>  |

|                  | 5.1   | Implementação dos Operadores em VHDL                            | 54         |

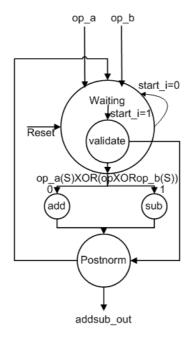

|                  | 5.1.1 | Unidade de Soma/Subtração                                       | 54         |

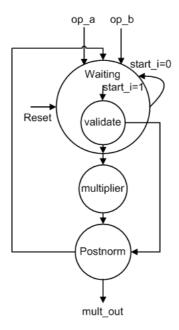

|                  | 5.1.2 | A unidade do Operador Multiplicação                             | 56         |

|                  | 5.1.3 | A unidade do Operador Divisão                                   | 57         |

|                  | 5.1.4 | Raiz Quadrada                                                   | 61         |

|                  | 5.2   | Cálculo de Funções Transcendentais                              | 62         |

|                  | 5.3   | Síntese e Simulação Funcional dos Operadores                    | 63         |

|                  | 5.3.1 | Resultados de Simulação                                         | 67         |

|                  | 5.4   | Resultados de Síntese e Simulação da Implementação da Cinemá-   |            |

|                  |       | tica Direta                                                     | 72         |

|                  | 5.5   | Conclusões do Capítulo                                          | 74         |

| 6                | Conc  | LUSÕES E SUGESTÕES PARA TRABALHOS FUTUROS                       | <b>7</b> 6 |

|                  | 6.1   | Considerações Gerais                                            | 76         |

|                  | 6.2   | Sugestões para trabalhos futuros                                | 78         |

| $\mathbf{R}^{1}$ | EFERÍ | ÈNCIAS BIBLIOGRÁFICAS                                           | 83         |

# LISTA DE FIGURAS

| 1.1  | Software versus Hardware (Modificado [1])                                            | 2  |

|------|--------------------------------------------------------------------------------------|----|

| 2.1  | Representa em ponto Fixo                                                             | 8  |

| 2.2  | Formato IEEE-754                                                                     | 9  |

| 2.3  | Robô Cartesiano e seu espaço de trabalho                                             | 13 |

| 2.4  | Robô Cilíndrico e seu espaço de trabalho                                             | 13 |

| 2.5  | Robô Esférico e seu espaço de trabalho                                               | 14 |

| 2.6  | Robô SCARA e seu espaço de trabalho                                                  | 14 |

| 2.7  | Robô Antropomórficoe seu espaço de trabalho                                          | 14 |

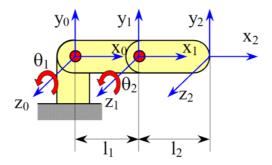

| 2.8  | Posição zero para juntas rotacionais.                                                | 16 |

| 2.9  | Algumas configurações de elos típicos.                                               | 18 |

| 2.10 | Acelerador em sistema embarcado (Modificado [2])                                     | 19 |

| 2.11 | FPGA de granularidade fina baseada numa arquitetura island                           | 19 |

| 2.12 | Diagrama de blocos de um CLB (Modificado [2])                                        | 20 |

| 2.13 | conexão de elementos internos de uma FPGA (Modificado [2])                           | 21 |

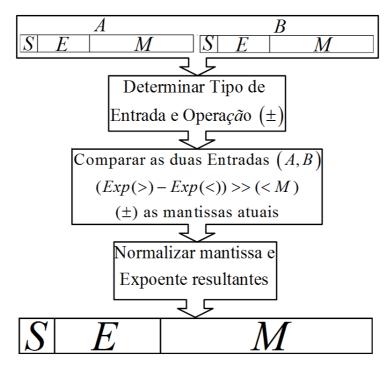

| 3.1  | Passos seguidos na implementação de soma/subtração em ponto flutuante                | 27 |

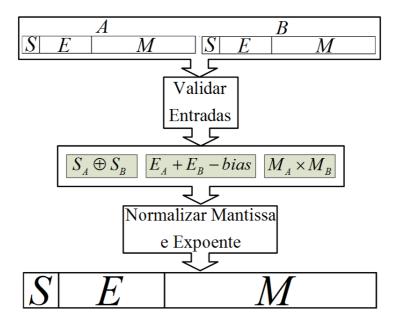

| 3.2  | Passos seguidos na implementação da multiplicação em ponto flutuante                 | 28 |

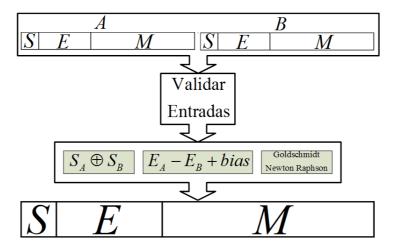

| 3.3  | Passos seguidos na implementação da divisão em ponto flutuante                       | 28 |

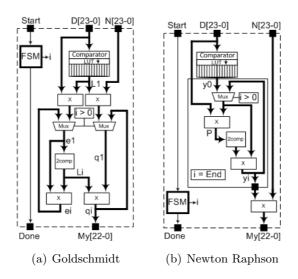

| 3.4  | Implementação do algoritmo Goldschmidt para divisão                                  | 30 |

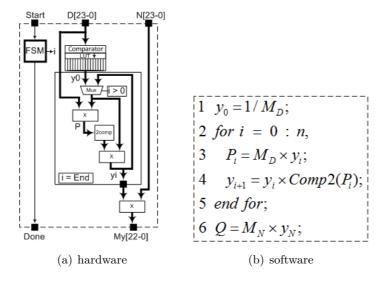

| 3.5  | Implementação do algoritmo Newton - Raphson para divisão                             | 30 |

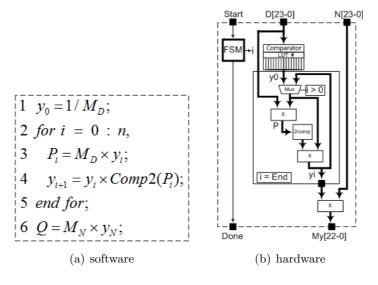

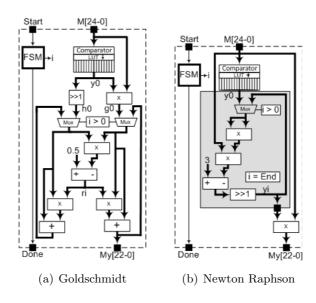

| 3.6  | Implementação do algoritmo Goldschmidt para raiz quadrada                            | 32 |

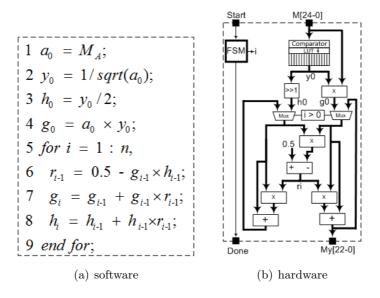

| 3.7  | Implementação do algoritmo Newton-Raphson para raiz quadrada                         | 33 |

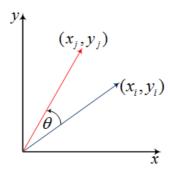

| 3.8  | Rotação do vetor $(x_i, y_i)$ por um ángulo $\theta$                                 | 33 |

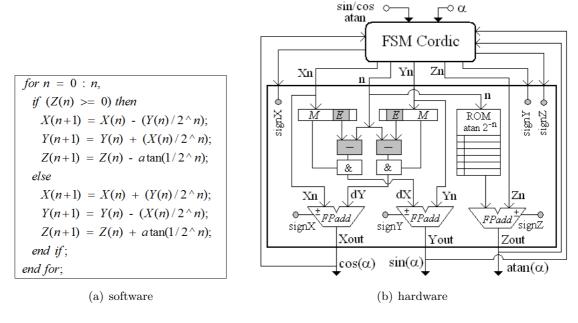

| 3.9  | Implementação do algoritmo CORDIC                                                    | 37 |

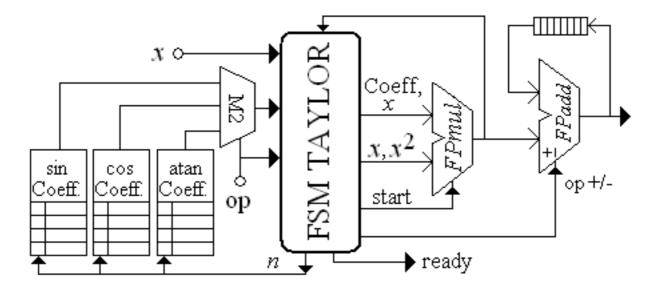

| 3.10 | Implementação das funções seno, cosseno e arco-tangente baseado em series de Taylor. | 38 |

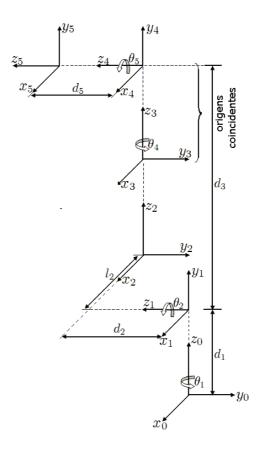

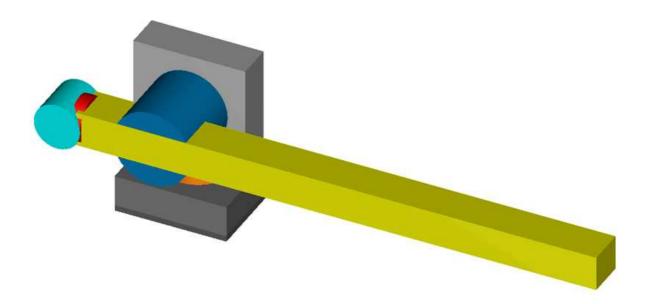

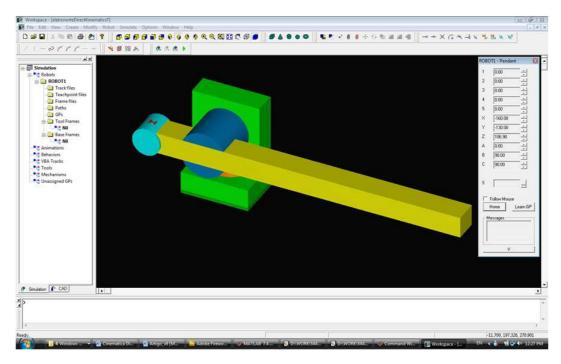

| 4.1  | Robô manipulador de 5 gruas de liberdade (objeto de estudo)                          | 42 |

| 4.2  | Atribuição de um marco de referencia para cada enlace                                | 43 |

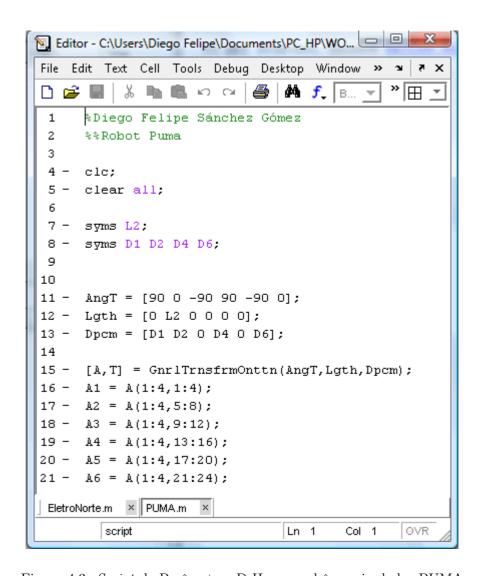

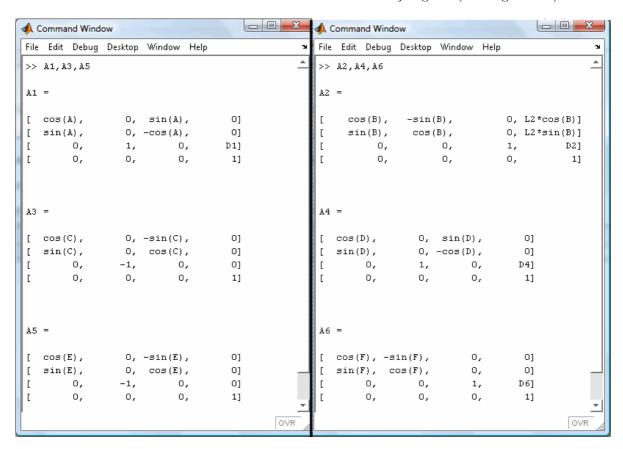

| 4.3  | Script de Parâmetros D-H para robô manipulador PUMA                                  | 44 |

| 4.4  | Matrizes obtidas para relação de marcos coordenados consecutivos do robô PUMA        | 45 |

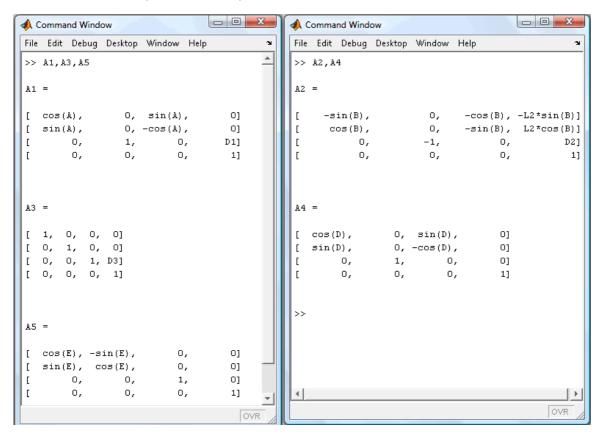

| 4.5  | Script de parâmetros D-H para robô manipulador caso de estudo                        | 47 |

| 4.6  | Posição zero real do robô.                                                           | 47 |

| 4.7  | Matrizes obtidas para relação de marcos de coordenadas consecutivos do robô esférico | 48 |

| 4.8  | Entorno de trabalho do Workspace                                                     | 49 |

| 4.9  | Arquitetura hardware para o cálculo da cinemática direta controlado por FSM                | 50 |

|------|--------------------------------------------------------------------------------------------|----|

| 4.10 | Arquitetura dentro da FPGA usando um processador Hard                                      | 51 |

| 4.11 | Algoritmo descrito em C para o cálculo da cinemática direta no processador PowerPC.        | 51 |

| 5.1  | Declaração em VHDL da entidade da unidade de soma subtração                                | 55 |

| 5.2  | Diagrama da máquina de estados do operador soma/subtração                                  | 55 |

| 5.3  | Parte do código em VHDL para implementar o operador soma                                   | 56 |

| 5.4  | Declaração da entidade do operador multiplicação                                           | 56 |

| 5.5  | Diagrama de estados para a unidade de multiplicação                                        | 57 |

| 5.6  | Estado $multiplier$ da unidade de multiplicação                                            | 57 |

| 5.7  | Arquiteturas usadas no cálculo do cociente da mantissa                                     | 58 |

| 5.8  | Gerador de código VHDL em MATLAB da unidade do operador divisão                            | 59 |

| 5.9  | Memória ROM gerada                                                                         | 59 |

| 5.10 | Comparadores e processo de acesso a memória para extrair a semente em VHDL                 | 60 |

| 5.11 | Processo em VHDL para o cálculo da mantissa usando o algoritmo Goldschmidt $\ldots\ldots$  | 60 |

| 5.12 | Processo em VHDL para o cálculo da mantissa usando o algoritmo Newton-Raphson              | 61 |

| 5.13 | Arquiteturas usadas no cálculo da mantissa na operação de raiz quadrada $\ldots\ldots$     | 61 |

| 5.14 | Processo em VHDL, para o cálculo da mantissa usando o algoritmo Goldschmidt $\ldots\ldots$ | 62 |

| 5.15 | Processo em VHDL para o cálculo da mantissa usando o algoritmo Newton-Raphson              | 63 |

| 5.16 | Gerador de código da função arco-tangente usando o algoritmo CORDIC                        | 64 |

| 5.17 | Ligações das tres unidades de soma usadas na implementação das micro-rotações. $\ldots$    | 65 |

| 5.18 | MSE da unidade FPTaylor para a função arco-tangente                                        | 71 |

| 6.1  | Arquitetura hardware usada no cálculo da cinemática direta                                 | 81 |

| 6.2  | Proposta de arquitetura hardware otimizada em tempo para o cálculo da cinemática           |    |

|      | direta                                                                                     | 82 |

# LISTA DE TABELAS

| 2.1  | Principais representações no padrão IEEE 754                                                         | 10 |

|------|------------------------------------------------------------------------------------------------------|----|

| 2.2  | Número real normalizado                                                                              | 10 |

| 2.3  | Número real desnormalizado                                                                           | 11 |

| 2.4  | Representação binária do QNAN e SNaN.                                                                | 11 |

| 2.5  | Representação do Infinito.                                                                           | 11 |

| 2.6  | Representação do Zero                                                                                | 12 |

| 2.7  | funções armazenadas numa LUT                                                                         | 20 |

| 2.8  | processadores hard e Soft disponibilizados por os fabricantes (Modificado $[3]$ )                    | 22 |

| 2.9  | processadores hard e Soft disponibilizados por os fabricantes (Modificado [3])                       | 23 |

| 4.1  | Parâmetros de Denavit-Hartenberg paro o robô caso de estudo                                          | 42 |

| 4.2  | Parâmetros D-H, para o robô manipulador PUMA                                                         | 43 |

| 5.1  | Resultados de síntese unidades de soma/subtração e multiplicação. Virtex<br>2 $\rm XCV6000$ 66       |    |

| 5.2  | Resultados de síntese das unidades de divisão com LUT 8. Virtex<br>2 $\mathrm{XCV}6000$              | 66 |

| 5.3  | Resultados de síntese das unidades de raiz quadrada com LUT 16. Virtex2 XCV6000                      | 67 |

| 5.4  | Resultados de síntese funções transcendentais. Virtex2 XCV6000                                       | 68 |

| 5.5  | $\operatorname{MSE}$ das unidades de soma/subtração e multiplicação para diferentes larguras de bits | 68 |

| 5.6  | MSE das unidades de divisão e raiz quadrada mudando o tamanho da LUT                                 | 69 |

| 5.7  | MSE das unidades de divisão e raiz quadrada mudando o número de iterações                            | 69 |

| 5.8  | Comparação dos algoritmos Goldschmidt e Newton-Raphson                                               | 70 |

| 5.9  | MSE das funções transcendentais mudando o número de iterações                                        | 70 |

| 5.10 | Comparção dos algoritmos CORDIC e expansão en séries de Taylor                                       | 72 |

| 5.11 | Resultados de síntese da arquitetura para o cálculo da cinemática direta. Virtex2                    |    |

|      | XC2VP30                                                                                              | 72 |

| 5.12 | MSE em diferente tamanhos de palavra da arquitetura para o cálculo da cinemática                     |    |

|      | direta                                                                                               |    |

| 5.13 | Latência e passo no qual é calculada cada variável                                                   | 74 |

| 5.14 | Latência das implementações hardware e software (PowerPC e MATLAB))                                  | 74 |

## Capítulo 1

## Introdução

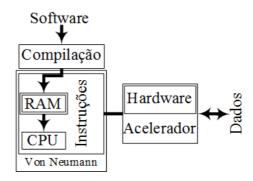

Aplicações como cálculo da cinemática direta e inversa na área da robótica, processamento digital de sinais e imagens, sistemas de controle e muitas outras aplicações cientificas precisam de alto número de operações aritméticas e trigonométricas que devem ser calculadas com alta precisão [4, 5]. De esta forma, a adoção de aritmética de ponto flutuante baseadas no padrão IEEE-754 é um requisito indispensável para este tipo de aplicações, comumente implementadas sobre processadores de propósito gerais (GPPs). A natureza seqüencial destes processadores (baseados na arquitetura ou modelo de von Neumann), e o fato de em alguns casos estes emulam operações de ponto flutuante em software, faz com que estes não sejam o suficientemente rápidos para algumas aplicações [1, 6, 7].

O continuo avance nas tecnologias de fabricação de circuitos integrados fez com que hoje tenhase uma alta capacidade de integração, permitindo implementar em hardware várias operações em ponto flutuante (comumente implementadas em software), aproveitando assim o paralelismo intrínseco tanto dos algoritmos como dos dispositivos reconfiguráveis como FPGAs, tendo como conseqüente um ganho no desempenho (velocidade de processamento) [8, 9, 10, 11].

Propor uma biblioteca de ponto flutuante para FPGAs que seja usável em aplicações como robótica é um grande desafio, já que permite explorar as potencialidades dos dispositivos FP-GAs e comparar com processadores embarcados no FPGA, tendo uma medida de velocidade de processamento entre as duas abordagens.

### 1.1 Generalidades

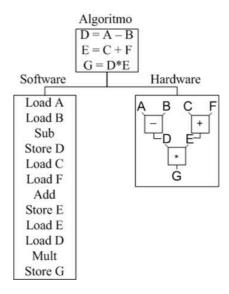

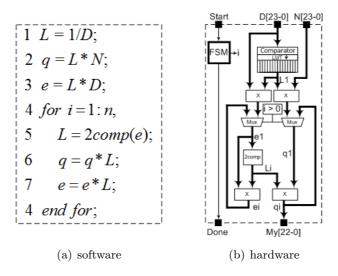

Uma das principais vantagens ao usar implementações em hardware de algoritmos é a execução em paralelo que pode ser obtida. Na figura 1.1 é mostrado um comparativo entre uma implementação hardware e uma implementação software [1]. Na implementação software, se cada linha do programa é executada em 1 ciclo de relógio o resultado G, é produzido em 12 ciclos de relógio; porém, na implementação hardware esta mesma implementação levaria 2 ciclos de relógio.

Por outro lado, para que um robô poda-se movimentar e manipular objetos precisa-se de uma adequada localização, baseada em ferramentas matemáticas que permitem localizar em posição e orientação um objeto (extremo do robot) no espaço tridimensional. O estudo da cinemática do

Figura 1.1: Software versus Hardware (Modificado [1])

robô permite relacionar a posição dos atuadores com a posição e orientação do extremo final do robô [12].

Um clássico pero importante problema na área da robótica de manipuladores é a cinemática direta que permite a localização cartesiana do extremo final do robô a partir do conhecimento da posição/ângulos nas articulações [13, 12]. A cinemática direta é uma formulação matemática que freqüentemente necessita de um elevado número de operações aritméticas e trigonométricas que, idealmente, devem ser calculadas em aritmética de ponto flutuante.

### 1.2 Descrição do Problema

Em uma arquitetura digital os números são representados usando seqüências binárias de largura finita, o que leva a erros de quantização na representação de parâmetros da implementação e erros de arredondamento nas operações aritméticas. Além do anterior, os erros dependem da aritmética usada na implementação [14, 15].

Em muitas aplicações científicas, devido a limitações da faixa de valores de números representados usando aritmética de ponto fixo, pode-se gerar erros de *overflow* e *underflow*. De esta forma, para se representar tanto números grandes como pequenos precisa-se de uma grande quantidade de bits. Uma solução a este problema é a utilização de aritmética de ponto flutuante, que permite representar em um registro de bits com um tamanho adequado, números pequenos e grandes ao mesmo tempo [16, 5].

Se uma rotina de cálculo é implementada em um GPP dispondo de aritmética de ponto flutuante, esta é a escolha mais natural. Por outro lado, é comum em implementações em hardware usar aritmética de ponto fixo visando economia em térmos de área do chip [17, 15].

Uma má escolha do formato numérico no qual se operam e representam os números pode levar a falhas no cálculo, causando catástrofes que levam à perda de vidas e recursos materiais. Uma

das falhas catastróficas encontradas na literatura foi a do míssil Patriot descrito embaixo.

Em 25 de fevereiro de 1991, durante a guerra do Golfo, o míssil americano Patriot falhou no caminho de interseção do míssil Scud iraquiano  $^{1\ 2}$ . O incidente causou a morte de 28 soldados e o ferimento de outras 100 pessoas. Um relatório técnico chegou à conclusão que a causa da falha foi uma incerteza nos cálculos de tempo devido a erros aritméticos computacionais. Especificamente, o tempo em décimas de segundos, medido pelo relógio interno do sistema foi multiplicado por 1/10 para produzir o tempo em segundos. Este cálculo foi executado usando um registrador de 24 bits em ponto fixo. Em particular, o valor 1/10, não é exatamente representável em uma expansão binária usando 24 bits. O erro acumulado em cada iteração foi acumulando-se, produzindo finalmente um erro final significante.

Por outro lado, na área de robótica atualmente há uma alta demanda de aplicações que operam a altas velocidades, procurando uma melhora em desempenho e obtendo benefícios em termos de eficiência da manufatura, precisão e tempo de processamento. Em geral, um sistema robótico executado em tempo real precisa de iterativas execuções de complexos algoritmos, que envolvem o uso de várias funções transcendentais e operações aritméticas. Muitos destes algoritmos, precisam ser computados na ordem de milissegundos (ms) ou microssegundos ( $\mu$ s), para alcançarem as restrições de tempo do sistema. Além disso, estes algoritmos necessitam de alto poder computacional que supera as capacidades de muitos computadores seqüências baseados na arquitetura von Neumann [7].

Como descrito acima, uma implementação em FPGAs (Field Programable Gate Array) permitiria aproveitar o paralelismo intrínseco desta abordagem. Porém, a falta de uma completa biblioteca em aritmética de ponto flutuante há limitado o uso dos FPGAs em aplicações que requerem de alta precisão. Ainda que as FPGAs têm sido usadas para a implementação de aritmética de ponto fixo, esta não é uma boa escolha quando a aplicação precisa trabalhar em uma faixa de valores que abranja tanto números muito pequenos como números muito grandes, como apresentado no caso da falha do míssil Patriot.

Representações numéricas em uma amplia faixa dinâmica, jogam um papel importante no projeto de controle de robôs. Normalmente um robô funciona em uma faixa limitada de movimentos que facilmente poderiam ser representados e manipulados usando processadores digitais de sinais de aritmética de ponto fixo. Porém, eventos inesperados poderiam acontecer na linha de montagem. Por exemplo, o robô poderia se travar, ou algum objeto poderia bloquear seu movimento. Neste caso, o laço de retro-alimentação poderia sair da faixa de operação, e o sistema baseado em um DSP de ponto fixo poderia não incluir um efetivo tratamento de condições não-usuais. Tendo uma implementação baseada num processador de ponto flutuante, devido à amplia faixa de números que podem ser representados, dificilmente o robô superaria a faixa de operação e se torna possível trabalhar com circunstâncias não-usuais de uma forma controlada [18].

<sup>&</sup>lt;sup>1</sup>http://ta.twi.tudelft.nl/users/vuik/wi211/disasters.html

<sup>&</sup>lt;sup>2</sup>http://www.ima.umn.edu/~arnold/disasters/patriot.html

<sup>3</sup>http://www.fas.org/spp/starwars/gao/im92026.htm

### 1.3 Objetivos

### 1.3.1 Objetivo Geral

Este trabalho tem como objetivo principal desenvolver, implementar e validar uma biblioteca aritmética de ponto flutuante parametrizável descrita em VHDL, com a finalidade de servir para implementação de arquiteturas totalmente paralelizadas de cinemática direta e inversa de manipuladores.

A biblioteca descrita neste trabalho inclui operações de soma/subtração, multiplicação, divisão, raiz quadrada e funções trigonométricas como seno, cosseno e arco-tangente, operadores comumente encontrados na implementação de cinemática de manipuladores.

### 1.3.2 Objetivos Específicos

Os objetivos específicos propostos para este trabalho são:

- Estudar, projetar simular e implementar diferentes algoritmos usados na implementação de operadores aritméticos básicos e transcendentais em hardware mediante o uso de arquiteturas reconfiguráveis.

- 2. Realizar um estúdio dos diferentes algoritmos implementados em quanto a área usada, desempenho, erro nos cálculos (precisão) e latência.

- 3. Mediante o uso da biblioteca aritmética desenvolvida, projetar, simular e implementar, direitamente em hardware, a cinemática direta de um robô manipulador de configuração esférica com 5 graus de liberdade.

- 4. Implementar a cinemática direta do manipulador em software mediante o uso de um processador embarcado PowerPC no FPGA.

- 5. Comparar o desempenho das implementações hardware e software.

### 1.4 Justificativa

Os primeiros trabalhos de implementação de aritmética de ponto flutuante foram projetados para primitivas FPGAs incluindo operações de soma e multiplicação [19, 20, 21]. Porém, estes trabalhos seminais mostram um excessivo custo do projeto em área. Os resultados obtidos nestes trabalhos mostram que implementar aritmética de precisão simples em FPGA era fatível mas pouco prático para a tecnologia disponível na época.

Nas primeiras implementações de unidades de ponto flutuante para FPGA observou-se uma grande quantidade de implementações dos operadores de soma/subtração e multiplicação. Por outro lado, foi dada pouca atenção a outros operadores tais como: divisão, raiz quadrada e funções transcendentais [22].

Modernas FPGAs possuem grandes quantidades de elementos lógicos, permitindo assim descrever em hardware cálculos complexos e novos algoritmos [23]. Recentemente, operações de aritmética de ponto flutuante usando precisão simples e dupla têm sido implementadas [24, 25, 26]. Mudar o tamanho da palavra nos operadores aritméticos é uma característica importante que permite satisfazer os requerimentos de precisão de acordo com a aplicação. Operadores aritméticos parametrizáveis só são possíveis em implementações baseadas em FPGAs, mas alem da precisão nos cálculo o projetista tem que se preocupar em evitar um sobre-dimensionamento do hardware.

Algumas bibliotecas parametrizáveis em aritmética de ponto flutuante são apresentadas em [24, 27]. Estas bibliotecas implementam operações de soma/subtração, multiplicação e raiz quadrada. Porém, estas não apresentam um estudo detalhado com respeito ao erro nos cálculos (precisão). Além disto, não se tem implementado operadores para o cálculo de funções transcendentais indispensáveis em aplicações em robótica (por exemplo, seno, cosseno e arco-tangente).

Uma biblioteca bastante comum entre os projetistas é apresentada em [28]. Esta biblioteca é apresentada como uma Unidade Lógica Aritmética (ULA), que inclui os operadores soma, subtração, multiplicação, divisão e raiz quadrada. Porém, estes operadores não podem ser usados para executar cálculos em paralelo, e não são parametrizáveis.

A Xilinx tem desenvolvido uma biblioteca comercial de operadores parametrizáveis em ponto flutuante incluindo soma/subtração, multiplicação, divisão, raiz quadrada, comparadores e conversores de ponto fixo a ponto flutuante. Os operadores de divisão e raiz quadrada são ser implementados usando arquiteturas pipeline (uma entrada pode ser aplicada em cada ciclo de relógio) apresentando um baixo consumo de recursos, porém, uma elevada latência. Por exemplo, em aritmética de precisão dupla as operações de divisão e raiz quadrada são calculadas em 56 ciclos de relógio (tempo de espera entre a entrada dos operandos e saída do resultado) [29].

Implementar uma biblioteca parametrizável em aritmética de ponto flutuante baseada no padrão IEEE-754 tem como contribuição facilitar o uso das FPGAs em variadas aplicações em engenharia, dando ao projetista as ferramentas para construir sua aplicação, de uma forma rápida e flexível. Pequenas modificações no tamanho da palavra exigem uma adaptação dos elementos internos de cada operador, o que levaria ao projetista gastar mais tempo na implementação.

Por outro lado, na literatura são encontrados poucos trabalhos que implementam a cinemática de manipuladores em FPGAs. Trabalhos prévios mostram arquiteturas de hardware para implementar controladores dos servo-motores utilizados em manipuladores, onde a cinemática direta e inversa é computada em software [30, 31, 32, 33]. Em [30, 31], uma arquitetura de hardware para controlar um robô manipulador SCARA é apresentada, implementando o controle dos servo-motores em FPGAs e relevando o custo computacional aos GPPs.

Finalmente, considerando-se a importância que tem uma biblioteca parametrizável em aritmética de ponto flutuante em FPGAs, permitindo, assim, explorar o paralelismo intrínseco destes dispositivos em aplicações como cinemática de manipuladores, torna-se importante a implementação de uma arquitetura paralela para o cálculo da cinemática direta em aplicações que requerem altas velocidades de processamento com alta precisão nos cálculos.

### 1.5 Resultados Obtidos

Em este projeto foi desenvolvida uma biblioteca de operadores aritméticos em ponto flutuante parametrizáveis pelo tamanho da palavra. No intuito de automatizar a tarefa de mudar o tamanho da palavra de acordo com os requerimentos do projeto, foram desenvolvidos geradores de código escritos em MATLAB. Estes programas geram o código VHDL de cada operador de acordo com dados fornecidos pelo usuário em um *script*.

Para os operadores aritméticos de divisão e raiz quadrada foram propostas duas arquiteturas baseadas nos algoritmos Goldschmidt e Newton-Raphson. Da mesma forma foram propostas as arquiteturas baseadas no algoritmo CORDIC e expansão em séries de Taylor, para o cálculo de funções transcendentais seno, cosseno e arco-tangente.

Um análise de desempenho das arquiteturas propostas tendo em conta parâmetros como: (a) consumo de recursos do FPGA, (b) vazão (freqüência/latência) e (c) precisão, permitiu observar que a arquitetura baseada no algoritmo Newton-Raphson apresenta um melhor desempenho do que a arquitetura baseada no algoritmo Goldschmidt. Para o caso das funções transcendentais observa-se um melhor desempenho da arquitetura baseada em séries de Taylor para o cálculo das funções seno e cosseno. Embora para o cálculo da função arco-tangente a melhor escolha esta baseada no algoritmo CORDIC.

Finalmente, fazendo uso dos melhores algoritmos foi construída uma arquitetura para o cálculo da cinemática direta de um manipulador robótico de configuração esférica com cinco graus de liberdade. Esta arquitetura permitiu validar o funcionamento em conjunto dos operadores aritméticos em ponto flutuante e fazer um comparativo da implementação totalmente em hardware com duas implementações software. Uma das implementações em software é executada num processador hard PowerPC e a outra num computador usando MATLAB para executar os cálculos. Encontrou-se uma considerável aceleração no cálculo da cinemática direta em comparação com suas respectivas implementações em software.

### 1.6 Organização do Trabalho

O capítulo 2 apresenta a fundamentação teórica necessária para o desenvolvimento deste trabalho, abordando assuntos como representação numérica, representação numérica de números em ponto fixo e ponto flutuante, o padrão IEEE-754, cinemática direta de manipuladores e FPGAs. O capítulo 3 descreve os algoritmos de implementação de operadores aritméticos básicos e funções transcendentais. No capítulo 4 é apresentado o modelado matemático para obtenção da cinemática direta do robô manipulador de configuração esférica com cinco graus de liberdade e uma arquitetura para calcular a cinemática direta totalmente em hardware. O capítulo 5 mostra os resultados de sínteses e simulação dos operadores implementados e da arquitetura de hardware usada no cálculo da cinemática direta. Finalmente, no capítulo 6 são apresentadas as conclusões e trabalhos futuros.

## Capítulo 2

## Fundamentação Teórica

Este capítulo apresenta a fundamentação teórica dos temas abordados no desenvolvimento deste projeto. Inicialmente, é tratada a representação de números em sistemas digitais, tais como a representação de números em ponto fixo e ponto flutuante baseados no padrão IEEE-754. Seguidamente é feita uma breve introdução à robótica de manipuladores, mostrando as características e classificação. Por outro lado, é feito um estudo focado, principalmente, na cinemática direita de manipuladores robóticos. Finalmente, é abordado o tema relacionado à tecnologia de hardware utilizada neste trabalho, principalmente na tecnologia de hardware reconfigurável baseada em FPGA (Field Programmable Gate Array).

### 2.1 Representação Numérica

Em cada aplicação deve ser escolhido cuidadosamente o tipo de representação numérica a usar. Neste caso, implementações em hardware usando ponto fixo têm como vantagens baixo consumo de recursos e altas velocidades de processamento. Por outro lado, aritmética de ponto flutuante abrange uma grande faixa dinâmica de representação de números reais, apresentando um maior consumo de recursos [17].

### 2.1.1 Representação em Ponto Fixo

Um dos formatos amplamente usados para representar valores numéricos é o formato em ponto fixo. O mesmo deriva seu nome da localização fixa de um ponto binário implícito entre a parte inteira e a parte fracionaria. Uma representação em ponto fixo é descrita, comumente, por dois números n e m, onde n representa a parte inteira e m parte fracionaria. Por exemplo, um formato 16.0 representa um inteiro de 16-bits. Por outro lado, um formato 3.2 (ver Fig. 2.1) representa um número em ponto fixo com um total de 5 bits, um bit reservado para o sinal, 2-bits na parte inteira e 2 bits a direita do ponto implícito (parte fracionaria). O maior valor representável em este formato é  $011.11_b = 3,75_d$  e o menor valor é  $111.11_b = -3,75_d$  [34].

A velocidade, baixo custo, e simplicidade faz com que implementações em ponto fixo sejam amplamente usadas. Porém, devido a sua faixa limitada de valores, este formato é inadequado

|   |         | n     | m       |       |

|---|---------|-------|---------|-------|

| S | $n_{l}$ | $n_o$ | $m_{l}$ | $m_2$ |

Figura 2.1: Representa em ponto Fixo

para a maioria de aplicações cientificas e de engenharia que precisam processar números muito grandes e muito pequenos [5, 35].

### 2.1.2 Representação em Ponto Flutuante

A representação em ponto flutuante está baseada na notação cientifica, na qual o ponto decimal é movimentado dinamicamente até uma posição desejada, usando um expoente para indicar a posição original do ponto decimal. Por exemplo,  $976.000.000.000.000 = 9,76 \times 10^{14}$ . Esta notação permite abranger tanto números grandes como pequenos utilizando poucos algarismos. Nesta notação tem-se que o número é representado pela equação 2.1

$$N = M \times B^E \tag{2.1}$$

onde M representa a mantissa, B a base e E o expoente.

A idéia da notação cientifica é estendida aos números binários, sendo conhecida também como representação binária em ponto flutuante. Esta representação é amplamente usada em aplicações computacionais que requerem de uma amplia faixa de representação numérica.

#### 2.1.3 Padrão IEEE-754

O padrão IEEE-754 foi desenvolvido no intuito de padronizar a representação de números em ponto flutuante. No inicio da computação numérica, larguras de palavra de diferentes tamanhos eram criadas por cada fabricante; assim, ao executar um algoritmo em máquinas diferentes obtinhase resultados diferentes [36].

Em 1958, no intuito de encerrar a incompatibilidade entre sistemas, a organização IEEE propôs o padrão IEEE-754, estabelecendo a representação e modo de operação de números representados em ponto flutuante. O padrão teve as seguintes diretrizes [36]:

- Facilitar a migração dos programas já existentes para os novos computadores que adotem este padrão.

- Permitir aos programadores, que tenham experiência ou não em métodos numéricos, produzir programas numéricos sofisticados.

- Motivar aos programadores experientes a produzir e distribuir programas numéricos eficientes, robustos e portáveis.

- Apoiar o diagnostico de anomalias e, facilmente, manipular exceções.

- Permitir o desenvolvimento de: (a) funções elementares tais como expoentes e cossenos, aritmética de alta precisão e (b) permitir um acoplamento entre cálculos numéricos e simbólicos.

- Permitir, em vez de impedir, novos aperfeiçoamentos e ampliações para a proposta.

### O padrão IEEE-754 especifica:

- Formatos básicos e estendidos para números em ponto flutuante.

- Operações de soma, subtração, multiplicação, divisão, raiz quadrada, resto, e funções de comparação.

- Conversões entre inteiros e formatos em ponto flutuantes.

- Conversões entre diferentes formatos em ponto flutuantes.

- Conversões entre formatos básicos de números em ponto flutuante e cadeias de caracteres decimais (strings).

- Exceções e sua manipulação, incluindo NaN (Not a Number).

- Formatos de cadeias de bits decimais e inteiros

- Interpretação do sinal e campo de bit implícito da representação de NaN

- Conversões de binário para decimal e vice-versa.

#### O Formato IEEE 754

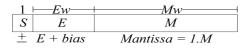

De acordo com o padrão IEEE-754 [36] um número real é representado por uma cadeia de bits caracterizados por três componentes: (a) um bit de signo S, (b) um expoente em excesso E com um largura de bits Ew e (c) uma mantissa M (parte fracionária) com uma largura de bits Mw (observar figura 2.2).

Figura 2.2: Formato IEEE-754

Um 0 no bit de sinal representa um número positivo e um 1 representaria um número negativo. O expoente tem seu próprio signo e é armazenado em excesso  $(2^{q-1}-1)$ , onde q é o número de bits). Por exemplo, se o expoente tem 8 bits, a representação em excesso é 127. Assim, o valor verdadeiro representado no expoente é igual a o valor armazenado subtraindo o excesso. Por exemplo, para um excesso de 127, se expoente tive-se armazenado o valor de 9, o valor verdadeiro representado no expoente seria: -118 = (9 - 127).

A mantissa representa um número fracionário normalizado, o que quer dizer, que o bit mais a esquerda da mantissa é sempre 1. Como este bit no muda de valor, não é armazenado; mais,

implicitamente faz parte da representação (o bit implícito). A mantissa M se calcula segundo a equação 2.2

$$M = m_{22} \times 2^{-1} + m_{21} \times 2^{-2} + \dots + m_1 \times 2^{-22} + m_0 \times 2^{-23}$$

(2.2)

O número real representado pela cadeia binária é obtido a partir da equação 2.3.

$$N = (-1)^{s} \times (1+M) \times 2^{E-Bias}$$

(2.3)

Dentro do padrão IEEE-754 tem-se principalmente duas representações: (a) precisão simples e (b) precisão dupla. Na tabela 2.1 são resumidas as características destas representações.

Tabela 2.1: Principais representações no padrão IEEE 754

| Precisão | Sinal | Expoente | Mantissa | Bais |

|----------|-------|----------|----------|------|

| Simples  | 1     | 8        | 23       | 127  |

| Dupla    | 1     | 11       | 52       | 1023 |

### Normalização do número sendo representado

Um número em ponto flutuante tem diferentes representações. Se o bit mais significativo da mantissa é diferente de zero a representação é dita normalizada [37]. Para evitar múltiplas representações para o mesmo valor, o mesmo deverá ser normalizado.

A operação de normalização em ponto flutuante consiste em deslocar a mantissa de modo que o bit más significativo seja igual a 1. Por cada deslocamento da mantissa o valor do expoente deve ser incrementado em uma unidade. Desta forma, somente o dígito 1 ficará na parte inteira (bit implícito), sendo esta informação redundante (só é necessário armazenar a parte fracionária). A única exceção a esta regra é o número zero, em que todos os bits (incluso o bit implícito) são iguais a zero [38]. Na tabela 2.2, pode-se observar o rango de representação de números normalizados usando aritmética de precisão simples.

Tabela 2.2: Número real normalizado

| Sinal | Expoente   | Mantissa                               |

|-------|------------|----------------------------------------|

| x     | 00000001 a | 00000000000000000000000000000000000000 |

|       | 11111110   | 111111111111111111111111               |

As últimas atualizações do padrão IEEE-754 incluem representação de números desnormalizados. Estes números têm o expoente em zero e a mantissa é usada para representar números entre zero e o menor número normalizado representado no formato. Em aritmética de precisão simples os números desnormalizados abrangem a faixa de valores entre  $(0, 1.1755E^{-38})$ . Na tabela 2.3, é mostrado como é representado um número real desnormalizado usando aritmética de precisão simples.

Tabela 2.3: Número real desnormalizado

|   | Expoente | Mantissa          |

|---|----------|-------------------|

| X | 00000000 | xxxxxxxxxxxxxxxxx |

### Valores especiais no formato IEEE 754

Neste formato são definidos valores especiais que permitem o tratamento de exceções, definindo códigos específicos dentro do formato para o posterior tratamento. Para definir estes valores específicos são usados os bits do expoente com todos seus campos em 1, com exceção do número zero [39].

O NaN (Not a Number) é usado para indicar operações inválidas. Uma operação é inválida se um dos operandos for inválido para a operação a ser executada. Por exemplo, soma ou subtração de valores de entrada  $+\infty$  ou  $-\infty$  infinito, multiplicação de  $0 \times \infty$ , divisão de 0/0 ou  $\infty/\infty$ , raiz quadrada de números menores que zero, entre outras.

Finalmente, o NaN tem duas representações: (a) QNaN (*Quiet NaN*) e (b) SNaN (*Signaling NaN*). O SNaN é caracterizado por ter o bit mais significativo da mantissa em 0, sendo é usado para indicar operações inválidas como as descritas anteriormente. O QNaN tem o bit mas significativo da mantissa em 1, e é usado em operações que não fornecem um resultado em ponto flutuante como nos casos de comparação e conversão de formatos. Na tabela 2.4, é mostrada a representação binária do QNAN e SNaN.

Tabela 2.4: Representação binária do QNAN e SNaN.

|       |          | 3                                      |       |

|-------|----------|----------------------------------------|-------|

| Sinal | Expoente | Mantissa                               | Valor |

| X     | 11111111 | 1xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | QNaN  |

| X     | 11111111 | 0xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx | SNaN  |

Os valores  $\pm \infty$ , são usados para indicar que houve uma divisão por zero, ou uma condição de overflow ou underflow. Estes são representados no formato como mostrado na tabela 2.5.

Tabela 2.5: Representação do Infinito.

| Sinal | Expoente | Mantissa                                | Valor     |

|-------|----------|-----------------------------------------|-----------|

| 0     | 11111111 | 000000000000000000000000000000000000000 | $+\infty$ |

| 1     | 11111111 | 000000000000000000000000000000000000000 | $-\infty$ |

Finalmente, o número zero tem duas representações no padrão IEEE-754 decorrentes da mudança do bit de sinal +0 e -0. Na tabela 2.6, é mostrada a representação do zero no formato IEEE 754.

Tabela 2.6: Representação do Zero.

| Sinal | Expoente | Expoente Mantissa                       |    |  |  |

|-------|----------|-----------------------------------------|----|--|--|

| 0     | 00000000 | 000000000000000000000000000000000000000 | +0 |  |  |

| 1     | 00000000 | 000000000000000000000000000000000000000 | -0 |  |  |

### 2.2 Aspectos de Manipuladores Robóticos

Nos últimos anos a robótica passou de ser um mito da imaginação de autores literários a uma realidade amplamente aceita no mercado produtivo. Entre as aplicações comumente encontrase que os robôs substituem o homem em tarefas repetitivas e hostis. Atualmente, podem ser encontrados em aplicações que incluem desde processos industrias a atividades diversas, tais como: segurança e vigilância, procura e salvamento, exploração planetária, exploração subaquática, entre outras aplicações.

Na área da robótica têm-se duas categorias principais, a saber: (a) robótica móvel e (b) robótica de manipuladores. O robô manipulador se caracteriza por ter a base fixa, e seu espaço de trabalho é limitado pelo alcance de seus elos. Por outro lado, os robôs moveis se caracterizam por sua capacidade de deslocamento em um ambiente [13].

De acordo com a ISO 8373, de 1994, um robô manipulador é definido como: "manipulador controlado automaticamente, reprogramável, de propósitos múltiplos, programável em três ou mais eixos, que podem ter base fixa ou móvel, para uso em aplicações industriais automatizadas" [40].

A configuração das juntas e a forma como são conectadas por meio dos elos definem o número de graus de liberdade em que o robô pode trabalhar, assim como a região dentro da qual o manipulador pode posicionar a ferramenta. Esta região é conhecida como espaço de trabalho do robô [13].

Os robôs podem ser classificados de acordo com a combinação entre juntas translacionais e rotacionais, assim como pela geometria do espaço de trabalho resultante. Dentre as combinações possíveis podem-se citar as 5 mais utilizadas do ponto de vista industrial: (a) cartesianos, (b) cilíndricos, (c) esféricos, (d) bi-cilíndrico ou SCARA e (e) articulado ou de revolução. Estas configurações são chamadas de clássicas e podem ser combinadas para dar lugar a novas configurações [13, 41].

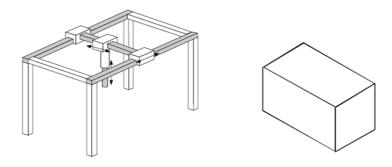

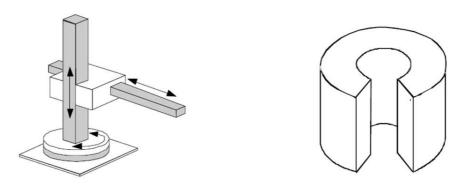

#### 2.2.1 O Robô Cartesiano

O robô cartesiano tem três articulações prismáticas atuando em cada eixo (x, y, z) (ver figura 2.3). Este se caracteriza pela alta rigidez mecânica e sua capacidade de operar com grande exatidão na localização do atuador, sendo que seu controle é simples devido ao seu movimento linear. A principal desvantagem é a sua pequena área de trabalho. Um robô com estas características é capaz de se localizar em qualquer ponto de um cubo.

Figura 2.3: Robô Cartesiano e seu espaço de trabalho

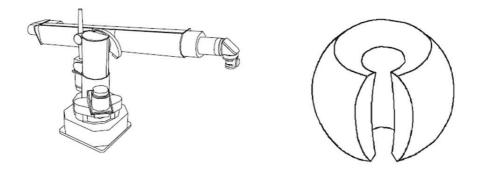

### 2.2.2 O Robô Cilíndrico

Este robô se caracteriza por ter duas jutas prismáticas e uma rotacional, situadas como mostrado na figura 2.4. Possui um espaço de trabalho maior que a do robô cartesiano, se comparado ao volume ocupado pela sua estrutura, sacrificando, entretanto a rigidez mecânica, e elevando a complexidade no controle.

Figura 2.4: Robô Cilíndrico e seu espaço de trabalho

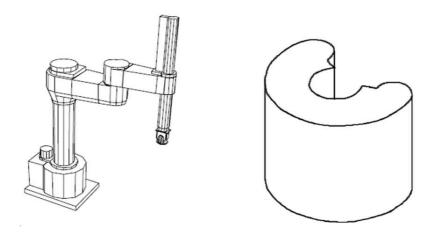

### 2.2.3 O Robô Esférico

O robô esférico consiste de duas juntas rotacionais, com eixos perpendiculares entre si, e uma junta prismática. As juntas rotacionais propiciam movimentos de azimute e de elevação e a junta prismática, de distância radial, resultando em um posicionamento representado por coordenadas polares (ver figura 2.5). A principal vantagem dos manipuladores que usam esta configuração é abranger um espaço de trabalho maior que seus pares cartesianos e cilíndrico, comparado ao volume ocupado pela estrutura do robô. Contudo, os robôs que usam esta configuração, apresentam a desvantagem de ter relativamente menor resolução e rigidez mecânica [41].

### 2.2.4 O Robô SCARA

O robô SCARA é formado por duas juntas rotacionais com eixos paralelos e uma junta prismática paralela aos eixos rotacionais, como mostrado na figura 2.6. Este robô tem um espaço de trabalho menor ao robô de configuração esférica comparando suas estruturas mecânicas. Entre-

Figura 2.5: Robô Esférico e seu espaço de trabalho

tanto, o mesmo tem uma grande capacidade de manobrar no plano horizontal, alta aceleração e boa rigidez mecânica na direção vertical.

Figura 2.6: Robô SCARA e seu espaço de trabalho

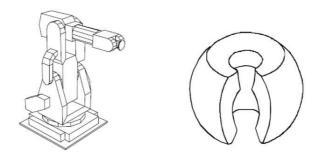

### 2.2.5 O Robô articulado

Este robô é composto somente por juntas rotacionais dispostas como mostrado na figura 2.7. A principal vantagem desta configuração é seu grande espaço de trabalho comparado ao volume ocupado pelo robô. Entretanto, apresenta desvantagens como cinemática complexa, movimentos lineares difíceis de controlar e estrutura complacente.

Figura 2.7: Robô Antropomórficoe seu espaço de trabalho.

### 2.3 Cinemática de Manipuladores

A cinemática de manipuladores tem por objetivo relacionar a posição e orientação do extremo final do robô com os valores assumidos pelas suas coordenadas articulares, existindo dois problemas fundamentais a serem resolvidos: (a) o problema cinemático direto e (b) o problema cinemático inverso.

No problema cinemático direto a posição e orientação do órgão terminal do robô, com respeito a um sistema de coordenadas fixo, são determinadas a partir dos valores das articulações e da configuração geométrica do robô. No problema cinemático inverso, pretende-se encontrar os valores das articulações para localizar o elemento terminal em uma posição e orientação desejada [13, 12].

Este trabalho tem por objetivo a implementação de uma biblioteca de operadores aritméticos em ponto flutuante para serem embarcados no FPGA, que permita calcular operações comumente encontradas na cinemática de manipuladores. Estes operadores serão usados na implementação totalmente em hardware do problema cinemático direto. A continuação será tratada com maior detalhe a cinemática direta de manipuladores.

### 2.3.1 Cinemática direta de manipuladores

Um clássico, porém importante problema na área de robótica industrial é a cinemática direta. A cinemática direta permite a localização cartesiana do elemento terminal do robô a partir da medida dos ângulos ou deslocamentos das juntas [13, 12, 41]. Este procedimento baseia-se, fundamentalmente na álgebra matricial e vetorial.

Um robô poderia ser considerado como uma cadeia cinemática conformada por uma série de elos que conectam o elemento terminal à base. Cada elo é conectado ao próximo por uma junta atuada [13, 12]. Associando um sistema de coordenadas para cada elo, a relação entre dois elos consecutivos pode ser descrita por uma matriz de transformação homogênea A. A seqüência de matrizes A relaciona o elemento terminal à base (ver equação 2.4) [13].

$${}^{R}T_{H} = A_{1}A_{2}\cdots A_{n-1}A_{n} \tag{2.4}$$

Desta forma o problema cinemático direto é resumido em obter uma matriz de transformação homogênea T que localize (posição e orientação) do elemento terminal do robô, com referência ao sistema de coordenadas fixado em sua base. Os elementos desta matriz são funções dos ângulos e deslocamentos entre os elos, que podem ser fixos (parâmetros geométricos) ou variáveis (variáveis das juntas do manipulador) [13, 12].

Para determinar a relação de um ponto no espaço cartesiano da base, em função de um ponto no espaço das juntas é seguido o seguinte procedimento [13]:

- 1. Mover o robô à posição zero.

- 2. Atribuir um sistema de coordenadas para cada elo.

- 3. Descrever as relações (translações e rotações) entre os sistemas de coordenadas de cada elo.

- 4. Definir as matrizes  $A_i$  de localização relativa entre os sistemas de coordenadas dos elos.

- 5. Multiplicar as matrizes para calcular a matriz de transformação homogênea do manipulador  ${}^{R}T_{H}$ .

- 6. Igualar a matriz de transformação homogênea do manipulador e a matriz de transformação geral a qual é obtida por meio das coordenadas cartesianas da posição que se quer atingir no espaço (posição almejada), relativas ao sistema de coordenadas fixado na base do robô, e da orientação de um sistema de coordenadas fixado na mesma posição almejada descrito por uma seqüência de três rotações em torno dos eixos do sistema de coordenadas da base.

### 2.3.1.1 A Posição zero (Home position)

A posição zero de um manipulador é a posição onde todas as articulações variáveis do manipulador são zero. As articulações rotacionais estão em sua posição zero quando o eixo x dos marcos de coordenadas dos enlaces sejam paralelos e tenham a mesma direção (ver figura 2.8). Uma junta prismática está na sua posição zero quando a distancia entre os enlaces é mínima (recolhida).

Figura 2.8: Posição zero para juntas rotacionais.

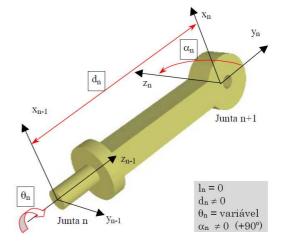

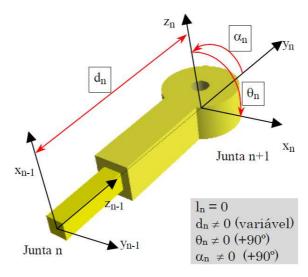

Para atribuir um sistema de coordenadas a cada elo são seguidas as convenções de Denavit e Hartenberg (D-H), por meio das quais dois elos consecutivos são relacionados por meio de 4 transformações básicas que só dependem da geometria do robô [13].

As transformações são:

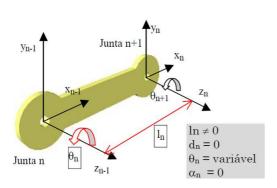

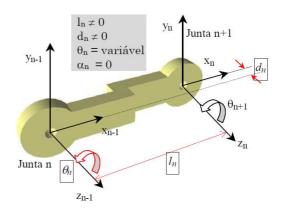

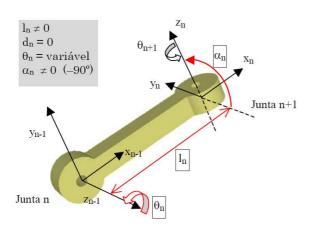

- 1. Uma rotação ao redor do eixo  $z_{n-1}$  (eixo da junta n-1) por o ângulo formado entre as direções das normais comuns a dois elos consecutivos (elo n-1 e elo n)( $\theta_n$ ).

- 2. Uma translação (transversal) ao longo do eixo da junta  $z_{n-1}$  da distância entre as juntas  $(d_n)$ . Esta é obtida a partir da distância entre os pontos de cruzamento, no eixo  $z_{n-1}$ , das normais comuns aos elos n-1 e n.

- 3. Uma translação, ao logo da normal comum do elo n, do comprimento do elo  $(l_n)$ . A direção da normal comum do elo n define a direção do eixo  $x_n$ .

- 4. Rotação em torno do eixo  $x_n$  por um ângulo  $\alpha_n$  com o objetivo de modificar a direção do eixo z, inicialmente paralela ao eixo  $z_{n-1}$  da junta n-1, de modo a torná-lo paralelo a direção do eixo da junta n ( $z_n$ ).

A multiplicação das transformações acima resulta na matriz A que define a posição relativa entre os sistemas de coordenadas atribuídos a elos consecutivos, conforme mostra a equação 2.5 [13].

$$A_{n} = R(z, \theta_{n})T(0, 0, d_{n})T(l_{n}, 0, 0)R(x, \alpha_{n})$$

$$= \begin{bmatrix} \cos(\theta) & -\sin(\theta) & 0 & 0 \\ \sin(\theta) & \cos(\theta) & 0 & 0 \\ 0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & l \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & d \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & \cos(\alpha) & -\sin(\alpha) & 0 \\ 0 & \sin(\alpha) & \cos(\alpha) & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

$$= \begin{bmatrix} \cos(\theta) & -\sin(\theta)\cos(\alpha) & \sin(\theta)\sin(\alpha) & l\cos(\theta) \\ \sin(\theta) & \cos(\theta)\cos(\alpha) & -\cos(\theta)\sin(\alpha) & l\sin(\theta) \\ 0 & \sin(\alpha) & \cos(\alpha) & d \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

$$(2.5)$$

Algumas configurações de elos típicos e o comportamento dos parâmetros  $d_n$ ,  $l_n$  and  $\alpha_n$  são mostrados na figura 2.9.

$\theta_n$ ,  $d_n$ ,  $l_n$  and  $\alpha_n$  representam os parâmetros de D-H do elo n. Identificando estes parâmetros a matriz A que relaciona dois elos consecutivos pode ser obtida. Finalmente, multiplicando a seqüência de matrizes A (ver equação 2.4) a matriz de transformação homogênea T é obtida. Esta, quando comparada à matriz de transformação homogênea resultante da localização almejada (matriz numérica), possibilita a obtenção da chamada cinemática direta do manipulador, a qual relaciona as coordenadas cartesianas da localização almejada como funções das coordenadas das juntas e dos parâmetros dos elos do manipulador [13].

### 2.4 Computação Reconfigurável

O paradigma baseado no fluxo de instruções de Von Neumann tem perdido seu domínio como modelo básico e único de sistemas computacionais. Hoje é comum que muitas aplicações desenvolvidas em software sejam migradas para aceleradores de hardware. Para isto, podem ser usados Circuitos Integrados para Aplicações Específicas (ASICs) ou sistemas reconfiguráveis baseados em FPGAs. Na figura 2.10 é mostrada a arquitetura de um acelerador baseado em um ASIC.

As FPGAs são dispositivos que oferecem a potencialidade de dispositivos ASICs , tais como: (a) redução de tamanho, peso, e consumo de potência, (b) alto desempenho, (c) maior segurança contra copias não autorizadas e (d) baixo custo. Além do anterior, FPGAs superam os ASICs em tempo de prototipagem, reprogramação do circuito, menor custo NRE (Non-recurring engineering), tendo como resultado projeto mais econômicos para soluções que precisem poucas quantidades de circuitos. Por outro lado, comparando com DSPs (Digital signal processing) e processadores de propósito geral, implementações em FPGAs podem explorar mais amplamente o paralelismo intrínseco dos algoritmos [17].

(a) Juntas Rotacionais Paralelas

(b) Juntas Rotacionais Paralelas com deslocamento

(c) Juntas Rotacionais Ortogonais

(d) Juntas Rotacionais Ortogonais Tipo<br/>  $2\,$

(e) Junta Rotacional e Prismática, Ortogonais

Figura 2.9: Algumas configurações de elos típicos.

Figura 2.10: Acelerador em sistema embarcado (Modificado [2])

### 2.4.1 Arquitetura interna de um FPGA

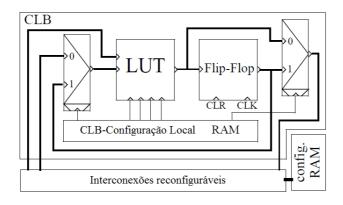

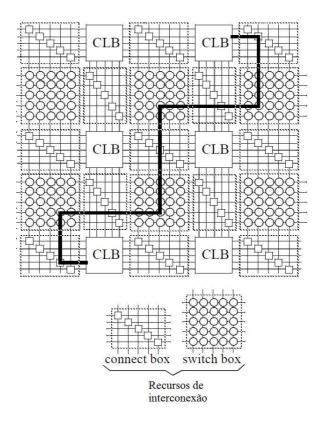

Entre as arquiteturas de FPGAs mais importantes encontramos: (a) arquiteturas island (Xilinx), (b) arquiteturas hierárquicas (Altera) e (c) arquiteturas row-based (Actel) [42]. Neste trabalho, será tratada com mais detalhe a arquitetura island da Xilinx, já que, as implementações feitas no desenvolvimento deste trabalho foram realizadas principalmente nestes dispositivos.

| Swithc box | Connect box | Swithe box  | Connect<br>box | Swithe box  | Connect<br>box | Swithc box  | Connect box | Swithe box  |

|------------|-------------|-------------|----------------|-------------|----------------|-------------|-------------|-------------|

| Connect    | CLB         | Connect box | CLB            | Connect     | CLB            | Connect box | CLB         | Connect box |

| Swithc box | Connect box | Swithe box  | Connect box    | Swithe box  | Connect box    | Swithc box  | Connect box | Swithc box  |

| Connect    | CLB         | Connect     | CLB            | Connect box | CLB            | Connect     | CLB         | Connect box |

| Swithc box | Connect     | Swithe box  | Connect        | Swithc box  | Connect box    | Swithe box  | Connect     | Swithc box  |

Figura 2.11: FPGA de granularidade fina baseada numa arquitetura island

Um FPGA é, basicamente, formado por uma matriz de Blocos Lógicos Configuráveis (CLB - Configurable Logic Blocks) incorporados em interconexões reconfiguráveis (ver figura 2.11). O código configware (código de reconfiguração) é armazenado em memórias RAM distribuídas. Uma vez que a FPGA é ligada, o código configware é carregado desde memórias RAM externas, geralmente de tipo FLEX.

A maioria de CLBs são baseados em LUTs (*Look Up Tables*), na figura 2.12 é mostrado um diagrama de blocos da arquitetura interna de um CLB. Seu principio de funcionamento está baseado na multiplexação de funções previamente armazenadas na LUT, como mostrado na tabela 2.7. Os elementos de roteamento do sistema (*switchbox* e os *connectbox*) servem para ligar os diferentes CLBs, sendo chamados de recursos de interconexão (ver figura 2.13). A configuração total

de todas as interconexões do dispositivo são realizadas por ferramentas de projeto assistido por computador (CAD), este procedimento é conhecido como posicionamento e roteamento (*Placement and Routing*).

Figura 2.12: Diagrama de blocos de um CLB (Modificado [2])

Tabela 2.7: funções armazenadas numa LUT

|                      | Tabela 2.7. Tunções armazenadas numa 1.0 f |    |         |                 |                           |  |  |

|----------------------|--------------------------------------------|----|---------|-----------------|---------------------------|--|--|

| Bits de configuração |                                            |    | guração |                 |                           |  |  |

|                      | local                                      |    |         | f(A,B)          | Função                    |  |  |

| g3                   | g2                                         | g1 | g0      |                 |                           |  |  |

| 0                    | 0                                          | 0  | 0       | 0               | Constante 0               |  |  |

| 0                    | 0                                          | 0  | 1       | A and B         | and                       |  |  |

| 0                    | 0                                          | 1  | 0       | B não implica A | if B then 0 else A        |  |  |

| 0                    | 0                                          | 1  | 1       | A               | Identidade A              |  |  |

| 0                    | 1                                          | 0  | 0       | A não implica B | if A then 0 else B        |  |  |

| 0                    | 1                                          | 0  | 1       | В               | Identidade B              |  |  |

| 0                    | 1                                          | 1  | 0       | A Xor B         | Xor                       |  |  |

| 0                    | 1                                          | 1  | 1       | A or B          | or                        |  |  |

| 1                    | 0                                          | 0  | 0       | not(A or B)     | nor                       |  |  |

| 1                    | 0                                          | 0  | 1       | A igual B       | Igualdade                 |  |  |

| 1                    | 0                                          | 1  | 0       | not(B)          | Negação de B              |  |  |

| 1                    | 0                                          | 1  | 1       | B implica A     | if A then 1 else $\neg B$ |  |  |

| 1                    | 1                                          | 0  | 0       | not(A)          | Negação de A              |  |  |

| 1                    | 1                                          | 0  | 1       | A implica B     | if B then 1 else $\neg A$ |  |  |

| 1                    | 1                                          | 1  | 0       | not(A and B)    | nand                      |  |  |

| 1                    | 1                                          | 1  | 1       | 1               | Constante 1               |  |  |

### 2.4.2 Granularidade de Sistemas Reconfiguráveis

Outro parâmetro importante em sistemas reconfiguráveis é a granularidade do sistema. Este fator é definido como o tamanho da menor unidade funcional que pode ser acessada por uma ferramenta de mapeamento (tamanho de grão). Como exemplo de granularidade pode-se citar o CLB que representa a menor unidade de configuração.

Figura 2.13: conexão de elementos internos de uma FPGA (Modificado [2])

Entre os dispositivos reconfiguráveis encontra-se os de granularidade fina e os de granularidade grossa. Os dispositivos de granularidade fina apresentam um grande número de elementos simples que podem ser interconectados para a formação de subsistemas digitais. Em sistemas complexos há um elevado grau de utilização destes elementos e, portanto, apresenta-se uma dificuldade na tarefa de roteamento. Adicionalmente, é necessário um número grande de dados de configuração (a configuração/reconfiguração é feita no nível de bits) para as unidades de processamento, o qual exige uma memória maior para o armazenamento dos dados de configuração, acarretando conseqüentemente, uma maior dissipação de potência [42].

Nos dispositivos de granularidade grossa os blocos de construção são maiores, tipicamente ULAs (Unidades lógico Aritméticas), microprocessadores, DSPs, e blocos de memória. Como pode-se ver estes dispositivos apresentam maior quantidade de lógica ou poder computacional nas unidades funcionais. Neste caso, a programação do FPGA é feito no nível de palavras (cadeias de caracteres) e não de bits (como no caso de dispositivos de granularidade fina).

### 2.4.3 Processadores embarcados em FPGAs

A elevada densidade de portas lógicas disponíveis em FPGAs atuais permite que hoje seja possível incorporar dentro destes dispositivos processadores que coexistem no mesmo chip. Alguns fabricantes oferecem processadores que diretamente estão incorporados dentro da FPGA (hardIP), e/ou processadores que podem ser baixados para a FPGA (SoftIP). O propósito de se ter um processador incorporado dentro da FPGA é prover uma base flexível combinando a potencialidade do software e hardware em um só dispositivo de silício [3].

Na tabela 2.8, são mostrados alguns processadores disponibilizados pelos fabricantes para serem usados com seus respectivos dispositivos.

Tabela 2.8: processadores hard e Soft disponibilizados por os fabricantes (Modificado [3])

| Processador   | Tipo    | Barramento         | Fabricante                |  |

|---------------|---------|--------------------|---------------------------|--|

| MicroBlaze    | Soft 32 | IBM Coreconnect    | Xilinx                    |  |

| Nios          | Soft 32 | Avalon             | Altera                    |  |

| LatticeMico32 | Soft 32 | Wishbone           | Lattice                   |  |

| CoreMP7       | Soft 32 | APB                | Actel                     |  |

| ARM Cortex-M1 | Soft 32 | AHB                | Distribuidor Independente |  |

| LatticeMico8  | Soft 8  | Input/Output ports | Lattice                   |  |

| Core8051      | Soft 8  | Nil                | Actel                     |  |

| Core8051s     | Soft 8  | APB                | Actel                     |  |

| PicoBlaza     | Soft 8  | Input/Output ports | Xilinx                    |  |

| PowerPC       | Hard 32 | IBM Coreconnect    | Xilinx                    |  |

| AVR           | Hard 8  | Input/Output ports | Atmel                     |  |

### Processadores Soft

Um processador soft é um microprocessador completamente sintetizável para depois ser implementado usando blocos lógicos e demais recursos disponíveis no FPGA. Neste caso, encontram-se processadores soft de 8 e 32 bits.

Dentre os processadores soft de 8 bits mais comuns encontra-se o PicoBlaze da Xilinx. Adicionalmente, para o caso de 32 bits encontra-se o NIOS da Altera e o MicroBlaze da Xilinx. Estes processadores usam uma parte fixa da área FPGA, deixando outra parte para incorporar lógica digital (mediante o processo de reconfiguração), fazendo possível aproveitar o paralelismo intrínseco dos algoritmos a serem mapeados em hardware.

#### Processadores Hard