# UNIVERSIDADE FEDERAL DO RIO GRANDE DO NORTE CENTRO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA E COMPUTAÇÃO

# eOSI: Um modelo para Desenvolvimento de Sistemas Embarcados Tolerantes a Falhas

## **Antônio Higor Freire de Morais**

Orientador: Prof. Dr. Gláucio Bezerra Brandão

Co-Orientadora. Profª. Dra. Ana Maria Guimarães Guerreiro

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica e Computação da UFRN (área de concentração: Engenharia de Computação) como parte dos requisitos para obtenção do título de Mestre em Ciências.

Natal/RN, 17 de Julho de 2009.

## **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

#### Divisão de Serviços Técnicos

Catalogação da Publicação na Fonte. UFRN / Biblioteca Central Zila Mamede

Morais, Antônio Higor Freire de.

eosi: um modelo para desenvolvimento de sistemas embarcados tolerantes a falhas / Antônio Higor Freire de Morais. – Natal, RN, 2009. 107 f.

Orientador: Gláucio Bezerra Brandão.

Co-orientador: Ana Maria Guimarães Guerreiro.

Dissertação (Mestrado) – Universidade Federal do Rio Grande do Norte. Centro de Tecnologia. Programa de Pós-Graduação em Engenharia Elétrica e Computação.

1. Tolerância a falha – Dissertação. 2. Sistemas embarcados – Dissertação. 3. FPGA – Dissertação. I. Brandão, Gláucio Bezerra. II. Guerreiro, Ana Maria Guimarães. III. Universidade Federal do Rio Grande do Norte. IV. Título.

RN/UF/BCZM

CDU 681.5.09(043.3)

## **Antônio Higor Freire de Morais**

| Projeto de Dissertação de Mestrado aprovada em de<br>bela banca examinadora composta pelos seguintes membros: | de 2009     |

|---------------------------------------------------------------------------------------------------------------|-------------|

|                                                                                                               |             |

|                                                                                                               |             |

|                                                                                                               |             |

| Prof. Dr. Gláucio Bezerra Brandão (Orientador)                                                                | DCA/UFRN    |

|                                                                                                               |             |

| Profa. Dra. Ana Maria Guimarães Guerreiro (Co-Orientador)                                                     | DCA/UFRN    |

|                                                                                                               |             |

| Prof. Dr. Ricardo Alexandro de M. Valentim (Avaliador Externo)                                                | DATINE/IERN |

"A glória de Deus é ocultar as coisas, a glória dos reis é pesquisá-las." (Pr 25, 2)

Dedico este trabalho à minha namorada

Por ser uma pessoa com um coração de ouro;

Pelo seu carinho e pelo seu amor.

Por isto, este trabalho é para você minha Princesa.

## **Agradecimentos**

Agradeço ao meu Bom Deus por não ter permitido que eu vacilasse em momento algum e por ter acalmado meu coração nos momentos de aflição.

À minha mãe, Francisca, e à minha bisavó, mãe Ana, meu muito obrigado por tudo que fizeram em minha vida. Obrigado pela formação do meu caráter e pelo amor incondicional.

Agradeço a minha querida namorada, Josi, que mesmo distante serviu-me como uma fonte de energia para que eu chegasse até este último degrau.

Ao meu amigo e orientador, Gláucio, só tenho que agradecer por todas as sábias perguntas que me foram feitas, fundamentais para o desenvolvimento desta Dissertação. Muito obrigado também pela ajuda dispensada, minha amiga e co-orientadora Ana Maria.

Meu caro amigo e parceiro Ricardo, todos os nossos debates foram igualmente importantes para que eu chegasse ao final dessa jornada. Muito obrigado amigo.

Um agradecimento especial a toda a turma do Laboratório de Automação Hospitalar e Bio-engenharia – LAHB. Obrigado ao meu camarada Diego (Diegão o homem do café, na ausência de Ricardo), Heitor (sempre com uma rapadura), Hélio (HB2 e seus comentários e suposições inesperadas). Obrigado a todos vocês pelos momentos de descontração e estudos.

Obrigado aos meus caros colegas da UFRN e aos servidores que nos dão o apoio necessário para possamos desenvolver nossas pesquisas.

## Resumo

A evolução das tecnologias em semicondutores possibilita que dispositivos sejam desenvolvidos cada vez mais com uma maior capacidade de processamento. Neste sentido, estes componentes passam a ter sua utilização ampliada para um maior campo de atuação. Ambientes da indústria petroleira, mineração, automotivos e hospitalares são exemplos de setores que estão utilizando tais dispositivos com maior frequência em seus processos. As atividades que são desenvolvidas por estas indústrias estão diretamente envolvidas com a segurança ambiental e a saúde daqueles que nela trabalham. Desta forma, torna-se mister a utilização de sistemas que sejam dotados de características de segurança extra que possam conferir a estes sistemas maior confiabilidade, segurança e disponibilidade. O modelo de referencia eOSI que será apresentado por esta Dissertação tem por objetivo permitir que estes sistemas sejam desenvolvidos sob uma nova perspectiva que facilite a escolha das estratégias de tolerância a falha a serem empregadas na aplicação. Como forma de validar a utilização deste modelo será apresentada uma arquitetura de suporte que foi desenvolvida em FPGA com base neste modelo.

Palavras chaves: Tolerância a falha, Sistemas embarcados, FPGA.

## **Abstract**

The semiconductor technologies evolutions leads devices to be developed with higher processing capability. Thus, those components have been used widely in more fields. Many industrial environment such as: oils, mines, automotives and hospitals are frequently using those devices on theirs process. Those industries activities are direct related to environment and health safe. So, it is quite important that those systems have extra safe features yield more reliability, safe and availability. The reference model eOSI that will be presented by this work is aimed to allow the development of systems under a new view perspective which can improve and make simpler the choice of strategies for fault tolerant. As a way to validate the model an architecture FPGA-based was developed.

Key words: Fault Tolerant, Embedded Systems, FPGA.

# Sumário

| SESSÃO 1                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                   |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1. INTROD                                                                                        | UÇÃO                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                                   |

| 1.2 OBJE                                                                                         | TIVO<br>TIVOS ESPECÍFICOS<br>ANIZAÇÃO DO TRABALHO                                                                                                                                                                                                                                                                                                                                                                                             | 16                                                                   |

| SESSÃO 2                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                   |

| 2. FUND                                                                                          | AMENTAÇÃO TEÓRICA                                                                                                                                                                                                                                                                                                                                                                                                                             | 18                                                                   |

| 2.1. 2.1.1. 2.1.2. 2.2. 2.2.1. 2.2.2. 2.2.3. 2.2.4. 2.2.5. 2.2.6. 2.2.7. 2.2.8. 2.2.9. 2.3. 2.4. | SISTEMAS EMBARCADOS E DISPOSITIVOS RECONFIGURÁVEIS ARQUITETURA RISC X ARQUITETURA CISC FPGAS E DISPOSITIVOS RECONFIGURÁVEIS TOLERÂNCIA A FALHAS E SISTEMAS REDUNDANTES TOLERÂNCIA A FALHAS DEPENDABILIDADE CONCEITOS CLÁSSICOS: FALHA, ERRO E DEFEITO FALHA E SISTEMAS COMPUTACIONAIS SISTEMAS REDUNDANTES REDUNDÂNCIA TEMPORAL REDUNDÂNCIA DE SOFTWARE REDUNDÂNCIA DA ÎNFORMAÇÃO REDUNDÂNCIA DE HARDWARE SISTEMAS DISTRIBUÍDOS CONSIDERAÇÕES | 20<br>23<br>28<br>28<br>29<br>31<br>32<br>34<br>35<br>36<br>37<br>41 |

|                                                                                                  | DO DA ARTE E TRABALHOS CORRELATOS                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| 3.1.<br>3.2.<br>3.3.                                                                             | MODELAGENS E ARQUITETURAS DE SISTEMAS                                                                                                                                                                                                                                                                                                                                                                                                         | 45<br>47                                                             |

| SESSÃO 4                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52                                                                   |

| 4. EOSI:                                                                                         | EMBEDDED OPEN SYSTEMS INTERCONNECTION                                                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                   |

| 4.1.<br>4.2.<br>4.2.1.<br>4.2.2.                                                                 | CONTEXTUALIZAÇÃO DO TRABALHOO MODELO EM CAMADASCAMADA DE APLICAÇÃOCAMADA DE DETECÇÃO                                                                                                                                                                                                                                                                                                                                                          | 53<br>56                                                             |

| 4.2.3.           | CAMADA DE RECUPERAÇÃO                                       | 57  |

|------------------|-------------------------------------------------------------|-----|

| 4.2.4.           | CAMADA DE REDUNDÂNCIA                                       | 58  |

| 4.2.5.           | CAMADA DE COMUNICAÇÃO                                       | 59  |

| 4.2.6.           | CAMADA DE ENLACE                                            | 60  |

| 4.2.7.           | CONSIDERAÇÕES SOBRE O FLUXO DE DADOS                        | 60  |

| 4.3.             | ESTUDO DE CASO                                              | 61  |

| 4.3.1.           | CAMADA DE APLICAÇÃO, DETECÇÃO E RECUPERAÇÃO                 | 62  |

| 4.3.2.           | CAMADA DE REDUNDÂNCIA                                       | 64  |

| 4.3.2.1.         | ALGORITMO DO MÓULO PRINCIPAL                                |     |

| 4.3.2.2.         | ALGORITMO DO MÓULO RESUNDANTE                               |     |

| 4.3.3.           | CAMADA DE COMUNICAÇÃO E ENLACE                              | 68  |

| 4.3.4.           | CONSIDERAÇÕES SOBRE A ARQUITETURA                           | 69  |

| SESSÃO 5         |                                                             | 71  |

| 5. IMPL          | EMENTAÇÃO E RESULTADOS                                      | 71  |

| 5.1.             | PLATAFORMA                                                  | 71  |

| 5.1.1.           | DISPOSITIVOS DE ENTRADA E SAÍDA                             |     |

| 5.1.2.           | Memória                                                     |     |

| 5.1.3.           | CLOCKS                                                      |     |

| 5.2.             | LINGUAGEM DE DESCRIÇÃO DE HARDWARE                          |     |

| 5.3.             | PROJETO EM NÍVEL DE TRANSFERÊNCIA ENTRE REGISTRADORES (RTL) |     |

| 5.3.1.           | CAMADA DE APLICAÇÃO                                         |     |

| 5.3.1.1.         | MÁQUINA DE ESTADOS – APLICAÇÃO                              |     |

| 5.3.2.           | CAMADA DE DETECÇÃO                                          |     |

| 5.3.1.1.         | MÁQUINA DE ESTADOS – DETECÇÃO                               | 77  |

| 5.3.3.           | CAMADA DE REDUNDÂNCIA — MÓDULO PRINCIPAL                    |     |

| 5.3.1.1.         | MÁQUINA DE ESTADOS – MÓDULO PRINCIPAL                       |     |

| 5.3.4.           | CAMADA DE REDUNDÂNCIA — MÓDULO SECUNDÁRIO                   |     |

| 5.3.1.1.         | MÁQUINA DE ESTADOS – MÓDULO SECUNDÁRIO                      |     |

| 5.3.5.           | ARQUITETURA GERAL                                           |     |

| 5.4.             | CASOS DE TESTE                                              |     |

| 5.4.1.           | PRIMEIRO TESTE – FLUXO DE ATUAÇÃO NORMAL                    |     |

| 5.4.2.           | SEGUNDO TESTE — CAMADA DE APLICAÇÃO                         |     |

| 5.4.3.           | TERCEIRO TESTE – CAMADA DE APLICAÇÃO OU DETECÇÃO            |     |

| 5.4.3.<br>5.4.4. | QUARTO TESTE – CAMADA DE REDUNDÂNCIA MASTER                 |     |

| 5.4.5.           | QUINTO TESTE – CAMADA DE REDUNDÂNCIA MASTER                 |     |

| 5.4.5.           | QUINTO TESTE - CAMADA DE REDUNDANCIA SECUNDANIA             | 93  |

| SESSÃO 6         |                                                             | 98  |

| 6. CON           | CLUSÕES                                                     | 98  |

| 6.1.             | Considerações Finais                                        | 98  |

| 6.2.             | Trabalhos Futuros                                           |     |

| REFERÊN          | CIAS BIBLIOGRÁFICAS                                         | 103 |

| BIBLIOGR         | ÁFIA                                                        | 103 |

# Lista de Figuras

| FIGURA 2.1: ARQUITETURA DE JOHN VON NEUMANN [STALLINGS, 2002]             | 19  |

|---------------------------------------------------------------------------|-----|

| FIGURA 2.2: ARQUITETURA DE UMA PAL [BROWN & ROSE, 1996]                   | 24  |

| FIGURA 2.3: ARQUITETURA DE UMA FPGA [GERICOTA, 2003]                      | 26  |

| FIGURA 2.4: CLASSIFICAÇÃO DAS FPGAS SEGUNDO A RECONFIGURABILIDADE [RIBEIF | ₹0  |

| 2002]                                                                     | 27  |

| FIGURA 2.5: FLUXOGRAMA DE CAUSA-EFEITO DE FALHAS [JOHNSON, 1984]          | 34  |

| FIGURA 2.6: MODELO DE REDUNDÂNCIA TMR [ABD-EL-BARR, 2007]                 | 38  |

| FIGURA 2.7: MODELO TMR COM REDUNDÂNCIA DE VOTADORES [KOREN & KRISHNA, 200 | )7  |

|                                                                           | 39  |

| FIGURA 2.8: MODELO DE REDUNDÂNCIA DINÂMICA [ABD-EL-BARR, 2007]            | 40  |

| FIGURA 2.9: MODELO DE REDUNDÂNCAI HÍBRIDA [ABD-EL-BARR, 2007]             | 41  |

| FIGURA 3.1: NÓ DA ARQUITETURA PROPOSTA POR HARIRI                         | 45  |

| FIGURA 3.2: ARQUITETURA PROPOSTA POR JEFERRY E FIGUEIREDO                 | 47  |

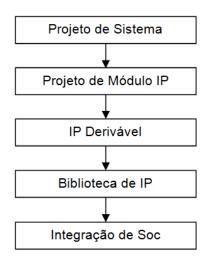

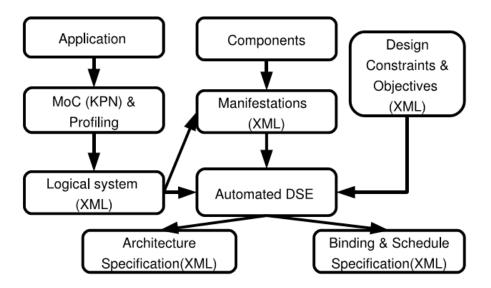

| FIGURA 3.3: FLUXO DE PROJETO DE SOC BASEADO EM PLATAFORMA                 | 48  |

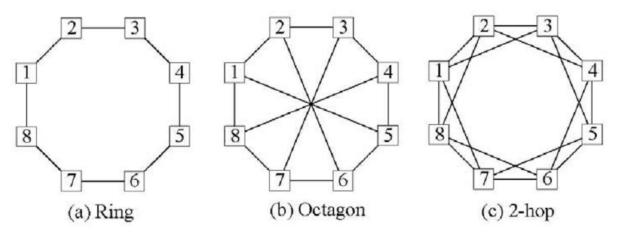

| FIGURA 3.4: CONJUNTO DE TOPOLOGIAS DO RO2 [CHEM ET. AL. 2007]             | 49  |

| FIGURA 3.5: FLUXO DE PROJETO EM NÍVEL DE SISTEMA [WU ET. AL. 2008]        | 50  |

| FIGURA 4.1: CAMADAS DO MODELO DE REFERÊNCIA EOSI [MORAIS ET. AL. 2009]    | 55  |

| FIGURA 4.2: FLUXO DE DADOS PARA O MODELO EOSI                             | 61  |

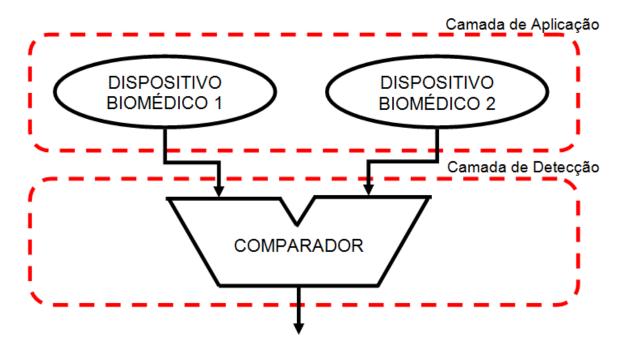

| FIGURA 4.3: ARQUITERURA DA CAMADA DE APLICAÇÃO E DETECÇÃO                 | 63  |

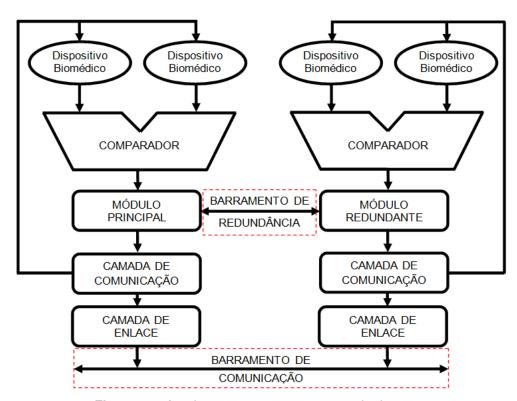

| FIGURA 4.4: ARQUITETURA PROPOSTA PARA O ESTUDO DE CASO                    | 69  |

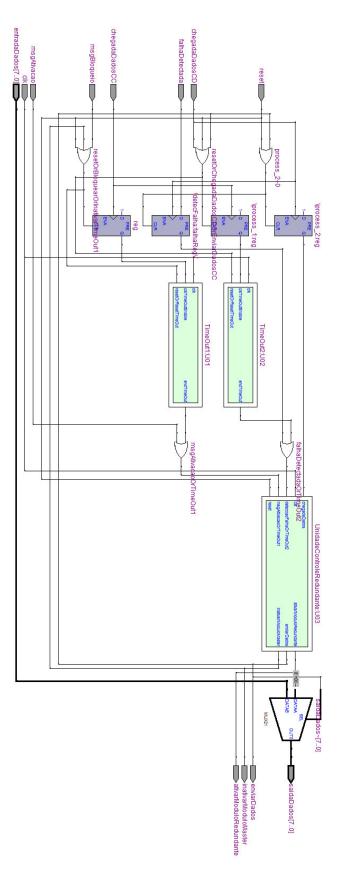

| FIGURA 5.1: RTL DA CAMADA DE APLICAÇÃO                                    | 75  |

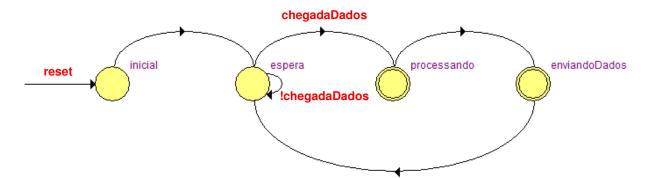

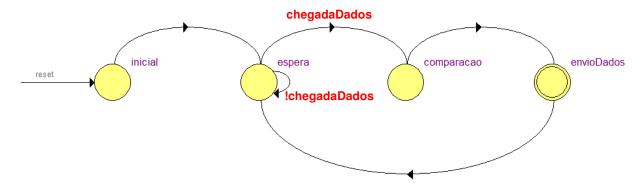

| FIGURA 5.2: MÁQUINA DE ESTADOS DO PROCESSADOR DA CAMADA DE APLICAÇÃO      | 76  |

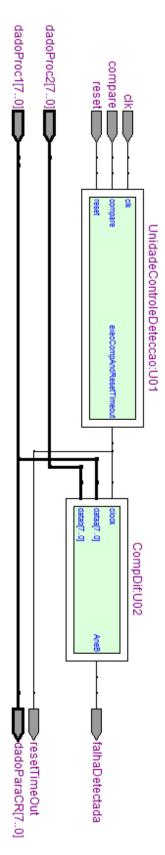

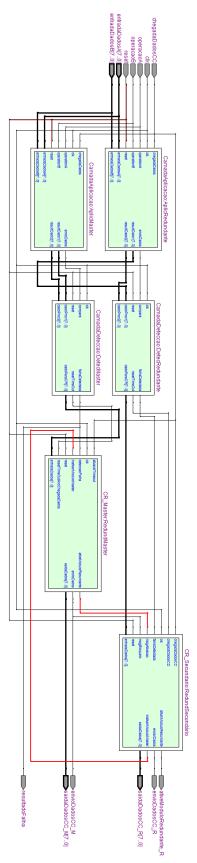

| FIGURA 5.3: RTL DA CAMADA DE DETECÇÃO                                     | 78  |

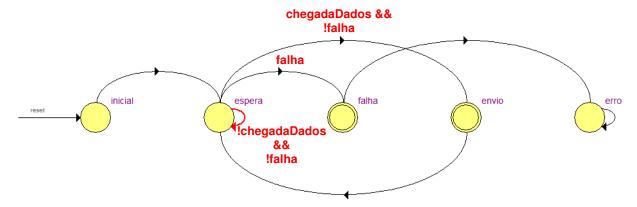

| FIGURA 5.4: MÁQUINA DE ESTADOS DO PROCESSADOR DA CAMADA DE DETECÇÃO       | 79  |

| FIGURA 5.5: MÁQUINA DE ESTADOS DO PROCESSADOR DA CAMADA DE REDUNDÂNCIA    | ١ - |

| MÓDULO PRINCIPAL                                                          | 80  |

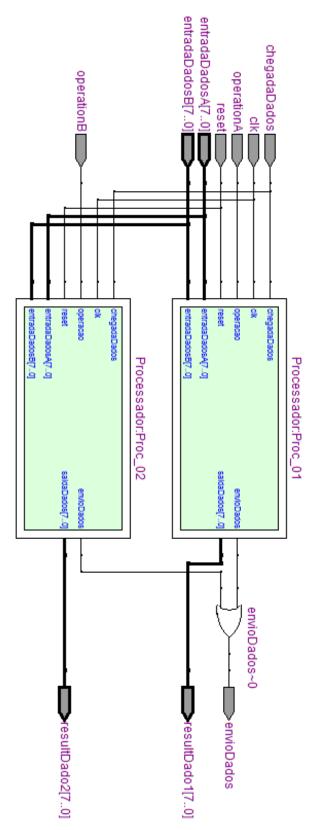

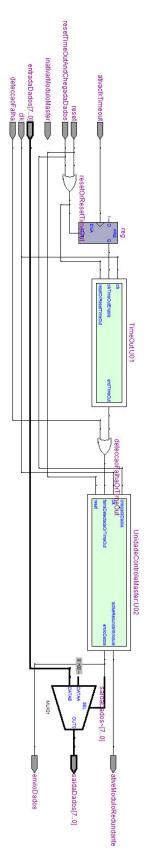

| FIGURA 5.6: RTL DA CAMADA DE REDUNDÂNCIA – MÓDULO PRINCIPAL            | 81  |

|------------------------------------------------------------------------|-----|

| FIGURA 5.7: MÁQUINA DE ESTADOS DO PROCESSADOR DA CAMADA DE REDUNDÂNCIA | A - |

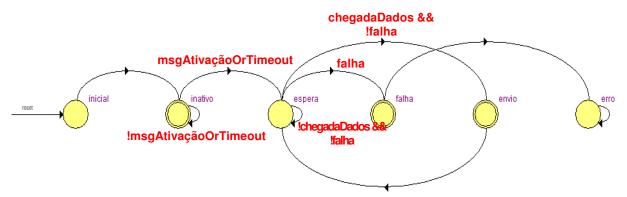

| Módulo Secundário                                                      | 83  |

| FIGURA 5.8: RTL DA CAMADA DE REDUNDÂNCIA — MÓDULO SECUNDÁRIO           | 84  |

| FIGURA 5.9: RTL DA ARQUITETURA SUPORTE GERAL                           | 86  |

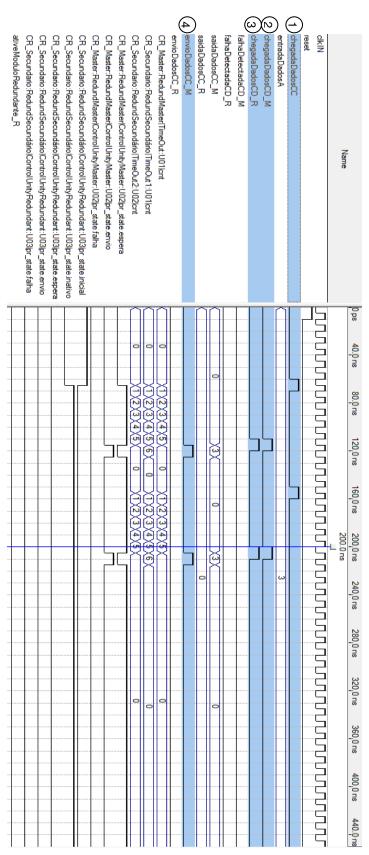

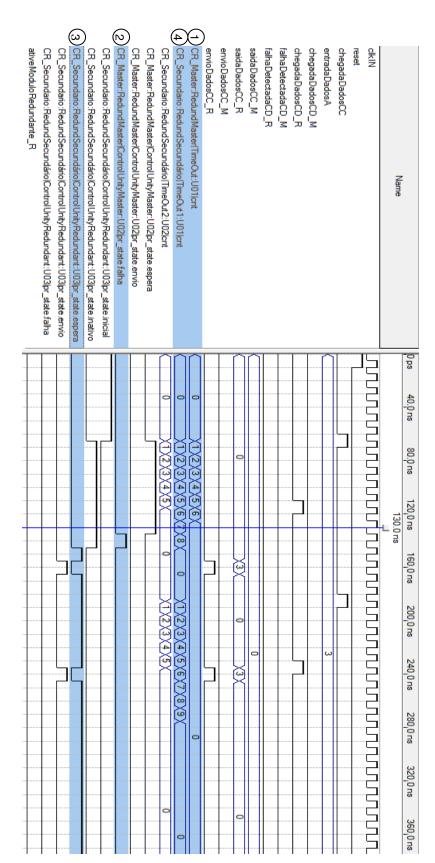

| FIGURA 5.10: FLUXO NORMAL DE OPERAÇÃO                                  | 88  |

| FIGURA 5.11: FALHA DETECTADA PELA CAMADA DE DETECÇÃO                   | 90  |

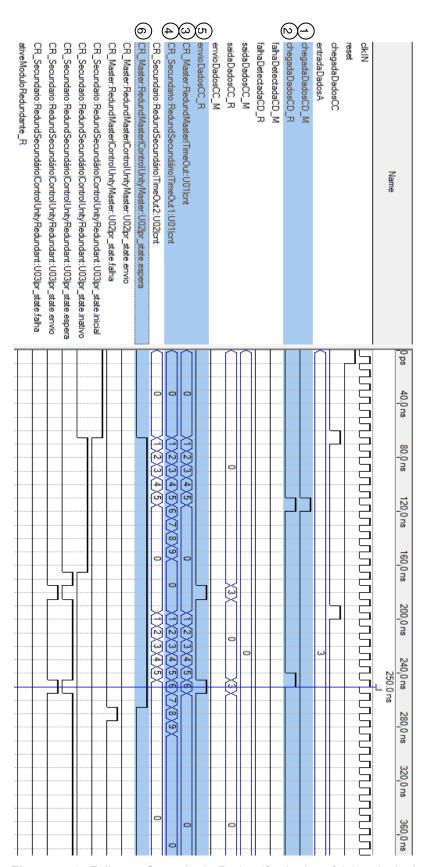

| FIGURA 5.12: FALHA DE NÃO CHEGADA DE DADOS PARA CAMADA DE REDUNDÂNCIA  | 92  |

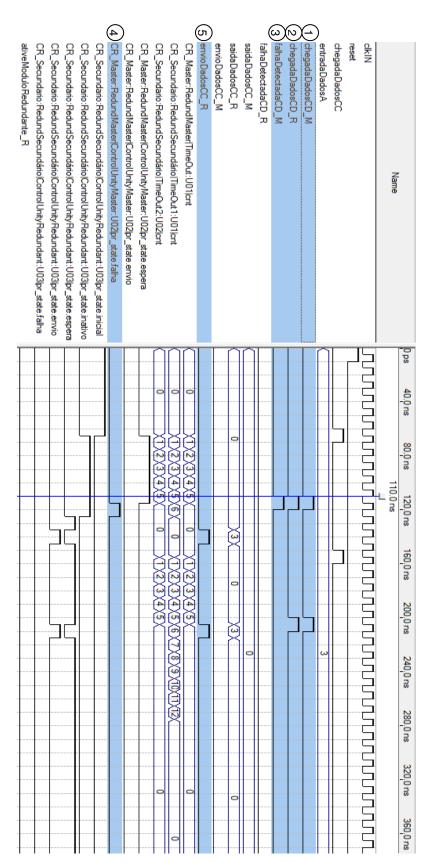

| FIGURA 5.13: FALHA NA CAMADA DE REDUNDÂNCIA DO MÓDULO PRINCIPAL        | 94  |

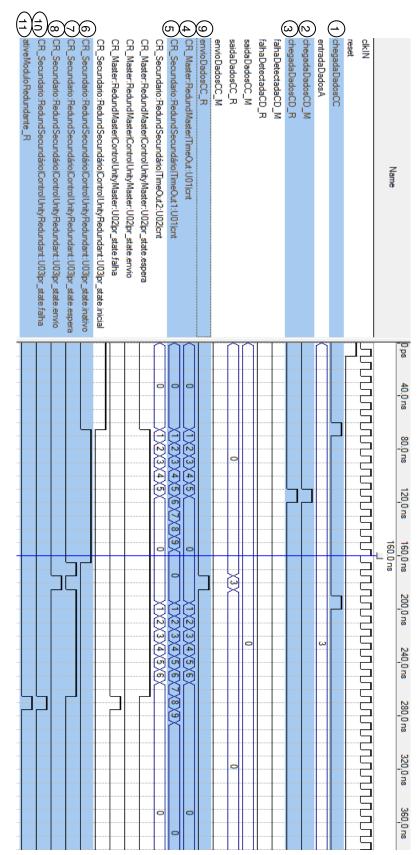

| FIGURA 5.14: FALHA PELA CAMADA DE REDUNDÂNCIA DO MÓDULO SECUNDÁRIO     | 96  |

# Lista de Equações

| EQUAÇÃO 4.1 | 65 |

|-------------|----|

| EQUAÇÃO 4.2 | 67 |

# Lista de Quadros

| QUADRO 4.1: ALGORITMO DO MÓDULO PRINCIPAL  | 64 |

|--------------------------------------------|----|

| QUADRO 4.2: ALGORITMO DO MÓDULO SECUNDÁRIO | 6  |

# Lista de Gráficos

| Gráfico 2.1: Comparação entre sistem | AS REDUNDANTES E NÃO REDUNDANTES [KOREN |

|--------------------------------------|-----------------------------------------|

| & Krishna. 20071                     | 39                                      |

## Lista de Acrônimos

ANSI/ISA American National Standards Institute/Instrument Society of

America

ASIC Application-Specific Integrated Circuit

CI Circuito Integrado

CISC Complex Instruction Set Computer

CLB Configurable Logic Block

CPLD Complex Programmable Logic Device

CRC Cyclic Redundancy Check

DSE Design Space Eploration

ECC Error Detection Code

EEPROM Electrically-Erasable Programmable Read-Only Memory

EDA Eletronic Design Automation

ESL Eletronic System Level

FPGA Field-Programmable Gate Array

FPLA Field-Programmable Logic Array

ILP Integer Linear Programing

IP Intellectual Property

IPI Intellectual Property Interface

ISO International Standards Organization

KNP Khan Process Network

LUT Lookup-Table

MSRS Motorola Semiconductor Reuse Standards

MPSoC Micro-Processor System-on-Chip

NASA National Aeronautics and Space Administration

NMR *N-Modular Redundancy*

NoC Network-on-Chip

OSI Open Systems Interconection

PAL Programmable Array Logic

PCI Peripheral Component Interconnect

PLD Programmable Logic Device

PROM Programmable Read-Only Memory

RAM Random Access Memory

RISC Reduced Instruction Set Computer

RF Rádio Frequência

RTL Register Transfer Level

SoC System-on-Chip

TCP Transmission Control Protocol

TMR Triple-Modular Redundancy

ULA Unidade Lógica Aritmética

VHDL Very High Speed Integrated Circuits Hardware Description

Language

VMM Virtual Machine Monitor

XML eXtensible Markup Language

## Sessão 1

### 1. Introdução

O cenário da microeletrônica mundial atualmente passa por uma revolução no desenvolvimento de sistemas embarcados, desde sua forma de concepção física à complexidade com que são projetados. A complexidade e heterogeneidade dos sistemas embarcados que são desenvolvidos vem crescendo rapidamente ao longo da última década [Vermeulen et. al. 2008]. Estes tipos de sistemas microprocessados estão, cada vez mais, fazendo parte do nosso dia-a-dia, sejam eles em computadores pessoais sejam em sistemas automotivos. Neste sentido, faz-se necessário a criação de níveis de abstração para o desenvolvimento de *System-on-Chip* (SoC), de tal forma que a equipe de desenvolvedores possa ser gerenciada e analisada, durante o desenvolvimento do projeto, para que a quantidade de erros (erros de projeto) seja a menor possível [Lahtnen, 2006]. As pessoas que integram a equipe de projetistas de um sistema embarcado são especializadas no desenvolvimento de *software* e *hardware*, cada qual atendendo às necessidades particulares do projeto.

Esta necessidade de criação organizada de projetos fez com que alguns padrões fossem pensados e elaborados com este fim. Atualmente, um conceito que trata das questões referentes às abstrações de projeto é chamado de *Electronic System Level* (ESL). Os conceitos que são abordados pelo ESL estão destinados ao desenvolvimento de cinco metodologias de projetos que podem ser encontradas em [Lahtinen, 2006]. Tais conceitos referem-se a questões de desenvolvimento de *hardware* e *software* para sistemas embarcados de forma concorrente. Algumas das causas que impulsionaram a criação destas metodologias de projetos estão no fato de que o tempo gasto com *re-design* e o risco de erros de projetos tendem a ser menor quando se desenvolve um projeto de forma estruturada.

A forma de comunicação entre software-software, software-hardware e hardware-hardware, bem como o mecanismo de troca de informações entre os

elementos de um sistema embarcado é um tema abordado por [Gervini et. al. 2003]. Estes são fatores de grande importância quando se trata de projetos de SoC, pois estes parâmetros estão intimamente associados: à potência consumida pelo sistema; à área que será ocupada pelo SoC na pastilha de silício; e à velocidade de processamento e desempenho alcançado pelo SoC. Ao se projetar um sistema embarcado, o projetista deve estar atento aos compromissos e especificações do projeto. Normalmente, a melhoria de um requisito afeta as características do outro. Por exemplo, um ganho em desempenho de processamento pode levar ao consumo de uma maior área ocupada pelo processador e/ou aumento de consumo de energia.

A linha que separa cada um destes elementos deve ser observada com atenção para que o requisito de uma dada característica do sistema não comprometa o escopo do projeto. Apesar da importância destes *tradeoffs*<sup>1</sup>, este trabalho não está preocupado com a minimização destes fatores no tocante aos projetos de sistemas embarcados. Embora sejam considerações que devam ser observadas quando da elaboração de projetos deste tipo, outras questões relacionadas às metodologias de projeto, segurança de sistemas, integridade e disponibilidade necessitam de um estudo mais aprofundado por parte da comunidade acadêmica.

Os ataques a sistemas embarcados é um tema abordado por Diguet em [Diguet et. al. 2007]. Os autores tratam de questões referentes à integridade de dados e autenticidade de entidades, os quais podem ser verificados através do monitoramento de comportamentos anormais de comunicação [Diguet et. al. 2007]. Temas relacionados à garantia da entrega de dados e fatores intrínsecos de segurança de informação são pontos que podem ser explorados de maneira mais apurada nestes projetos. Não é escopo deste trabalho discutir de forma aprofundada métodos de desenvolvimento de sistemas embarcados visando um menor consumo de área e potência ou melhora de desempenho.

O modelo de referência *Open Systems Interconection* (OSI) surgiu em função da necessidade de se ter um modelo que formalizasse o mecanismo de comunicação entre os computadores. Tal metodologia foi necessária para que os

<sup>&</sup>lt;sup>1</sup> Termo originário do inglês e utilizado para situações em que há conflito de escolha. Neste caso, a escolha de um determinado componente que melhor dada característica resultará no prejuízo de outra

fabricantes pudessem desenvolver produtos que fossem capazes de trocar informações independentemente de *drivers*. Este modelo foi formalmente desenvolvido pela *International Standards Organization* (ISO) e também é conhecido como modelo ISO/OSI.

A ANSI/ISA-95, ou ISA-95, é um padrão que trata da forma de criação de interfaces entre sistemas de controle e sistemas corporativos. Este padrão visa estabelecer uma forma eficiente para que estas aplicações possam trocar informações de uma forma segura, robusta, com um melhor custo-benefício, de tal forma que a integridade entre os dois sistemas seja preservada [ANSI/ISA-95.00.01, 2000]. Assim como o modelo OSI da ISO, a ISA-95 preocupa-se com a forma de comunicação entre sistemas e, devido a esta preocupação, ela sugere um modelo mais específico para os sistemas de controle e automação.

## 1.1 Objetivo

O objetivo desta Dissertação é apresentar uma metodologia para desenvolvimento de sistemas embarcados que tem como base um modelo de representação em camadas. O foco desta metodologia de desenvolvimento concentra esforços sobre questões voltadas à disponibilidade de sistemas/dispositivos em redes, utilizando como base conceitos de tolerância à falhas e sistemas distribuídos, empregando técnicas de redundância em *hardware*.

Esta forma de desenvolvimento segmentado irá permitir que o projeto seja desenvolvido com um maior desacoplamento entre as partes e, conseqüentemente, uma maior agilidade para desenvolvimento de projetos. Esta segmentação facilitará a prática de gerenciamento, devido ao fato do projeto estar sendo pensando em camadas logicamente separadas. Isto fará com que o projetista tenha uma visão abstrata da representação do sistema embarcado, aumentando as chances de detecções de falhas de projeto em um tempo menor.

#### 1.2 Objetivos específicos

Os trabalhos científicos são fundamentados em teorias e pesquisas que comprovem a veracidade do que está sendo apresentado. A fundamentação teórica é o suporte que é utilizado para apresentar o objeto de estudo. Como forma de consolidar este trabalho é apresentado um estudo de caso que demonstra um exemplo de arquitetura que emprega os conceitos do modelo de referência *Embedded Open Systems Interconnection* [Morais et. al. 2009]. Este modelo servirá para estabelecer uma divisão hierárquica de níveis de responsabilidades que possam determinar funcionalidades específicas de um sistema embarcado, de tal forma que seja possível um desenvolvimento organizado e estruturado deste sistema. Além disso, este modelo permite uma visão abstrata de alto nível com relação ao sistema que será implementado o que facilita a compreensão deste para a equipe de desenvolvedores. Desta forma, destacam-se como objetivos específicos deste trabalho:

- Estudo das principais propostas no meio acadêmico para metodologias de sistemas embarcados;

- Elaboração de um modelo em camadas para desenvolvimento de sistemas embarcados baseado em redundância em *hardware* e tolerância à falhas;

- Elaboração de uma arquitetura de suporte baseada no modelo de referência eOSI voltada para problemas de disponibilidades;

- Implementações de técnicas de redundância em hardware em uma Field-Programmable Gate Arrays (FPGA) para aumento da confiança e disponibilidade do sistema e validação da Camada de Redundância do modelo eOSI;

#### 1.3 Organização do trabalho

A estrutura organizacional desta Dissertação está definida da seguinte forma: no Sessão 1 é feita uma breve contextualização do trabalho e apresentação da proposta; no Sessão 2 serão apresentados conceitos referentes à redundância em hardware, sistemas tolerantes a falhas, sistemas distribuídos e demais assuntos associados a esta proposta. A análise destas técnicas de tolerância a falhas será necessária para a implementações que serão demonstradas na Sessão 4; a Sessão 3 é destinado ao estudos de trabalhos correlatos e estado da arte; na Sessão 4 são apresentadas as camadas que devem ser utilizadas como referência para os projetos de sistemas embarcados tolerantes a falhas. Como parte da consolidação deste trabalho foi implementado um sistema embarcado baseando-se no modelo de referência eOSI. Tal sistema é parte complementar a Tese de Doutorado desenvolvida por Valentim em [Valentim, 2008] que apresenta um protocolo multiciclo, baseado em IGMP Snooping, para automação hospitalar. A Sessão 5 apresenta o resultado da implementação da arquitetura de suporte tolerante a falha que é apresentada na Sessão 4. Na Sessão 6 são feitas as considerações finais do trabalho de dissertação de mestrado e sugestões a cerca de trabalhos futuros.

## Sessão 2

## 2. Fundamentação Teórica

Nesta Sessão são abordadas as pesquisas e tecnologias em torno do objeto de estudo desta Dissertação, bem como os conceitos básicos que serviram de ferramenta para elaboração da mesma.

### 2.1. Sistemas Embarcados e Dispositivos Reconfiguráveis

O século 20 foi marcado como um período de grandes revoluções para a ciência e tecnologia no âmbito do processamento de informações. Em 1945, John Von Neumann propôs um modelo de arquitetura para computadores que vem sendo usado até os dias atuais. Sua arquitetura é constituída por três características principais: a existência de um programa; uma unidade de processamento com funcionalidades particionadas; e um ciclo de busca-decodificação-execução [Yi & Lilja, 2006].

O programa é unidade responsável pela descrição das ações que serão tomadas pelo sistema de acordo com os valores de entrada que são passados (interações com um usuário ou valores de sinais digitais, por exemplo). Este programa pode estar gravado diretamente no *hardware* ou armazenado em uma memória, comumente chamada de memória de programa. Para o caso em que o programa está armazenado em memória faz-se necessário que o processador, a cada passo que é executado, carregue as instruções armazenadas. Destas duas abordagens podemos concluir que: a opção pelo armazenamento do programa em memória diminui o desempenho que pode ser alcançado pelo sistema, quando comparado ao que suas instruções fixas em *hardware* podem alcançar. Porém, o ganho é desempenho implica na perda de flexibilidade e uma vez fabricados não podem ter seu programa alterado. O mesmo não acontece com os processadores que tem o programa armazenado em memória. Estes processadores podem ser

utilizados para aplicações diversas e podem ter a função do programa modificada facilmente por meio de uma nova programação.

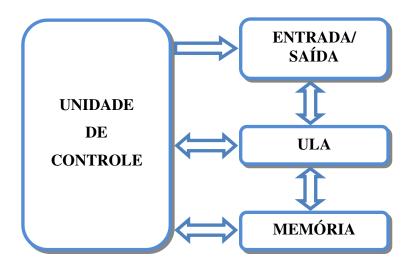

O segundo ponto, que define a arquitetura física da máquina de Von Neumann, é certamente o mais importante do modelo. A Figura 2.1 ilustra um exemplo da arquitetura de Von Neumann. Ela é composta por uma Unidade Lógica Aritmética (ULA) responsável pelo processamento das informações; uma memória que pode ser utilizada tanto para armazenamento de dados quanto para o armazenamento do programa; dispositivos de entrada e saída, responsáveis pela aquisição e envio de sinais, que realizam a interface com o usuário e o ambiente externo; e uma unidade de controle que gerencia as operações de processamento da ULA, bem como o armazenamento das informações na memória e as atividades dos dispositivos de entrada e saída.

Figura 2.1: Arquitetura de John Von Neumann [Stallings, 2002]

O último ponto é destacado pela forma de operação do processador. Na verdade trata-se dos processadores que possuem as instruções do programa armazenadas em memória, as quais para serem executadas devem ser buscadas e decodificadas. Por isto, esta forma de execução das instruções recebe o nome de ciclo de busca-decodificação-execução, pois para cada instrução armazenada este mesmo processo deve ser realizado. Dependendo do tipo de programa, este ciclo pode ser otimizado por meio da implementação de um *pipeline*, mas para isso faz-se necessário que o programa não possua muitas instruções de desvio.

Hoje em dia, os sistemas embarcados que são desenvolvidos não são tão diferentes dos que eram desenvolvidos na década de 80. Nesta época, os sistemas embarcados eram comumente tidos como um conjunto de periféricos, os quais juntos eram possíveis de serem programados para execução de uma tarefa. Basicamente, estes sistemas eram compostos por um micro-controlador, uma memória e portas de entrada e saída analógica e digital. Por se tratarem de um sistema imutável em termos de *hardware*, o desempenho que era alcançado por estes era dependente do compilador que convertia o código, normalmente escrito em *assembly* para a linguagem de máquina que seria interpretada pela ULA. Não obstante, o algoritmo utilizado para implementar o programa era outro fator que influenciava sobre o desempenho que o sistema teria na execução de suas tarefas, posto que quanto menos eficiente o algoritmo fosse em termos de linhas de código maior seria a quantidade de instruções de máquinas executadas pela ULA.

Esta realidade na qual se encontravam os projetistas de sistemas proporcionou o surgimento das duas maiores vertentes de arquitetura de processadores que imperaram durante o final do século passado. A sessão 2.1.1 descreve as características e razões para o surgimento de tais arquiteturas.

#### 2.1.1. Arquitetura RISC x Arquitetura CISC

Atualmente, o potencial de desempenho e a capacidade de armazenamento dos sistemas embarcados são bastante superiores quando comparados aos sistemas que eram desenvolvidos na década de 70. No início desta mesma década, vários fatores conspiravam para a criação de um sistema que atendesse as limitações que eram impostas. Estes fatores eram principalmente o custo com armazenamento de código e o valor da hora de trabalho para os desenvolvedores de software. Antes do advento das memórias RAMs (Random Access Memory), as memórias magnéticas existentes estavam a quem em termos de velocidade de acesso em comparação aos processadores. A memória era um ponto de extrema relevância, pois não só impactava diretamente sobre a velocidade do sistema, como também, o uso indiscriminado da mesma tornava o sistema mais caro. Isto nos leva

a conclusão que, para se ter um sistema a um custo reduzido, faz-se necessário um programa com código "enxuto".

Aliado a estas questões, o custo com desenvolvimento de *software* tornava-se cada vez mais elevado, pois para se ter um programa compacto e eficiente era necessário que este fosse desenvolvido em linguagem de montagem (*assembly*). Esta linguagem era (e continua sendo) pouco amigável e inteligível para os desenvolvedores de códigos para sistemas embarcados e poucos eram os que verdadeiramente dominavam este estilo de programação. Desta forma, por se tratar de uma tarefa dispendiosa e que exigia a contratação de profissionais especializados, os bons códigos de programas para sistemas embarcados tornaram-se caros. A fim de contornar estes custos e desenvolver um sistema que tivesse um preço cada vez mais competitivo, e baseado na premissa estabelecida por Gordon E. Moore<sup>2</sup> em 1965, os projetistas pensaram numa forma de transferir a complexidade da programação para o *hardware*, haja vista, que este se tornava cada vez mais barato.

A filosofia de projetos CISC (*Complex Instruction Set Computer* – Computador com Conjunto Complexo de Instruções) tem como premissa a resolução destes problemas, ou seja, fornecer uma plataforma capaz de oferecer uma linguagem *assembly* que fosse mais amigável aos programadores. Isto implica principalmente em transferir a complexidade de uma série de funções para o *hardware*. Dentre as principais razões e ganhos que fomentaram o desenvolvimento de sistemas baseado em CISC destacam-se [Ditzel & Patterson, 1998], [Stallings, 2002]:

- Redução na complexidade de desenvolvimento de compiladores para linguagens de máquina;

- Redução no custo com desenvolvimento softwares;

- Redução do tamanho do código dos programas;

<sup>&</sup>lt;sup>2</sup> A Lei de Moore serviu durante muito tempo como meta para os fabricantes de circuitos integrados (CIs) atenderem ao que fora estabelecido, fazendo com que estes investissem em pesquisas promovendo um grande avanço tecnológico na área de semicondutores no final do século XX.

- Redução da complexidade para desenvolvimento de softwares;

- Aumento da quantidade de instruções capazes de realizar operações mais complexas.

No início da década de 80, os projetistas de sistemas embarcados estavam divididos em dois grupos: os que defendiam a arquitetura RISC (Reduced Instruction Set Computer – Computador com Conjunto Reduzido de Instruções) e os que defendiam a arquitetura CISC. A arquitetura RISC teve seu primeiro processador desenvolvido pela IBM em 1975 e contradizia a forma de desenvolvimento de processadores daquele período. As arquiteturas CISC, por transferirem grande parte da complexidade do sistema para o hardware, acabavam por produzir um sistema demasiadamente grande, em termos de utilização de transistores, para os padrões da época. Esta grande necessidade de transistores fazia com que alguns dos processadores CISC não estivessem inseridos em um único CI (Circuito Integrado), aumentando a possibilidade de problemas no sistema. A despeito do que era tido como melhor prática para desenvolvimento das plataformas embarcadas, vários estudos estavam sendo feitos com o intuito de encontrar uma metodologia ótima para o desenvolvimento destes sistemas. Pesquisas apontavam que 25% das instruções contidas em uma plataforma CISC eram utilizadas em aproximadamente 95% do tempo de execução do processador. Além disso, uma quantidade de 30 instruções eram responsáveis por cerca de 99% das instruções que eram executadas pelo processador [Jamil, 1995].

Em 1980, Patterson e Ditzel propuseram a criação de um processador RISC com base nos estudos feitos sobre a utilização das instruções por parte dos processadores. Eles chegaram à conclusão que o desenvolvimento de uma arquitetura baseada nas instruções que eram mais utilizadas pelos processadores maximizaria a eficiência destes. As idéias que davam suporte ao desenvolvimento das arquiteturas RISC eram as seguintes [Patterson & Ditzel, 1980], [El-Aawar, 2006]:

• Pequeno conjunto de instruções;

- Instruções de tamanho único;

- Pequena quantidade de modos de endereçamento;

- A maior parte das instruções é executada em um único ciclo de relógio<sup>3</sup>;

- Compilador otimizado e confiável.

Os temas que abordam estas duas filosofias de projetos envolvem diversos tipos de pesquisas, tais como aplicações de baixo consumo, metodologias para desenvolvimento de arquiteturas superescalares, aplicações de tempo real processamento digital de imagens, projeto de sistemas assíncronos entre outras [Charlot et. al. 1995], [Chang et. al. 1999], [Hu et. al. 2006] e [Lee et. al. 2002]. Todos estes trabalhos possuem um ponto em comum, apesar estarem dirigidos a áreas de estudos distintas. O crescimento tecnológico e científico, no que diz respeito às formas de construção e qualidade dos produtos que são fabricados atualmente, nos permitiu quebrar paradigmas e mudar a forma de pensamento para concepção dos sistemas embarcados. A alta densidade dos circuitos de hoje e a reconfiguração dinâmica são duas características que, entre as décadas de 70 e 80, limitavam bastante o escopo dos projetos e suas funcionalidades. A sessão 2.1.2 abordará aspectos sobre a atual situação e tecnologia disponíveis para a concepção de sistemas embarcados

#### 2.1.2. FPGAs e Dispositivos Reconfiguráveis

Muito embora as arquiteturas e filosofia de desenvolvimento de sistemas embarcados sejam objetos de estudo de grande importância, a forma com que projetos de sistemas embarcados eram desenvolvidos pressupunha uma grande limitação e dependência do sistema pré-fabricado. Neste caso, a arquitetura do *core* do processador escolhido, muitas vezes, não era especificamente projetada para a aplicação ao qual era proposto, fossem estes processadores RISC ou CISC. Isto

•

<sup>&</sup>lt;sup>3</sup> Neste caso, relógio deve ser entendido como o dispositivo responsável pela imposição do ritmo de processamento do sistema e sincronização das operações/tarefas

significava que o projetista estava limitado a um conjunto genérico de instruções de máquina que o processador era capaz de realizar e a uma limitação física de recursos de *hardware*, tais como memória, tamanho das palavras a serem processadas e quantidade de portas de entrada e saída [Stallings, 2002]. Os dispositivos reconfiguráveis estão inseridos dentro uma classe de sistemas digitais que, especialmente no Brasil, obteve grandes incentivos financeiros por parte do governo federal e empresas da área privada nos últimos anos. Um dos exemplos que deste investimento é o Programa Brasil-IP (Intelectual Property) que tem por objetivo formar um corpo expressivo e qualificado de profissionais de sistemas embarcados (sistemas digitais, analógicos e rádio frequência). Apesar de o país estar investindo a pouco tempo neste tipo de tecnologia, o primeiro dispositivo reconfigurável (*Programmable Read-Only Memory* - PROM) apresentado pela comunidade científica já remonta quase 4 décadas . Como forma de contextualizar o leitor sobre a plataforma de implementação a qual esta proposta se destina, façamos uma breve revisão histórica a cerca dos *Dispositivos Reconfiguráveis*.

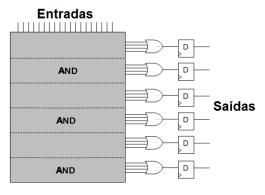

Os Dispositivos Lógicos Programáveis (*Programmable Logic Device* - PLD) surgiram no início da década de 70 e tinham o propósito de fornecer certa flexibilidade de configuração em nível de *hardware*. A *Field-Programmable Logic Array* (FPLA ou apenas PLA, ou ainda PAL) também foi desenvolvido no início da década de 70 e era constituído por um plano fixo de portas ANDs seguido uma coluna de portas ORs de diversos tamanhos. Estes primeiros dispositivos tinham o inconveniente de permitir apenas a aplicação de lógicas combinacionais, mas logo adveio a idéia de interligar-lhes às suas saídas uma bateria de flip-flops [Brown & Rose, 1996]. A Figura 2.2 ilustra um exemplo de da arquitetura da PAL.

Figura 2.2: Arquitetura de uma PAL [Brown & Rose, 1996]

Claramente, as funções que eram possíveis de serem implementadas no PAL eram somas de produtos. A empresa responsável pela criação dos primeiros PALs foi a *Monolithic Memories* e, já no início dos anos 80, foram acrescentados novos blocos de circuitos lógicos aos PALs, o que lhes concebera maior poder de processamento. Estes novos blocos foram chamados de Macrocélulas e eram dotados de *flip-flops*, multiplexadores e portas lógicas.

Os CPLDs (Complex PLD) surgiram posteriormente aos PALs e destacam-se como sendo o dispositivo que promoveu a agregação de vários PLDs em um único *chip*. Esta agregação era promovida por meio de uma rede de interligações físicas e um mecanismo de roteamento entre os diversos blocos de PLDs. Além disso, a qualidade dos dispositivos semicondutores que eram utilizados na fabricação dos CPLDs era superior à dos antigos PALs. Outra importante característica que foi adicionada aos CLPDs foi o padrão de testes e varredura de circuitos, o *Joint Test Action Group* (JTAG), a fim de descobrir pontos de falhas. O processo natural de evolução tecnológica fez com que os sistemas embarcados se tornassem cada vez mais compactos, complexos e densos (maior número de transistores por unidade de área ocupada). A tecnologia atual permite que sistemas sejam produzidos em uma densidade de área de um transistor para cada 10<sup>-9</sup>m². Esta tecnologia é chamada de nano-tecnologia e está sendo fortemente estudada para o desenvolvimento de soluções que podem ser aplicadas nas mais diversas áreas tais como: industrial têxtil, engenharia militar e principalmente na área bio-médica, a bio-tecnologia.

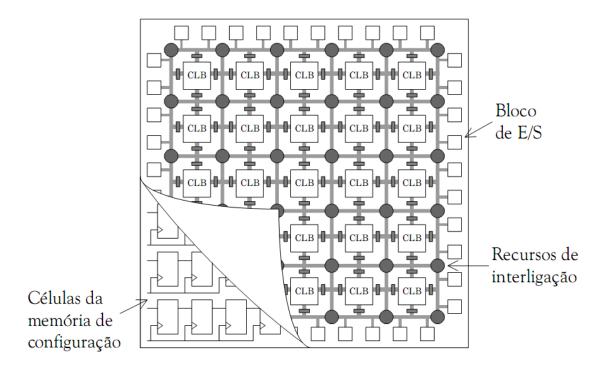

A forma conceitual que caracteriza a arquitetura estrutural de uma *Field-Programmable Gate Arrays* (FPGA) está centrada na alta densidade circuitos, milhares de pinos de entrada e saída (o que lhes confere uma grande vantagem para criação de barramentos de diversos tamanhos) e sua capacidade de reconfiguração. Apesar de serem dispositivos semelhantes aos CPLDs, existem algumas diferenças que distinguem as FPGAs destes últimos. A título de exemplificação, podemos citar como diferença entre os dois dispositivos a quantidade de transistores existente nas FPGAs, que é maior, o processo de fabricação e a tecnologia que empregada. Neste sentido, ela pode ser entendida como uma imensa matriz de blocos lógicos configuráveis (*Configurable Logic Block* - CLB) interconectados ente si por diversas

malhas de conexão e dispositivos de entrada e saída que possibilitam a transferência de dados entre estes blocos. Além disso, o controle da configuração destes CLBs é realizado através de um conjunto de células de memória que estão localizados abaixo da estrutura dos CLBs. A Figura 2.3 ilustra um exemplo desta configuração.

Figura 2.3: Arquitetura de uma FPGA [Gericota, 2003]

Diferentemente dos blocos que são interconectados pelo CPLD, o CLB não se baseia na utilização de soma de produtos, mas na utilização de *Lookup-Table* (LUT), ou seja, implementação de lógicas baseada em memória. As FPGAs constituem o principal grupo de dispositivos reconfiguráveis e nos últimos tempos adquiriu uma característica que proporcionou aos projetistas uma nova forma de pensar e desenvolver sistemas embarcados que é a reconfiguração dinâmica. Esta característica de algumas FPGAs permite ao *hardware* a capacidade de ser remodelado em tempo de execução. Diante disto, o desenvolvimento de sistemas com características de reconfiguração dinâmica possibilita a agregação de funcionalidades que podem tornar o sistema mais seguro através da implementação de técnicas de tolerância à falhas [Matos & White, 1998] e [Yu & Koren, 1994]. A despeito desta característica, as FPGAs são excelentes para prototipação de

projetos de sistemas embarcados devido à sua facilidade de reprogramação e redução de custos com erros de projeto não percebidos na fase de concepção, haja vista a característica de reconfiguração que lhe é assegurada. Entretanto, os resultados de desempenho, ocupação de área ou potência consumida obtidos em uma FPGA não devem ser comparados ao de um Circuito Integrado de Aplicação Específica (*Application-Specific Integrated Circuit* - ASIC), pois a maioria dos circuitos que são desenvolvidos em uma FPGA não está organizado em um arranjo ótimo para tal.

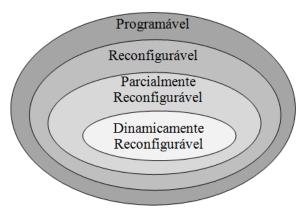

As FPGAs podem ser classificadas segundo o tipo de reconfiguração que lhe é assegurada dentro de 4 grupos segundo Ribeiro [Ribeiro, 2002]. As FPGAs baseadas na tecnologia antifuse são somente programáveis, ou seja, não são passíveis de reconfiguração. As EEPROMs (Electrically-Erasable Programmable Read-Only Memory) estão classificadas dentro do grupo reconfiguráveis, no entanto, o ato da reconfiguração implica na alteração de todas as células que compõem o dispositivo neste processo. No terceiro grupo estão inseridas as FPGAs parcialmente reconfiguráveis as quais são capazes de reter uma parte inativa de sua configuração enquanto outra sofre a reconfiguração. Isto resulta no ganho de tempo, haja vista que somente o circuito de interesse sofre a reconfiguração. O último grupo é designado de dinamicamente reconfigurável. Este grupo distingue-se do anterior pelo fato de permitir a reconfiguração seletiva de parte de seus circuitos em tempo de execução, ou seja, a reconfiguração ocorre com a FPGA em seu modo ativo. A Figura 2.4 ilustra a organização destes grupos, para outras informações [Skliarova & Ferrari, 2003].

Figura 2.4: Classificação das FPGAs segundo a reconfigurabilidade [Ribeiro, 2002]

#### 2.2. Tolerância a Falhas e Sistemas Redundantes

A revolução digital ocorrida no final do século passado promoveu o surgimento de sistemas que vieram a automatizar diversos processos, tais como: transações bancárias, controle de tráfego (aéreo, terrestre ou marítimo), plataformas ou refinarias petroquímicas e ambientes hospitalares. Na maioria dos casos, estes processos envolvem um fator de criticidade o qual necessita de especial atenção a fim de evitar a ocorrência de danos à saúde (física ou mental) dos envolvidos no processo, ao meio ambiente ou aos recursos financeiros. As tecnologias e pesquisas envolvendo soluções para ambientes hospitalares têm sido fortemente fomentadas no meio acadêmico [Soares, 2008], [Iantovics, 2007], [Zhang et. al. 2006] e [Bartocci et. al. 2007]. Este conjunto de fatores acaba por demandar do sistema um alto grau de confiança e disponibilidade, os quais podem ser alcançados através do emprego de técnicas de tolerância a falhas e, em alguns casos, *Redundância em Hardware*.

#### 2.2.1. Tolerância a Falhas

O conceito de tolerância a falha foi primeiramente cunhado em 1967, por Avizienis, o qual fora motivado pelo projeto da *National Aeronautics and Space Administration* (NASA) que pretendia construir uma nave espacial não tripulada para enviar ao espaço [Avizienis, 1997]. O principal desafio deste projeto consistia no desenvolvimento de um sistema que fosse confiável e capaz de atuar de forma automática por um período de dez anos. Desde então, as tecnologias e os métodos para desenvolvimento de sistemas embarcados evoluíram bastante. A quantidade de transistores que podem ser implantados dentro de um chip (*System-on-Chip* - SoC), atualmente, é da ordem de dezenas de milhões. Isto acaba por permitir a construção de um sistema com um maior poder computacional, pois mais funcionalidades podem ser agregadas ao SoC.

As falhas são acontecimentos aos quais os sistemas estão sujeitos e são impossíveis de serem evitadas, toda via, os efeitos que elas podem causar sobre o sistema computacional podem ser tratados de forma a gerarem danos mínimos ou nenhum. Para tanto, existem diversas técnicas de tolerância à falhas já conhecidas no meio acadêmico que podem ser utilizadas em sistemas permitindo que estes

possam atuar de forma limitada, em alguns casos, ou até mesmo sendo intertravados para evitar a ocorrência de um dano maior. Na industrial de mineração, petroquímica ou siderúrgica, por exemplo, existem diversos processos que podem ser considerados extremamente críticos e que envolvem vidas humanas. A ocorrência de falha em um processo crítico destas indústrias pode causar a perde de vidas humanas, ou danos irreparáveis a algum equipamento, se não forem corretamente tratadas. Dependendo do tipo de falha, a parada do processo, mesmo que signifique a diminuição da produção, pode ser a melhor opção, caso seja constatado a ocorrência de uma falha que avarie o sistema e comprometa a segurança do processo. Assim como existem processos automatizados na indústria, de uma forma geral, a área biomédica também é dotada de alguns equipamentos especializados para monitoração de pacientes [Kida et. al. 2008], [Hong et. al. 2008] e [Winey & Yan, 2006]. Para um melhor entendimento dos conceitos de tolerância a falha passemos a definição de alguns conceitos clássicos.

#### 2.2.2. Dependabilidade

A dependabilidade é uma propriedade do sistema que engloba um conjunto de propriedades que servem para definir a qualidade do serviço que é oferecida pelo sistema [Lapri, 1985]. Dentre estas propriedades Pradhan, em [Pradhan, 1996], destacam-se as seguintes: confiabilidade (*reliability*), disponibilidade (*desponibility*), testabilidade (*testability*), mantenabilidade (*mantenability*), segurança de funcionamento (*safety*), segurança da informação (*security*) e desempenho (*performability*). A seguir são apresentados os conceitos de cada uma destas propriedades.

- Confiabilidade: É a capacidade que o sistema tem de executar suas tarefas atendendo as especificações predefinidas do sistema, por um determinado período de tempo, sendo necessário estar operável no início da execução processo.

- Disponibilidade: É dada pela probabilidade que o sistema tem de estar disponível para execução de uma dada tarefa quando solicitado.

- Testabilidade: É dada pela possibilidade da realização de teste sobre o sistema a fim de verificar a consistência do mesmo. Esta propriedade será melhor tanto quanto for mais fácil a realização dos testes.

- Mantenabilidade: Esta propriedade esta relacionada com a capacidade de recuperação do sistema após a entrada deste em um estado de erro. Esta propriedade será melhor tanto quanto menor for o tempo para reparo e recuperação do sistema após sua parada. A mantenabilidade do sistema também está relacionada à probabilidade do sistema ser reparado dentro de um determinado período de tempo pré-estipulado.

- Segurança de funcionamento: Esta propriedade esta relacionada à probabilidade que o sistema tem de executar suas tarefas, ou dirigir o sistema para um estado de segurança, quando uma falha que comprometa a segurança for constatada. Neste sentido, ou o sistema executa suas tarefas sem causar danos aos usuários e outros sistemas ao qual ele esteja ligado, ou interrompe suas operações.

- Segurança da informação: Esta propriedade relacionada à confidencialidade, integridade, autenticidade e proteção contra invasões no sistema que vem a comprometer os dados armazenados.

- Desempenho: Esta propriedade está relacionada à capacidade de o sistema continuar operando, mesmo que de forma degradada, quando uma falha ocorre.

Diante das propriedades inerentes às características da dependabilidade, podemos observar que a tolerância a falha mostra-se como uma solução para a resolução de alguns desafios que a norteiam. As subsessões seguintes apresentaram outros conceitos relacionados à tolerância a falhas, bem como, técnicas utilizadas para sua implementação.

### 2.2.3. Conceitos Clássicos: Falha, Erro e Defeito

O correto funcionamento de um sistema está relacionado ao atendimento de suas especificações (limites máximos e mínimos, tempo, quantidade de dados processados, etc.). O não atendimento a estas especificações podem decorrer de uma má especificação ou de uma falha. O conceito relacionado à definição do que vem a ser falha, erro e defeito é de fundamental importância para a compreensão dos assuntos abordados nesta proposta de qualificação. As definições aqui apresentadas seguem o pensamento adotado por Weber [Weber et. al. 1990], Laprie [Lapri, 1985] e Anderson [Anderson & Lee, 1981]. A falha é definida como o evento que faz o sistema desviar-se de seu curso normal de execução e está necessariamente associada ao universo físico. Este acontecimento pode ser originário de um fator lógico ou físico. Uma falha decorrente de um fator lógico, em alguns casos, está relacionada a uma parte do código que não foi corretamente elaborada ou a um valor de entrada imprevisto, como no caso de entrada de um valor do tipo *real* quando é esperado um valor do tipo *inteiro*. As falhas decorrentes de fatores físicos normalmente estão relacionadas a desgastes do equipamento ou problemas de interconexão entre estes. Embora a falha seja o acontecimento que faz com que o sistema desvie-se de sua especificação, a ocorrência de uma falha, em alguns casos, não significa que o sistema irá atuar de forma incorreta. Por exemplo, se algum dispositivo de sistema deixa de funcionar, mas ele não é utilizado, a percepção desta falha pode nunca acontecer.

O *erro*, em um sistema, nada mais é que a manifestação da falha, ou seja, quando uma falha faz com que o sistema atue de forma não conforme com sua especificação, diz-se que o sistema está em um estado de erro [Avizienis et. al. 2004]. Por exemplo, uma falha em um sensor de temperatura de uma caldeira poderia induzir o sistema a um estado errôneo quanto ao verdadeiro valor de temperatura. Sendo assim, a falha no sensor de temperatura provocou um erro de medição de temperatura.

O defeito pode ser entendido como a manifestação do *erro*, assim como o *erro* pode ser entendido como a manifestação da *falha*. Quando um sistema ou equipamento está com defeito, ou em um estado defeituoso, as especificações para

o qual este fora projetado não serão atendidas. Por exemplo, dado uma rede de sensores/atuadores inteligentes que se comunicam e efetuam a monitoração e aplicação de medicamentos em um leito hospitalar [Valentim et. al. 2008]. A perda da comunicação devido a falha na estrutura da rede pode fazer com que o sistema não receba informações sobre algum dado clínico do paciente, o que indica um *defeito* no sistema de comunicação ou no equipamento que deveria fazer a medição.

### 2.2.4. Falha e Sistemas Computacionais

Um sistema é dito ser tolerante a falha quando possui a capacidade de executar corretamente suas tarefas independentemente da ocorrência de falhas [Johnson, 1984]. Mesmo um sistema que tenha sido aparentemente desenvolvido corretamente está sujeito a falhas decorrentes do desgaste dos dispositivos ou erros de projetos que impliquem em uma lógica falha. Existem dois tipos de falhas que podem acontecer em um sistema: as falhas naturais causadas por um desgaste, de origem interna ou externa, de um componente; e as falhas decorrentes de uma ação humana acidental ou intencional [Avizienis, 1997]. A ocorrência de uma destas falhas não implica que outro tipo de falha não possa vir a acontecer. Como exemplo de uma situação em que estes dois tipos de falhas podem ocorrer é quando um operador configura os parâmetros de uma planta para executar uma tarefa de forma sobrecarregada. Esta operação sistemática fará com que a planta, inevitavelmente, entre em avaria devido ao desgaste de suas peças. Neste exemplo em particular, uma falha decorrente de uma ação humana gerou uma falta natural.

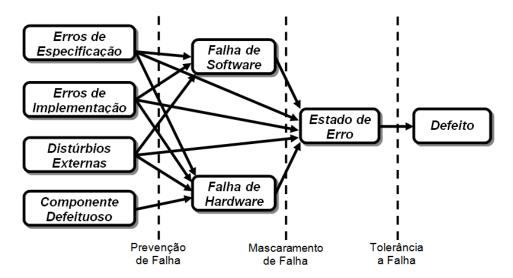

A falha é o fator originário que implica no surgimento de um *erro*. Quando um *erro* acontece, o sistema pode ser conduzido a um estado inconsistente/incoerente que caracteriza a existência de um *defeito*. A falha é o fator que irá fazer com que o sistema não atenda às especificações de seus requisitos. No entanto, os sistemas tolerantes a falhas devem ser capazes de conduzir o sistema a um estado seguro quando uma falta (erro) é detectada, ou permitir que o sistema possa atuar de forma degradada, mas atendendo aos requisitos mínimos do mesmo. Diante deste contexto, existem algumas técnicas que visam dar um tratamento correto à falha, são elas: estruturas redundantes para mascarar componentes que sofreram alguma

falha; códigos de controle de erros e duplicação ou triplicação com mecanismo de votação para descobrir ou corrigir erros de informação; técnicas de diagnóstico para localizar componentes falhos; e técnicas de conversões automáticas para substituir um subsistema que sofreu uma falha [Avizienis et. al. 1987]. Em 1984, Johnson definiu as três principais técnicas para tentar melhorar ou manter a operação normal de um sistema: Prevenção de Falha (*Fault Avoidance*), Mascaramento de Falha (*Fault Masking*) e Tolerância a Falha (*Fault Tolerance*) [Johnson, 1984].

A Prevenção de Falha visa atacar a falha antes mesmo de seu surgimento e pode ser conseguida através de boas práticas de gerenciamento de projetos e testes do sistema para detecção de alguma falha de projeto não percebida em sua fase de detalhamento. Isto tem por objetivo evitar que o sistema seja lançado para o mercado com algum "bug". Neste sentido, testes exaustivos da aplicação podem ajudar a descobrir estes "bugs", entretanto, o tempo gasto na fase de testes irá aumentar o "time to market" (quantidade de tempo desde a concepção até o lançamento do produto no mercado).

O Mascaramento de Falha é aplicado em sistema de tempo real e tem por objetivo evitar que a falha seja propagada para outros componentes do sistema provocando a ocorrência de um erro, ou levando o sistema para um estado de erro. Uma das formas de se implementar esta técnica é por meio da implementação de votadores.

A Tolerância a Falha, ao contrário das demais, não tem por objetivo eliminar o surgimento da falha ou a sua propagação, mas sim conduzir o sistema para um estado que seja aceitável, em termos de execução, e seguro. Existem quatro princípios sobre os quais está fundamentado a utilização da Tolerância a Falha. São eles: a detecção, a localização, o confinamento e recuperação. A Figura 2.5 mostra um fluxograma onde as técnicas descritas por Johnson podem ser utilizadas para aumentar a garantia de funcionamento adequado do sistema e onde cada uma é empregada [Johnson, 1984]:

Figura 2.5: Fluxograma de Causa-Efeito de Falhas [Johnson, 1984]

#### 2.2.5. Sistemas Redundantes

As técnicas de redundância em *hardware* estão, necessariamente, associadas ao aumento de custos financeiros decorrentes da maior quantidade de *hardware* que será empregada no sistema. Entretanto, as técnicas de redundância podem ocorrer em diversos níveis e/ou escopos do projeto [Johnson, 1984], dependendo do tipo do negócio e necessidade do cliente. Vejamos a seguir alguns tipos de redundância que comumente são implementadas em sistemas.

### 2.2.6. Redundância Temporal

Este tipo de técnica de redundância é implementada em processos onde o poder de processamento do sistema é suficientemente elevado, ao ponto de se poder processar uma mesma informação mais de uma vez, sem que o processo venha a sofrer algum prejuízo. Normalmente é utilizada em aplicações de tempo não crítico. Estas técnicas podem ser empregadas para a detecção de falhas transientes, ou seja, falhas que ocorrem de tempo em tempos, não necessariamente igualmente espaçados. Também é possível aplicá-la a fim de detectar uma falha permanente. Para este tipo de falha a detecção requer a aplicação de funções de codificadores e decodificadores as quais sejam inversíveis [Abd-El-Barr, 2007].

Para os casos de Redundância temporal, qualquer que seja o tipo de falha que se queira detectar, permanente ou transiente, faz-se necessário o uso de um

componente que seja capaz de armazenar o valor do dado em um tempo t e um comparador. Estes dois componentes serão utilizados para que os dados processados em um tempo t+x e os processados em um tempo t possam ser comparados. Desta forma, a não equivalência entre os valores constatará a existência da falha.

#### 2.2.7. Redundância de Software

A aplicação de técnicas de redundância de *software* não acontece simplesmente copiando dois programas idênticos e fazendo com que estes executem em paralelo. A própria literatura comenta sobre a grande dificuldade e a quantidade de erros que são ocasionados pela utilização deste tipo de redundância [Koren & Krishna, 2007]. Existem diversos tipos de técnicas de redundância que podem ser utilizadas com o auxílio de *software*. Por este não ser o objetivo principal desta dissertação, não nos ateremos a este tipo de redundância e maiores detalhes podem ser consultados em [Abd-El-Barr, 2007], [Koren & Krishna, 2007], [Pradhan, 1996] e [Jalote, 1994]. A seguir, daremos uma breve explicação sobre algumas das técnicas de redundância de *software* que podem ser aplicadas em um sistema computacional, as quais podem ser consultadas em [Abd-El-Barr, 2007].

**Programação N-versões:** Neste tipo de abordagem, o mesmo escopo de um sistema é passado para diversos grupos de desenvolvedores de *software*, os quais ficam encarregados de elaborar o programa. Após a finalização do programa, cria-se um mecanismo de votação que irá decidir sobre a saída do sistema com base nos valores que foram gerados por cada um dos programas. Normalmente são desenvolvidas 3 aplicações, as quais executam a mesma tarefa em paralelo. Esta técnica pode ser aplicada em diversas fases do desenvolvimento do *software* (especificação, implementação, teste), entretanto vários problemas estão associados a este tipo, tais como: identificação do erro por meio de correlação, sincronização entre os *software*s e aumento significativo da complexidade e custo do sistema. Não obstante, não existe um método formal para validar a eficácia deste tipo de técnica.

**Blocos de Recuperação:** Está técnica é bastante semelhante à Programação N-versões, mas com uma abordagem diferente. Tal qual para a técnica anterior, esta

também faz uso de várias versões de programas desenvolvidas por grupos distintos, no entanto, ao invés de utilizar um votador para decidir sobre o resultado processado é feito um teste de aceitação sobre cada uma dos programas. Os programas estão organizados de forma cascateada e para cada saída que não passar no teste de aceitação é verificada a saída do programa seguinte.

**Precondições, Pós-condições e Asserções:** Trata-se de testes de aceitação que são realizados sobre métodos, funções ou sub-rotinas de *software* a fim de realizar, por exemplo, um tratamento de exceção que ocorre quando se tenta realizar uma divisão por zero. Estes testes, que podem ocorrer antes, durante ou após a invocação de um método e tem por objetivo evitar a propagação do erro ou o "travamento" do programa.

As técnicas de tolerância a falhas aplicadas em *software*s não estão limitadas a estas breves descrições. Existem outras abordagens que exploram pontos de falhas diferentes dos aqui mencionados, não só para detecção como também para correção.

### 2.2.8. Redundância da Informação

Existem sistemas onde o mais importante é que a informação associada ao processo não seja perdida e, para tal situação, o emprego de redundância de dados armazenados (*backup*) em discos rígidos diferentes pode ser visto como uma boa solução para o problema. Toda via, torna-se mais proveitoso e seguro ter estes dois, ou mais, discos localizados em ambientes diferentes. Isto visa resguardar um destes discos rígidos no caso da ocorrência de um incêndio no prédio em que estes se encontrem, por exemplo, causando a destruição de ambos os dispositivos de armazenamento. Isto irá diminuir as chances de perda da informação, além de evitar a ocorrência de um evento que danifique os dois, ou mais, discos rígidos.

Neste caso, os custos envolvidos não estão relacionados somente à duplicação dos dados, mas também ao aluguel/compra/construção de outro local para armazenamento deste disco. Para tal situação, existem empresas especializadas que tratam do armazenamento e proteção (segurança) destas informações, o que evidencia mais um custo para o sistema. Não obstante, há

também a perda de tempo inerente à realização da duplicação da base de dados e, em algumas circunstâncias, o transporte, que também consome recursos. Esta é uma técnica que é utilizada com fins a prevenir a integridade dos dados, ou seja, trata-se de um mascaramento para o caso de ocorrência de alguma falha em um ou outro disco. No entanto, diferentemente das aplicações de armazenamento, existem outras formas de se aplicar a redundância da informação como meio para detecção de falhas. Nestes casos, costuma-se transmitir informações reduntantes em uma mesma mensagem para que o receptor possa comparar os campos e validar a qualidade da informação recebida. Exemplos clássicos de onde estas técnicas são implementadas podem ser encontrados nos campos de verificação da mensagem, utilizados em alguns protocolos, tais como bits de paridade e *checksum*. Estes campos de detecção de erros são muito importantes para verificação da mensagem que é recebida, no entanto, além destes ou, ao invés destes, existem também alguns campos que são utilizados para detecção e correção de erros, a saber, *Error Detection Code* (EDC) que além de detectar o erro realiza a correção deste.

#### 2.2.9. Redundância de *Hardware*

Dentre todas as técnicas de redundância utilizadas para sistemas tolerantes a falhas, as técnicas de redundância em *hardware* são as mais pesquisadas no meio científico [Koren & Krishna, 2007]. O emprego deste método, entretanto, deve ser aplicado de acordo com o bom senso do projetista e a viabilidade financeira para qual o sistema é destinado. Neste cenário, existem três tipos de técnicas de redundância de *hardware* que são conceitualmente empregadas: redundância estática (ou passiva), redundância dinâmica (ou ativa) e redundância híbrida. A seguir são apresentados os conceitos dos tipos de técnicas de redundância em hardware segundo Koren e Krishna [Koren & Krishna, 2007].

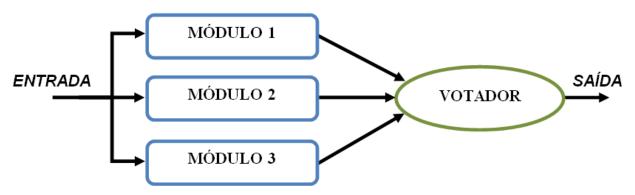

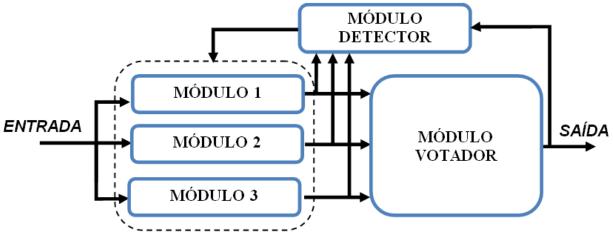

**Redundância Estática:** O princípio básico desta técnica consiste em ocultar (mascarar) a existência da falha em um determinado nível do sistema de tal forma que sua ocorrência não seja identificada por outras partes do mesmo. Exemplos clássicos deste tipo de redundância são os sistemas *N-Modular Redundancy* (NMR) e o *Triple-Modular Redundancy* (TMR), o qual trata-se de uma particularidade do

NMR. Um sistema TMR é caracterizado pela existência de três módulos de processamento de *hardware* idênticos que devem receber e processar a mesma gama de dados em paralelo. A saída destes módulos está ligada a um módulo votador que irá decidir sobre a corretude dos valores recebidos baseado no valor médio ou pela maioria. Além disso, a correta especificação deste sistema irá depender da expectativa de falha dos módulos de processamento. Considerando que, em um determinado sistema, *n* módulos venham a falhar é fácil notar que para este será necessária a utilização de *2n+1* módulos [Abd-El-Barr, 2007]. Esta constatação pode ser feita, pois como o sistema baseia-se em um votador, é necessário que a maioria dos módulos esteja em bom estado para que o resultado da escolha seja correto. A Figura 2.6 demonstra um exemplo em diagrama de fluxo de um sistema TMR.

Figura 2.6: Modelo de Redundância TMR [Abd-El-Barr, 2007]

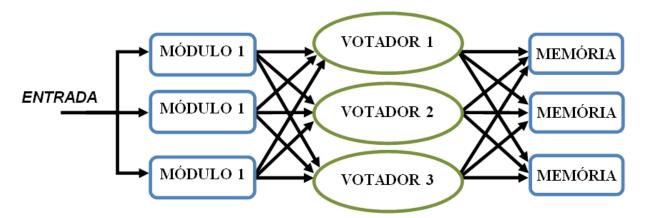

Observando este modelo podemos perceber que o módulo votador consiste no ponto crítico de falha, pois independentemente da quantidade de falhas que venham a acontecer nos módulos de processamento, se o módulo votador não estiver funcionando corretamente o sistema poderá atuar de forma errada. Como forma de minimizar esta deficiência, um esquema de redundância de votadores e armazenamento em memória podem ser utilizados [Koren & Krishna, 2007]. A Figura 2.7 demonstra um exemplo deste modelo que aumenta a confiabilidade do sistema. Vale salientar que este tipo de sistema não é capaz de detectar qual(is) dos módulos do sistema sofreu(ram) uma falha que tenha ocasionado um erro. Para isto, seria necessária a implantação de um detector de falhas para identificar o(s) módulo(s) em

desacordo(s). Pesquisas mostram que aplicações que requeiram a disponibilidade do sistema por um longo período, a utilização de um sistema NMR pode apresentar um desempenho pior que o de um sistema não redundante em termos de confiança.

Figura 2.7: Modelo TMR com Redundância de Votadores [Koren & Krishna, 2007]

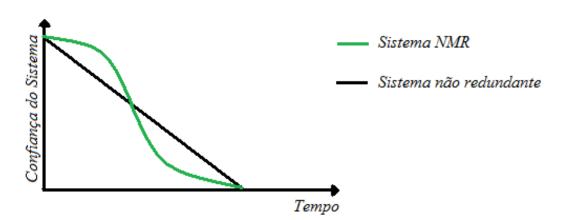

O Gráfico 2.1 demonstra o comportamento destes sistemas ao longo do tempo baseado em seu grau de confiança. Claramente podemos notar que, com o passar do tempo, a confiança de um sistema com redundância múltipla torna-se inferior a de um sistema que não emprega redundância. Parte desse declínio na confiança do sistema deve-se a complexidade envolvida para recuperação, quando da ocorrência de falha, em um sistema distribuído.

Gráfico 2.1: Comparação entre sistemas redundantes e não redundantes [Koren & Krishna, 2007]

**Redundância Dinâmica:** Este tipo de técnica deve ser aplicado em sistemas que não exijam uma resposta imediata da aplicação quando da ocorrência de um

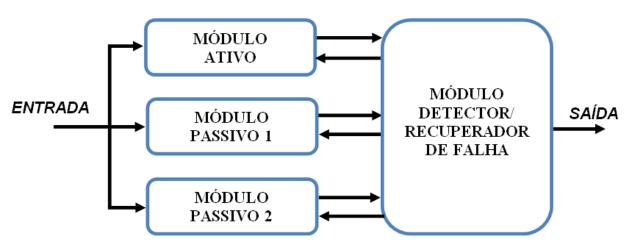

erro, ou seja, é admissível que o sistema permaneça um período de tempo tolerável em um estado de falha. O fundamento na qual se baseia está técnica pressupõe a substituição ou remoção do componente que sofreu a falha (módulo ativo) por uma réplica deste (módulo passivo). Para tanto, é necessário que tais módulos sejam dotados de uma estrutura capaz de perceber a ocorrência da falha e, a partir desta detecção, recuperar o sistema. Esta estrutura é chamada de módulo detector/recuperador de falha e, pode ser visto como um gerenciador que bloqueia a passagem dos valores gerados pelos componentes com erro. Quando um erro é detectado, o módulo ativo em erro é bloqueado e o módulo seguinte passa a ser o responsável pela geração da informação e continuidade de operação do sistema. A Figura 2.8 ilustra um arranjo simples da implementação da técnica de redundância dinâmica.

Figura 2.8: Modelo de Redundância Dinâmica [Abd-El-Barr, 2007]

A forma de operação dos componentes replicados determina o tipo de redundância dinâmica:

Hot Standby: Nesta configuração, ambos os módulos estão operando de forma paralela e, no momento em que ocorre um erro no módulo que está em operação, o módulo seguinte, por estar operando em paralelo, encontra-se apto para enviar o valor processado. • Cold Standby: Neste tipo de configuração, apenas um módulo processa a informação por vez. O módulo passivo é acionado somente quando um erro é detectado no módulo ativo. Este tipo de redundância requer um maior tempo de espera para recuperação do sistema, entretanto, o tempo de vida útil de forma geral é aumentado, posto que o módulo passivo só começa a atuar quando o módulo ativo entra um estado de erro. Isto permite que os módulos sofram um menor desgaste decorrente de sua não utilização.

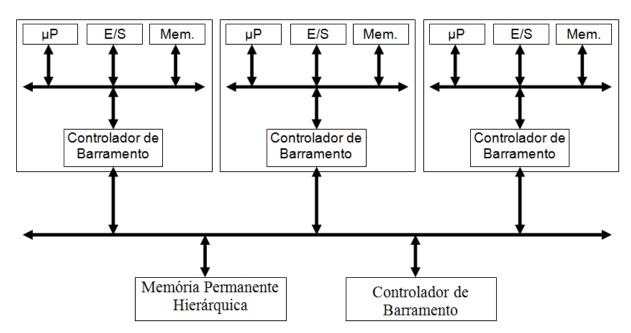

Redundância Híbrida: Esta técnica é caracterizada pela utilização das duas abordagens anteriormente apresentadas, Redundância Estática e Redundância Dinâmica [Koren e Krishna, 2007]. Esta característica híbrida confere ao sistema a possibilidade de, além de continuar seu andamento a despeito da ocorrência de uma falha, identificar qual o módulo de processamento sofreu a falha, removendo ou substituindo-o do processo. Para isso, é necessária a criação de um bloco que será responsável pela detecção do módulo que sofreu a falha, o qual está ligado às saídas dos módulos de processamento e saída do módulo votador. A Figura 2.9 ilustra um exemplo deste tipo de técnica.

Figura 2.9: Modelo de Redundâncai Híbrida [Abd-El-Barr, 2007]

#### 2.3. Sistemas Distribuídos

Os avanços das tecnologias de comunicação trouxeram ganhos expressivos que permitiram o desenvolvimento de grandes redes de computadores, como por

exemplo, a Internet<sup>4</sup>. Neste sentido, a aplicação de ferramentas que tem por objetivo a exploração dos benefícios proporcionados por estas redes acabaram por fomentar o desenvolvimento de sistemas distribuídos. Os sistemas distribuídos podem ser entendidos como um conjunto de módulos autônomos que se comunicam entre si por meio de troca de mensagens [Hariri et. al. 1992]. Entretanto, não é suficiente dizer que somente a troca de mensagem entre estes sistemas concebe a estes o valor agregado ao conceito de sistema distribuído. Faz-se necessário que estes módulos atendam alguns requisitos definidos por Colouris [Colouris et. al. 1994] e que as tarefas executadas estejam envolvidas em um propósito comum, tornando todos estes módulos um sistema singular e coerente para o usuário [Tanenbaum & Steen, 2002]. Estes requisitos são definidos como: compartilhamento de recursos, concorrência de processos, escalabilidade do sistema, tolerância a falhas e transparência em termos de aplicação para o usuário.