# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# GUSTAVO REIS WILKE

# Analysis and Optimization of Mesh-based Clock Distribution Architectures

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microelectronics

Ricardo Augusto da Luz Reis Advisor

Rajeev Murgai Coadvisor

# **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

## CIP - CATALOGING-IN-PUBLICATION

Wilke, Gustavo Reis

Analysis and Optimization of Mesh-based Clock Distribution Architectures / Gustavo Reis Wilke. – Porto Alegre: PGMICRO da UFRGS, 2008.

123 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2008. Advisor: Ricardo Augusto da Luz Reis; Coadvisor: Rajeev Murgai.

1. Clock. 2. Clock mesh. 3. Skew. 4. High performance. 5. Microprocessor. 6. Variability. I. Reis, Ricardo Augusto da Luz. II. Murgai, Rajeev. III. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Pró-Reitor de Coordenação Acadêmica: Prof. Pedro Cezar Dutra Fonseca Pró-Reitora de Pós-Graduação: Prof<sup>a</sup>. Valquíria Linck Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMICRO: Prof. Henri Ivanov Boudinov Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **CONTENTS**

| LIST                                                           | OF ABBREVIATIONS AND ACRONYMS                                                                                             | 7                                      |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| LIST                                                           | OF SYMBOLS                                                                                                                | 8                                      |

| LIST                                                           | OF FIGURES                                                                                                                | 9                                      |

| LIST                                                           | OF TABLES                                                                                                                 | 12                                     |

| ABS                                                            | TRACT                                                                                                                     | 13                                     |

| 1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4<br>1.1.5<br>1.2<br>1.3 | Definitions Clock Timing Clock Skew Clock Jitter Process Variability Environmental Variability Motivation Thesis Proposal | 14<br>15<br>16<br>16<br>17<br>19<br>20 |

| 2 C<br>2.1                                                     | Reliability                                                                                                               |                                        |

| 2.1.1                                                          | Shielding                                                                                                                 |                                        |

| 2.1.2                                                          | Differential Signaling                                                                                                    | 23                                     |

| 2.2                                                            | Low Power                                                                                                                 | 24                                     |

| 2.2.1                                                          | Clock Gating                                                                                                              | 24                                     |

| 2.2.2                                                          | Reduced Swing                                                                                                             | 25                                     |

| 2.3                                                            | Routing Topologies                                                                                                        | 27                                     |

| 2.3.1                                                          | Htree                                                                                                                     | 28                                     |

| 2.3.2                                                          | Xtree                                                                                                                     | 29                                     |

| 2.3.3                                                          | Clock Routing                                                                                                             | 29                                     |

| 2.3.4                                                          | Clock Spine                                                                                                               | 31                                     |

| 2.3.5                                                          | Clock Mesh                                                                                                                | 33                                     |

| <b>2.4</b>                                                     | Architectural Strategies                                                                                                  | 34                                     |

| 2.4.1                                                          | Clock Domains                                                                                                             | 34                                     |

| 2.4.2                                                          | Deskew                                                                                                                    | 35                                     |

| 3 C        | LOCK ARCHITECTURES REVIEW                                                                                   | 38  |

|------------|-------------------------------------------------------------------------------------------------------------|-----|

| 3.1        | Clock Distribution Architectures: A Comparative Study                                                       | 38  |

| 3.1.1      | Target Architectures                                                                                        | 38  |

| 3.1.2      | Target Chip Specification                                                                                   | 39  |

| 3.1.3      | Experimental Set-Up                                                                                         | 40  |

| 3.1.4      | Analysis                                                                                                    | 43  |

| 3.1.5      | Results                                                                                                     | 44  |

| 3.2        | Microprocessor Clock Distribution Bibliographic Study                                                       | 48  |

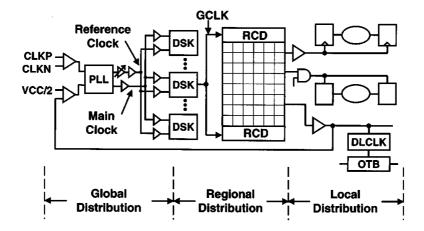

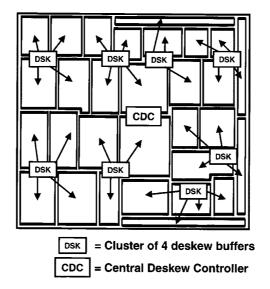

| 3.2.1      | Pentium 4 (2000)                                                                                            |     |

| 3.2.2      | Itanium 1st Generation (2000)                                                                               | 50  |

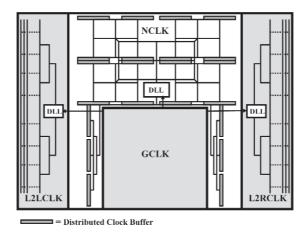

| 3.2.3      | 1.2GHz Alpha Microprocessor (2001)                                                                          | 52  |

| 3.2.4      | Power4 (2002)                                                                                               | 52  |

| 3.2.5      | Itanium 2nd Generation (2002)                                                                               | 54  |

| 3.2.6      | Itanium 3rd Generation (2004)                                                                               | 55  |

| 3.2.7      | Power5 (2004)                                                                                               | 56  |

| 3.2.8      | Dual-Core SPARC V9 (2005)                                                                                   |     |

| 3.2.9      | First Cell Processor (2005)                                                                                 | 57  |

| 3.2.10     |                                                                                                             |     |

| 3.2.11     |                                                                                                             |     |

| 3.3        | A General Microprocessor Clock Distribution Architecture                                                    | 59  |

| 4 C        | LOCK MESH ANALYSIS                                                                                          | 62  |

| 4.1        | Modeling                                                                                                    |     |

| 4.2        | The Sliding Window Scheme                                                                                   |     |

| 4.2.1      | SWS Justification                                                                                           |     |

| 4.2.2      | SWS Accuracy                                                                                                |     |

| 4.2.3      | Improving SWS Accuracy                                                                                      |     |

| 4.2.4      | Experimental Results                                                                                        |     |

| 4.2.5      | Conclusions                                                                                                 |     |

| 4.3        | Related Works                                                                                               |     |

| 4.3.1      | Accelerating Clock Mesh Simulation Using Matrix-Level Macromod-                                             |     |

|            | els and Dynamic Time Step Rounding                                                                          | 73  |

| 4.3.2      | Analysis of Large Clock Meshes Via Harmonic-Weighted Model Order                                            |     |

|            | Reduction and Port Sliding                                                                                  | 75  |

| 4.3.3      | A Frequency-domain Technique for Statistical Timing Analysis of                                             |     |

|            | Clock Meshes                                                                                                | 76  |

| 4.3.4      | Clock Skew Analysis via Vector Fitting in Frequency Domain                                                  |     |

| 4.4        | Conclusions                                                                                                 | 81  |

|            | LOCK MECH ORTHAIZATION CTRATECIES                                                                           | 0.0 |

|            | LOCK MESH OPTIMIZATION STRATEGIES                                                                           | 82  |

| 5.1        | Related Works                                                                                               | 82  |

| 5.1.1      | Combinatorial Algorithms for Fast Clock Mesh Optimization                                                   | 83  |

| 5.1.2      | MeshWorks: An Efficient Framework for Planning, Synthesis and Op-                                           | 0.5 |

| <b>F</b> 0 | timization of Clock Mesh Networks                                                                           |     |

| 5.2        | Motivation                                                                                                  |     |

| 5.2.1      | Power Consumption Due To Inter-Buffer Short Circuit Current Slowy Due To Inter Buffer Short Circuit Current |     |

| 5.2.2      | Skew Due To Inter-Buffer Short Circuit Current                                                              |     |

| 5.3        | Mesh Buffer Sizing                                                                                          | 94  |

| 5.3.1 | Mean Sizing                                 |

|-------|---------------------------------------------|

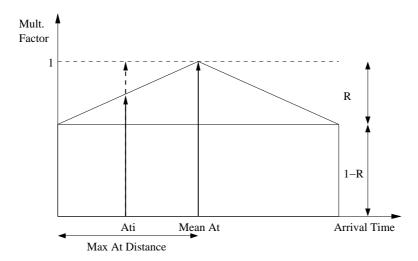

| 5.3.2 | Probabilistic Sizing                        |

| 5.3.3 | Experimental Setup                          |

| 5.3.4 | Experimental Data                           |

| 5.3.5 | Conclusions                                 |

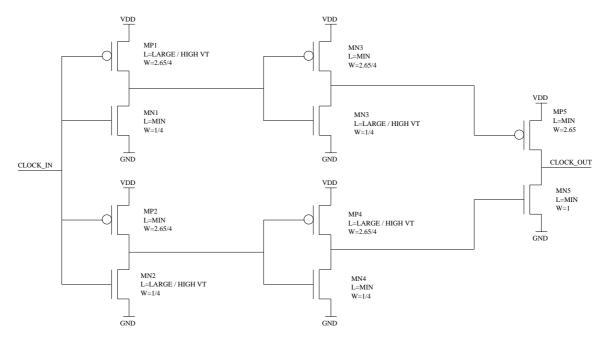

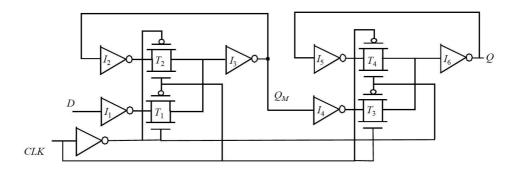

| 5.4   | A New Mesh Buffer Design                    |

| 5.4.1 | Fast Turning Off, Slow Turning On Heuristic |

| 5.4.2 | Electrical Implementation                   |

| 5.4.3 | Applicability and Limitations               |

| 5.4.4 | Experimental Setup                          |

| 5.4.5 | Methodology Verification                    |

| 5.4.6 | Buffer Verification                         |

| 5.4.7 | Leakage Analysis                            |

| 5.4.8 | Conclusions                                 |

| 6 C   | ONCLUSIONS                                  |

| APPE  | ENDIX A SELECTED PUBLICATION LIST           |

| REFE  | <b>RENCES</b>                               |

# LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application Specific Integrated Circuit

CDF Cumulative Distribution Function

PDF Probabilty Density Function

DME Deferred-Merge Embedding

IO Input-Output

LCD Local Clock Driver

PGCN Pre-Global Clock Network

GCG Global Clock Grid

PLL Phase Locked Loop

IA Instruction set Architecture

DLL Delay Locked Loop

SOI Silicon Over Insulator

MMM Method of Mean and Medians

VT Voltage Threshold

FO Fanout Of

PVT Process Voltage and Temperature

DFD Digital Frequency Dividers

SLCB Second Level Clock Buffers

CVD Clock Vernier Device

LCB Local Clock Buffer

UC Units of Capacitance

SWS Sliding Window Scheme

TLM Tree + Local Meshes

MLT Mesh + Local Trees

FF Flip-Flop

SPD Symmetric Positive Definite

MC Monte Carlo

# LIST OF SYMBOLS

- $\sum$  Summation

- $\sigma$  Standard deviation

- $\mu$  Micron/Mean

- m Milli

- n Nano

- p Pico

- f Femto

- $\Omega$  Ohms

# LIST OF FIGURES

| Figure 1.1:             | Clock period definition                                   | 14              |

|-------------------------|-----------------------------------------------------------|-----------------|

| Figure 1.2:             | Clock arrival time histogram                              | 17              |

| Figure 1.3:             |                                                           | 17              |

| Figure 2.1:             | Glitch caused by crosstalk noise                          | 23              |

| Figure 2.1:             | v                                                         | $\frac{23}{23}$ |

| Figure 2.2. Figure 2.3: | v                                                         | $\frac{23}{24}$ |

| Figure 2.3. Figure 2.4: |                                                           | $\frac{24}{25}$ |

| ~                       |                                                           | $\frac{25}{25}$ |

| Figure 2.5: Figure 2.6: |                                                           | $\frac{25}{27}$ |

|                         |                                                           | 21<br>27        |

| Figure 2.7:             | 0 ,                                                       |                 |

| Figure 2.8:             | 1                                                         | 28              |

| _                       | 9 0                                                       | 28              |

|                         | 1 /                                                       | 29              |

|                         | O I                                                       | 30              |

|                         | ,                                                         | 30              |

|                         | 6 6 6                                                     | 31              |

|                         | 0                                                         | 32              |

|                         | - , ,                                                     | 32              |

|                         | <u> </u>                                                  | 33              |

| Figure 2.17:            | Mesh for 600-MHz Alpha Microprocessor (BAILEY; BENSCHNEI- |                 |

|                         | , ,                                                       | 34              |

| _                       |                                                           | 35              |

| _                       |                                                           | 36              |

| _                       | , , ,                                                     | 36              |

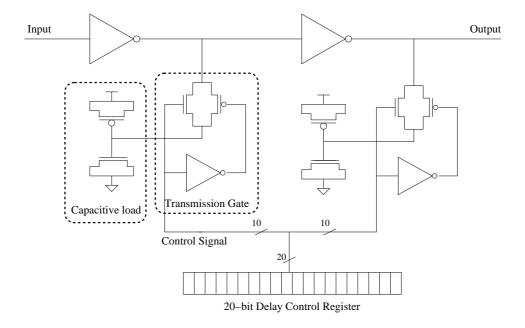

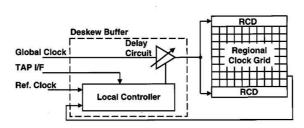

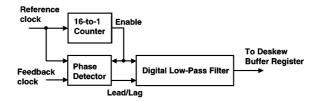

| Figure 2.21:            | Adjustable delay block controller (TAM et al., 2000)      | 37              |

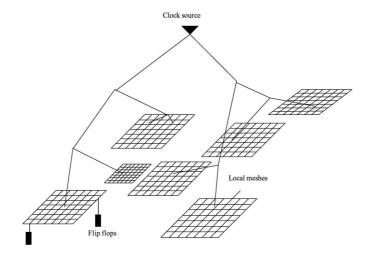

| Figure 3.1:             | MLT architecture example (YEH et al., 2006)               | 39              |

| Figure 3.2:             | - ,                                                       | 40              |

| Figure 3.3:             |                                                           | 41              |

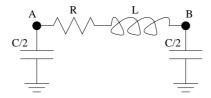

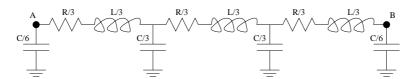

| Figure 3.4:             | $3-\pi$ model for interconnect                            | 41              |

| Figure 3.5:             |                                                           | 49              |

| Figure 3.6:             |                                                           | 49              |

| _                       |                                                           | 49              |

| Figure 3.8:             |                                                           | 50              |

| Figure 3.9:             |                                                           | 50              |

| ~                       |                                                           | 51              |

| _                       |                                                           | $51^{-}$        |

| J                       | , , ,                                                     |                 |

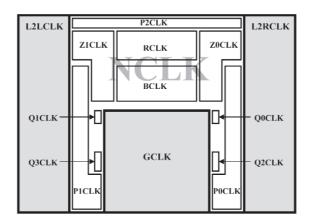

| Figure           | 3.12: | Clock domains for Alpha 1.2GHz microprocessor (XANTHOPOU-LOS et al., 2001)                                                                                                              | 52       |

|------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

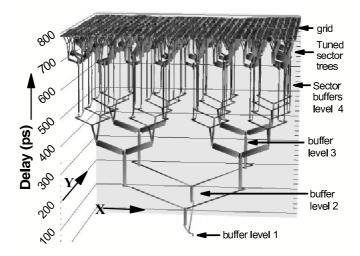

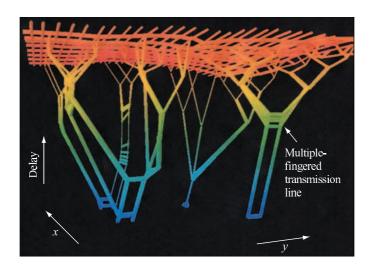

| Figure           | 3.13: | Clock distribution for Alpha 600MHz microprocessor (BAILEY;                                                                                                                             | 53       |

| Figure           | 3.14: | NCLK subdomains for Alpha 1.2GHz microprocessor (XANTHOPOU                                                                                                                              |          |

| Figure           | 3.15: | , ,                                                                                                                                                                                     | 54       |

|                  |       |                                                                                                                                                                                         | 54       |

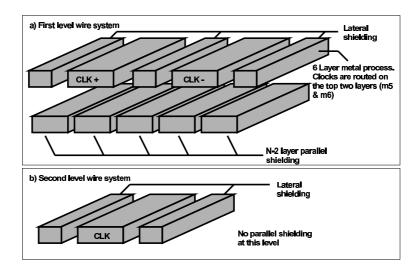

| Figure           | 3.17: | Clock lines shielding for Itanium 2nd generation(ANDERSON; WELLS; BERTA, 2002)                                                                                                          | 55       |

| Figure           | 3.18: | Clock distribution scheme for Itanium 2nd generation (ANDERSON; WELLS; BERTA, 2002)                                                                                                     | 55       |

| Figure           | 3.19: | Clock distribution scheme for 3rd generation Itanium (TAM; LI-MAYE; DESAI, 2004)                                                                                                        | 56       |

| Figure           | 3.20: |                                                                                                                                                                                         | 57       |

| Figure           | 3.21: | Clock distribution for Itanium Montecito microprocessor(MAHONEY et al., 2005)                                                                                                           | 58       |

| Figure           | 3.22: | Power6 clock distribution (FRIEDRICH et al., 2007)                                                                                                                                      | 60       |

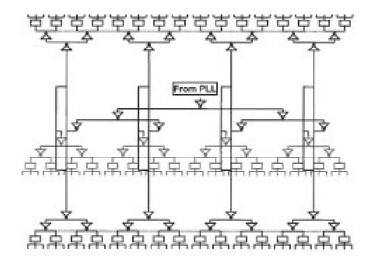

| Figure           | 3.23: | General clock distribution for microprocessors                                                                                                                                          | 61       |

| Figure           | 4.1:  | v i                                                                                                                                                                                     | 63       |

| Figure           |       | , ,                                                                                                                                                                                     | 64       |

| Figure           |       | <b>3 0 0 1</b>                                                                                                                                                                          | 65       |

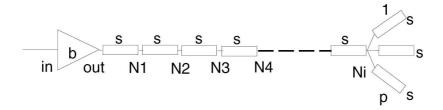

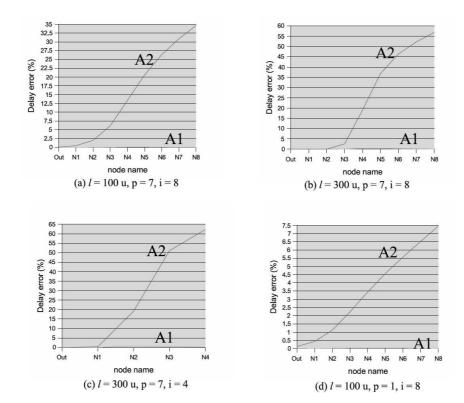

| Figure           | 4.4:  | Experimental data justifying SWS. Approximation $A_1$ mimics SWS; $A_2$ does not include model of the circuit outside the region of interest (CHEN et al., 2005)                        | 65       |

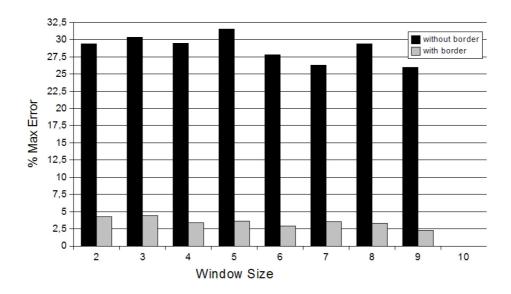

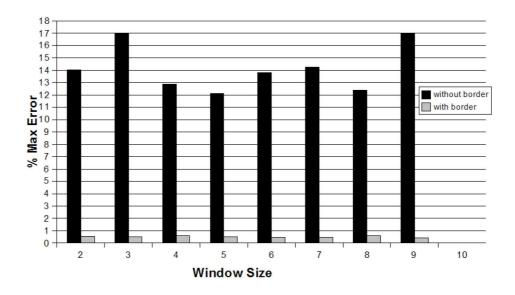

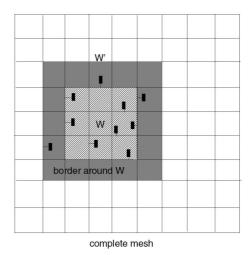

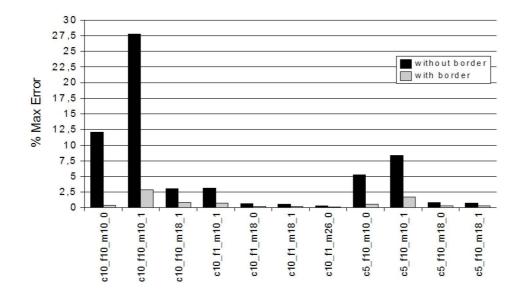

| Figure           | 4.5:  | Maximum error without and with border for $10mm \times 10mm$ chip, $10 \times 10$ mesh, $10 \text{K}$ FFs and a buffer on every other mesh node                                         | 67       |

| Figure           | 4.6:  | Maximum error without and with border for $10mm \times 10mm$ chip, $10 \times 10$ mesh, $10 \text{K}$ FFs and a buffer on every mesh node (CHEN                                         |          |

| Figure           | 17.   | , , ,                                                                                                                                                                                   | 67<br>68 |

| Figure           |       | Accuracy of SWS for different experimental settings (CHEN et al.,                                                                                                                       |          |

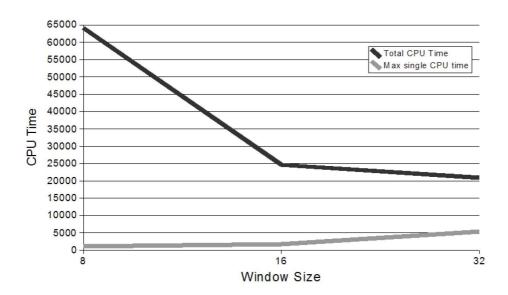

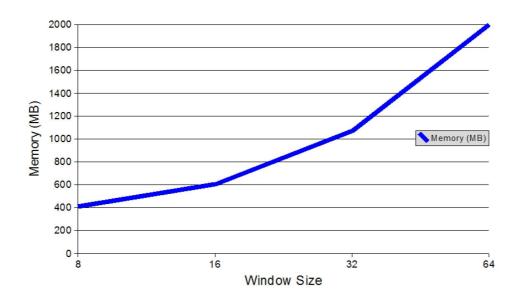

| Figure           | 4.9:  | CPU time as a function of the window size. Total CPU time is relevant for sequential execution. Max single CPU time is the turnaround time, assuming maximum parallel processing. (CHEN | 70       |

|                  |       | , , ,                                                                                                                                                                                   | 71       |

| _                |       | , , ,                                                                                                                                                                                   | 71       |

| _                |       | 1 / /                                                                                                                                                                                   | 74       |

| _                |       | <u> </u>                                                                                                                                                                                | 75<br>   |

| _                |       | , , , , ,                                                                                                                                                                               | 77       |

| _                |       | v , , , ,                                                                                                                                                                               | 79       |

| F'igure          | 4.15: | Ramp signal waveform (ZHANG et al., 2008)                                                                                                                                               | 79       |

| Figure<br>Figure |       | • , , ,                                                                                                                                                                                 | 84       |

| -                |       |                                                                                                                                                                                         | 85       |

| Figure | 5.3:  | Short circuit example                                             | 89  |

|--------|-------|-------------------------------------------------------------------|-----|

| Figure | 5.4:  | Short circuit due to skew                                         | 89  |

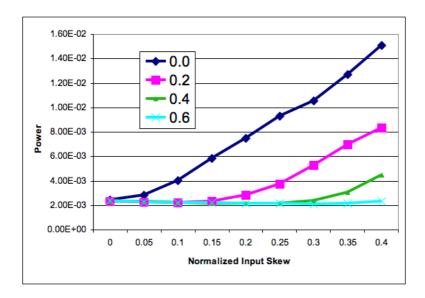

| Figure | 5.5:  | Total Power and Short circuit Power vs. Maximum Input Skew .      | 91  |

| Figure | 5.6:  | Improving slew by buffer sizing                                   | 91  |

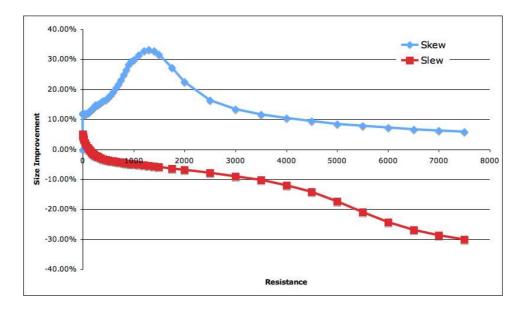

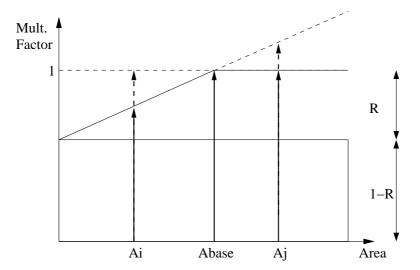

| Figure | 5.7:  | R effect on skew and slew reduction                               | 94  |

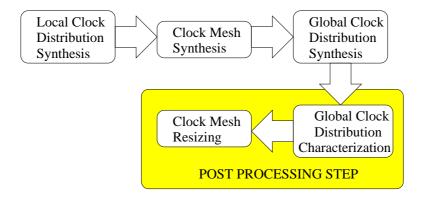

| Figure | 5.8:  | Mesh buffer sizing flow                                           | 94  |

| Figure | 5.9:  | Mean sizing algorithm                                             | 95  |

| Figure | 5.10: | Mean sizing algorithm                                             | 96  |

| Figure | 5.11: | Probabilistic sizing algorithm                                    | 96  |

| Figure | 5.12: | Probabilistic sizing algorithm                                    | 97  |

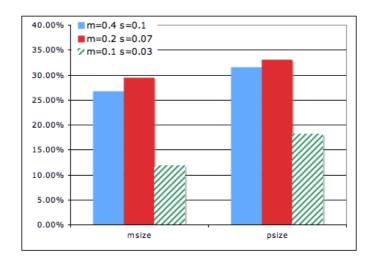

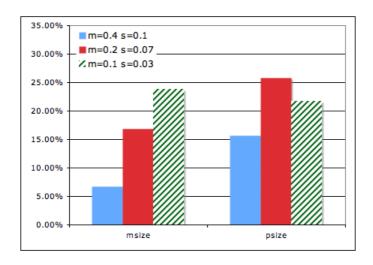

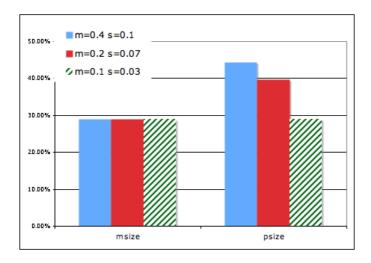

| Figure | 5.13: | Average Skew improvement                                          | 100 |

| Figure | 5.14: | Average Power improvement                                         | 100 |

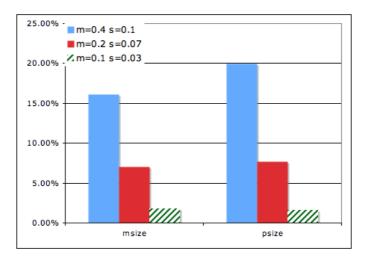

| Figure | 5.15: | Average Slew penalty                                              | 101 |

| Figure | 5.16: | Average Undersize                                                 | 101 |

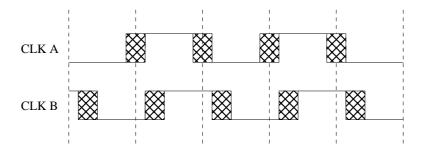

| Figure | 5.17: | High Impedance Time                                               | 103 |

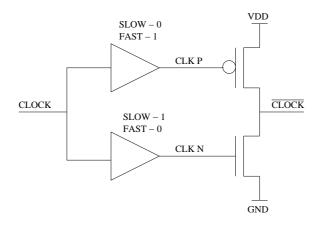

| Figure | 5.18: | A high impedance inverting buffer                                 | 104 |

| Figure | 5.19: | Electrical Scheme for Tri-State Buffer                            | 105 |

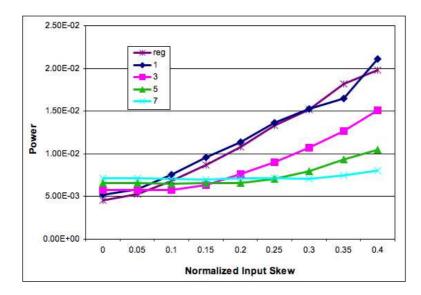

| Figure | 5.20: | Power vs. Input Skew for delays clock                             | 107 |

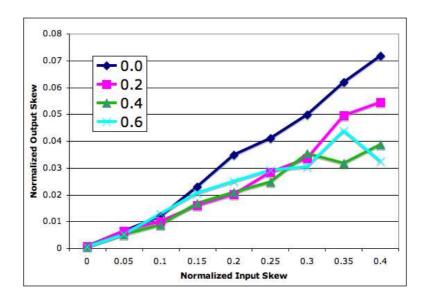

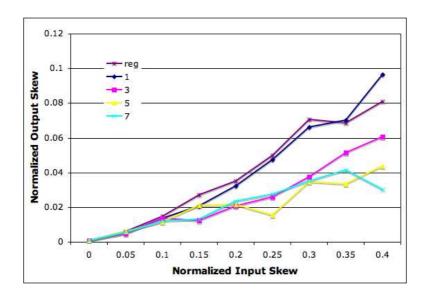

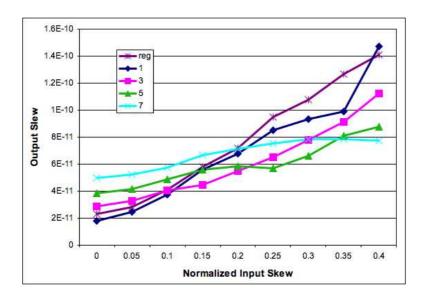

| Figure | 5.21: | Output Skew vs. Input Skew for delays clock                       | 108 |

| Figure | 5.22: | Output Slew vs. Input Skew for delays clock                       | 108 |

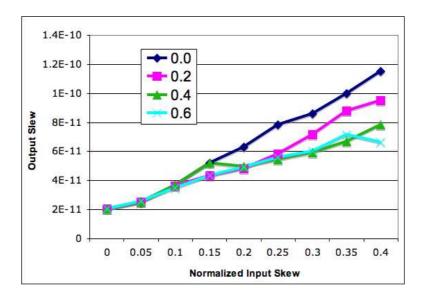

| Figure | 5.23: | Power vs. Input Skew for proposed buffer                          | 109 |

| Figure | 5.24: | Output Skew vs. Input Skew for proposed buffer                    | 110 |

| Figure | 5.25: | Output Slew vs. Input Skew for proposed buffer                    | 110 |

| Figure | 5.26: | Master-slave positive edge-triggered register, using multiplexers |     |

|        |       | (RABAEY, 1996)                                                    | 113 |

# LIST OF TABLES

| Table 3.1: | Test chip statistics                                                                                                  | 40 |

|------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2: | TLM partition information                                                                                             | 43 |

| Table 3.3: | $3\sigma$ variations for different parameters                                                                         | 44 |

| Table 3.4: | Capacitance distribution (%) for mesh architecture                                                                    | 45 |

| Table 3.5: | Mesh architecture vs. tree architecture                                                                               | 45 |

| Table 3.6: | Comparing Mesh and MLT architectures                                                                                  | 46 |

| Table 3.7: | TLM architecture evaluation                                                                                           | 47 |

| Table 3.8: | Reduction of uncertainty by mesh                                                                                      | 47 |

| Table 4.1: | Runtime on a real design with about 300K FFs. Parallel execution                                                      |    |

|            | assumes 4 processors.(CHEN et al., 2005)                                                                              | 72 |

| Table 4.2: | Runtime comparison between macromodel-based simulation and                                                            |    |

|            | SPICE simulation (YE et al., 2008)                                                                                    | 74 |

| Table 4.3: | CPU time comparison of CSAV and Hspice (unit: second) (ZHANG                                                          |    |

|            | et al., 2008)                                                                                                         | 76 |

| Table 4.4: | Runtime comparison. Time Unit: Seconds (WANG; KOH, 2007) .                                                            | 78 |

| Table 4.5: | CPU time comparison of CSAV and Hspice (unit: second) (ZHANG                                                          |    |

|            | et al., 2008)                                                                                                         | 81 |

| Table 5.1: | Buffer model vs. HSPICE comparison (VENKATARAMAN et al.,                                                              |    |

|            | $2006)  \dots $ | 84 |

| Table 5.2: | Results for mesh reduction (VENKATARAMAN et al., 2006)                                                                | 85 |

| Table 5.3: | Summary of optimization results for all test cases                                                                    | 88 |

| Table 5.4: | Reducing buffer sizes                                                                                                 | 93 |

| Table 5.5: | Benchmark Set                                                                                                         | 98 |

| Table 5.6: | Arrival time characteristics                                                                                          | 98 |

| Table 5.7: | Sizing Improvement for a 20% mean input skew with 7% sigma .                                                          | 99 |

# **ABSTRACT**

Process and environmental variations are a great challenge to clock network designers. Variations effect on the clock network delays can not be predicted, hence it can not be directly accounted in the design stage. Clock mesh-based structures (i.e. clock mesh, clock spines and crosslinks) are the most effective way to tolerate variation effects on delays. Clock meshes have been used for a long time in microprocessor designs and recently became supported by commercial tools in the ASIC design flow. Although clock meshes have been known for some time and its use in ASIC design is increasing, there is a lack of good analysis and optimization strategies for clock meshes. This thesis tackles both problems.

Chapter 1 presents a basic introduction to clock distribution and important definitions. A review of existent clock distribution design strategies is presented in chapter 2. A study about the clock distribution architecture used in several microprocessor and a comparison between mesh-based and pure tree clock distribution architectures is shown in chapter 3.2. A methodology for enabling and speeding up the simulation of large clock meshes is presented in chapter 4. The proposed analysis methodology was shown to enable the parallel evaluation of large clock meshes with an error smaller than 1%. Chapter 5 presents two optimization strategies, a new mesh buffer design and a mesh buffer sizing algorithm. The new mesh buffer design was proposed improving clock skew by 22% and clock power by 59%. The mesh buffer sizing algorithm can reduce clock skew by 33%, power consumption by 20% with at the cost of a 26% slew increase. At last conclusions are presented on chapter 6.

**Keywords:** Clock, Clock mesh, Skew, High performance, Microprocessor, Variability.

# 1 INTRODUCTION

The clock is the most important signal in any synchronous design. It controls the instant data is stored inside every sequential element. If clock timing is not extremely accurate, invalid data can be stored inside sequential elements. The clock period must be defined in such a way that data will always be ready and stable before clock edge arrives at the clock sinks.

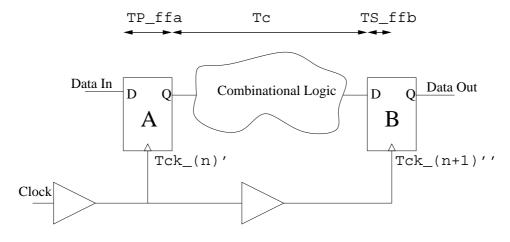

Figure 1.1 shows the timing parameters that must be considered to safely determine clock frequency. Assume that  $T_{CK}(n)'$  is clock arrival time at flip-flop A, at clock cycle n and  $T_{CK}(n+1)''$  is clock arrival time at flip-flop B during clock cycle (n+1). Data propagation time throught flip-flop A is represented by  $TP_{FFA}$ . Combinational logic delay is represented by  $T_C$  and flip-flop B setup time is represented by  $TS_{FFB}$ . Clock period,  $T_{CLOCK}$ , is defined by equation 1.1.

$$T_{CLOCK} \ge TP_{FFA} + T_C + TS_{FFB} + (T_{CK}(n)' - T_{CK}(n+1)'')$$

(1.1)

Equation 1.1 represents a lower bound to the clock period. To assure the correct behavior of a synchronous design it is necessary to guarantee that equation 1.1 is going to be respected for any path connecting any two flip-flops in the design. Besides that, it is also required that all delays associated to the combinational and to the sequential logic of the design obey the robustness property (GUNTZEL, 2000) (i.e. all sequential and combinational delays have to be a safe upper bound for the actual delays).

As can be seen in equation 1.1 the clock period has to be larger than the sequential delays plus the combinational delays plus the difference between the clock

Figure 1.1: Clock period definition

arrival time at the flip-flops A and B for any clock cycle. Since clock arrival time can change from cycle to cycle due to the effect of environmental variations an upper bound on the maximum difference between the two arrival times has to be considered when defining the clock period. Besides accounting for clock arrival time variations the clock period also has to consider the maximum difference between clock arrival times at any two flip-flops connected by a combinational path.

The maximum difference between all clock arrival times at sequential elements input is called clock skew. As discussed above, in order to assure that data will be ready to be stored when clock edge arrives at a sequential element, it is necessary to account for the clock skew in the clock period definition. Therefore it is important to design a clock network in which clock arrival times are almost the same for all sequential elements, i.e., clock skew is much smaller than clock period.

Clock skew affects not only the clock period definition but also the timing constraints related to fast paths in combinational logic. Fast paths can cause the circuit to fail whenever clock skew is larger than the path delay added to the propagation delay of the input flip-flop and to the hold delay of the output flip-flop. Considering the example illustrated in figure 1.1 the minimum delay allowed to any path connecting flip-flops A and B is defined by equation 1.2 in which  $TH_{FFB}$  represents the hold time for flip-flop B. This condition is also known as race condition (WESTE; ESHRAGHIAN, 1985). To assure the correct behavior of the design all race conditions must be satisfied.

$$Tp_C \ge TH_{FFB} - TP_{FFA} + (T_{CK}(n)' - T_{CK}(n+1)'')$$

(1.2)

Avoiding race condition is easy since it is necessary only to increase the delay of paths that violate this condition. (RESTLE et al., 2001) discusses in more details how to address this problem.

## 1.1 Definitions

In order to make the comparisons and analysis presented in the next sections clear some important concepts related to the clock signal timing are defined in this section. Section 1.1.1 defines how to compute clock arrival times, delays and transition times. Section 1.1.2 defines the meaning of clock skew and section 1.1.3 defines what clock jitter is. Sections 1.1.4 and 1.1.5 discusses the differences between process variations and environmental variations and their effects on clock timing.

# 1.1.1 Clock Timing

In this work the clock arrival time at a given node n, At(n), is given as the time when the voltage at n reaches Vdd/2 during a transition. Arrival times are measured with respect to the time the simulation starts. Arrival times can be measured during both, rise and fall transitions, in either case arrival times are measured at Vdd/2.

Given a circuit element E with i inputs and a single output, the delay of E with respect to the input  $j, j \geq 0 \land j < i$ , is given by the difference between the signal arrival time in the output of e minus the signal arrival time in the input j of e,  $D(E,j) = At(E_{out}) - At(E_j)$ . Therefore the delay of E, D(E) is defined as  $D(E) = max_jD(E,j) = At(E_{out}) - At(E_j)$ . Delays can be associated with fall and rise transitions, a fall delay is associated with a falling transition in the output of E, while a rise delay is associated to a rise transition.

Another important timing characteristic of the clock signal is the time it takes during a transition, this is called clock slew. In a falling transition clock slew at a given node n,  $Sl_{FALL}(n)$ , is defined as the time when the voltage at n reaches 10% of Vdd minus the time it reaches 90% of Vdd, i.e.,  $Sl_{FALL}(n) = T_{10\%} - T_{90\%} \mid V_n(T_{10\%}) = Vdd \times 0.1 \wedge V_n(T_{90\%}) = Vdd \times 0.9$ , where  $V_n(T)$  is voltage at the node n at the time T. Analogously, the rise slew can be defined as:  $Sl_{RISE}(n) = T_{90\%} - T_{10\%} \mid V_n(T_{90\%}) = Vdd \times 0.9 \wedge V_n(T_{10\%}) = Vdd \times 0.1$ . It should be noticed that the rise slew can only be computed during a rise transition while the fall slew can only be computed during a fall transition.

# 1.1.2 Clock Skew

Considering a set containing n instances  $I = (i_0, i_1, ..., i_n)$  and a set with m clock sinks  $S = (s_1, s_2, ..., s_m)$ , a path, p, can be defined as p = (E, F), where  $E \subset I$  and  $F = (s_i, s_j) \mid s_i, s_j \in S$ . A circuit C is defined as  $C = (p_1, p_2, ..., p_n)$ . Let us define the clock propagation time from the clock source to a clock sink  $s \in S$  as D(s). Now consider a function  $conn(C, s_i, s_j)$  that is defined as:

$$conn(C, s_i, s_j) = \begin{cases} 1 & \text{if } \exists p \Rightarrow (s_i, s_j) \in p \mid s_i, s_j \in S \\ 0 & \text{if } \neg \exists p \Rightarrow (s_i, s_j) \in p \mid s_i, s_j \in S \end{cases}$$

(1.3)

The clock skew, Sk, for a circuit C can be defined as:

$$Sk(C) = \{ max_{s_i,s_i}(|D(s_i) - D(s_j)|) \mid conn(s_i, s_j) = 1 \lor conn(s_j, s_i) = 1 \}$$

(1.4)

The definition presented by equation 1.4 means that the clock skew of a circuit is given by the maximum difference at the clock arrival time at any two flip-flops connected through some combinational path. Although the circuit topology is fixed the circuit delays may not be. Since clock skew may change according to process and environmental variations it is necessary to model its effect on clock delays. To account for this variation another concept is used, the concept of clock jitter.

#### 1.1.3 Clock Jitter

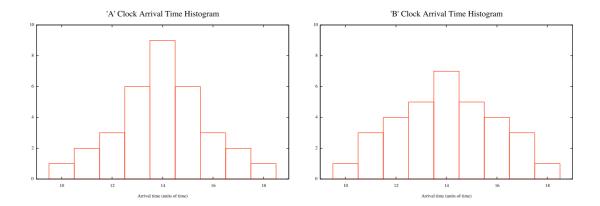

Clock signal behavior has become extremely non-deterministic due to the effect of variability sources. The clock jitter concept quantifies the effect of variability on clock timing behavior. Consider that for a given circuit the clock arrival time observed at a clock sink A is described by the histogram A Clock Arrival Time Histogram of figure 1.2 while the arrival time observed for a clock sink B is described by histogram B Clock Arrival Time Histogram. Comparing both histograms it can be seen that the smallest and largest arrival times observed are the same for A and B but histogram A has a higher occurrence of values closer to its mean while histogram B arrival times are further spread away from the mean. If the clock arrival time variation for clock sinks A and B were modeled only by the minimum and maximum values observed the information about how the arrival times are spread between the minimum and maximum values would be lost.

Assuming that the clock arrival time at a given clock sink s is modeled according to a given Gaussian probability density function (PDF) described by the mean and standard deviation pair  $(\mu, \sigma)$  the jitter at s, J(s), is defined as  $J(s) = 3 \times \sigma$ . By assuming that arrival times are Gaussian distributions and describing jitter as three

Figure 1.2: Clock arrival time histogram

Figure 1.3: SSTA in clock skew computation

times the standard deviation the information regarding how the arrival times are distributed is preserved and can be precisely retrieved.

Many authors study how to better model the effect of variability sources using different PDFs. The formal definition of jitter presented above is valid in the scope of this work only. If arrival times are modeled in any other way than by Gaussian distributions the definition of jitter may change. In a broader sense, jitter can be defined as how, and how much the arrival time of a signal changes in respect to time.

## 1.1.4 Process Variability

Process variability describes any source of variability that affects the performance of a chip due to variations in the fabrication process. The effect of process variability in the performance of ICs has become a major concern for chip designers. If process variations are not taken into account in early design stages final production yield will be low.

Process variability has to be accounted in a statistical fashion. Process variability effects on different circuit parameters are obtained by measuring a set of samples. By knowing the probability distribution for each electrical parameter value, a chip can be designed accounting for the effect of process variability on its electrical behavior.

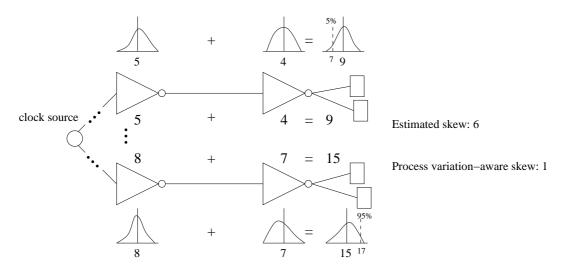

Figure 1.3 shows the different methodologies used to consider the effect of process variations in the circuit timing affect the final yield. It should be noticed that the values presented in the example above are very rough and its only purpose is to illustrate how process variations should be dealt. By performing a statistical analysis on the delay distribution of each gate for all the paths, it is possible to compute the delay distribution for each path in the clock network. The mean for the delay distribution for each gate. The mean value means that there is a 50% chance that the actual delay of a path will be smaller than the mean and 50% chance it will be greater than it. Considering the slowest clock path in the clock network, it means that half of fabricated circuits will present a delay smaller than the mean delay for this path. The same is true for the fastest path in the clock network. 75% of fabricated circuits will not properly work because one of these situations will happen:

- The delay of the slowest and the fastest path will be smaller than the mean delay.

- The delay of the slowest and the fastest path will be faster than the mean delay.

- The delay of the slowest path will be smaller than the mean delay and the delay of the fastest path will be faster than the mean delay.

This design strategy represents a large yield loss. One approach to maximize fabrication yield is to replace nominal gate delays by safe lower bounds and upper bounds to compute safe delay estimates. Let us assume that for the slowest instead of using delays of 5 and 4 for the first and second inverters respectively values of 3 and 2 are used. As it was mentioned before it is know that 50% of the times the first inverter will be faster than 5, therefore, if we assume that the delay of the first inverter is 3 maybe only 5% of the times the delay of this inverter will be smaller than 3. The same idea can be applied to the second inverter in the fastest path. If conservative estimates are added up the final path delay is 5 instead of 9 when nominal values are considered. The analogous procedure can be applied to the slowest path. The final delay estimates are safe for a great majority of chips but they are also very conservative and may demand more effort from the chip designer to meet the timing constraints.

To maximize fabrication yield and reduce the timing analysis pessimism the design should be analyzed statistically-wise. Instead of adding up conservative gate delays estimates each path delay should be computed by adding up the PDFs representing each gate delay. In the example presented in figure 1.3, if 7 is assumed to be the delay for the fastest path only 5% of the times this path will present a delay smaller than 7; while for the slowest path if 17 is used instead of 15 only 5% of the times this path will present a delay larger than 17. This means than only 9.75% of the times either the slowest or the fastest paths will present a delay that violates the estimate. Computing PDFs for circuit delays reduces the timing analysis pessimism because it accounts to the fact that if a gate was slowed down it can be compensated by other gates that can get faster due to process variations also. Another advantage is that statistical analysis allows a much better prediction of yield.

# 1.1.5 Environmental Variability

Environmental variations are variations in the electrical behavior of the circuit elements caused by temperature, crosstalk or voltage variations. This sort of variation can not be treated in the same way as process variations are. Even events with a very low probability may happen since they are a result of the environment variations. Changes in the operating environment can occur at any minute.

Variations in the supply voltage level are the most significant environmental variation effect affecting the clock network. Supply level variations are caused by the IR drop effect. When data switches, capacitances are charged by the VDD network and discharged through GND. In order to charge and discharge the capacitances current flows through the power supply lines. Since power supply lines are not zero resistance lines current flowing through their lines causes voltage to drop (for VDD) or rise (for GND). More details about IR drop effect on clock skew can be found at (SALEH et al., 2000).

It is necessary to be pessimistic when treating environmental variations. This is done by analyzing the circuit at different corners. For a set of environmental parameters E in which  $E = (e_0, e_1, ..., e_n)$ , each corner is a set of values  $V_k$ , where each value corresponds to one environmental parameter. For each set of values (i.e. corner)  $V_0, V_1, ..., V_r$ , the circuit has to be evaluated. Corner values have to be carefully chosen to guarantee that after the evaluation of all corners the worst case scenario was evaluated.

# 1.2 Motivation

Design of clock distribution architectures for synchronous digital circuits is an increasing complexity task. As technology advances, scaling allows designing faster combinational blocks. (MEHROTRA; BONING, 2001) shows that process and environmental variations are responsible for increasing clock skew in comparison to clock period. It is shown that clock skew due to variations divided by clock period almost doubles from a 180nm technology to a 50nm technology. Since delay of combinational blocks and delays related to the synchronous circuitry are decreasing, clock frequencies are becoming more dependent on the skew of the clock distribution architecture.

Besides process and environmental variations influence, other aspects contribute to the increasing importance of reducing the clock skew such as:

- Area increase: Chip area is rapidly increasing in relation to the transistor dimensions. As the chip area increase more resources are needed to route the clock to all sequential elements (e.g. more buffers need to be added, wire lengths increase). Therefore the clock distribution architecture becomes more sensitive to variations and harder to be tuned.

- Design complexity: Increase in the complexity of the designs demands precise engineered clock architectures. New designs often use more than one clock frequency. Macros used in the design usually represent an obstruction to clock lines. As the number of macros increases the complexity to route the clock lines with a small skew also increases.

• New effects: Clock frequencies are increasing to gigahertz scale. Some effects that could be safely overlooked for smaller frequencies must be taken into account now (e.g. inductance and transmission line theory (THOMSON; RESTLE; JAMES, 2006)).

Another important aspect in the design of clock architecture is power consumption. (GRONOWSKI et al., 1998) shows that 40% of the total circuit power can be spent on the clock distribution. In more recent microprocessor designs the total amount of power consumed by the clock network is about 25% (ALIMADADI et al., 2008). Power constraints are becoming tighter. Design strategies such as clock meshes or clock spines can distribute a low skew clock signal by the cost of a high power consumption. This sort of approach may not be suitable in a near future where clock power consumption has to be minimal. Solutions for reducing power dissipated by the clock architecture without affecting its performance must be further researched.

Although clock meshes are becoming more present in high performance designs we can observe a lack of optimization and analysis techniques for clock meshes. The current techniques for low power clock distribution designs target at tree-based distribution and can hardly be applied to clock meshes. Besides, clock mesh analysis is very costly due to its long electrical simulations times. In order to develop any optimization technique for clock meshes it is necessary first to develop an accurate and efficient analysis methodology. By reducing clock mesh power consumption and making it easier to be characterized we expect to widen the range of designs in which clock meshes can be applied.

# 1.3 Thesis Proposal

This thesis presents solutions to analyze and optimize clock meshes. In chapter 2 several design strategies used in clock networks are discussed. In chapter 3, the clock distribution architectures used in the latest microprocessor designs are presented. A comparison between clock meshes and clock trees is also provided. Both studies motivate the use of clock meshes as a way to design variability tolerant clock distributions.

In order to optimize clock meshes we must first analyze them. Chapter 4 offers a simple methodology to enable the analysis of large clock meshes through electrical simulation. Related works are also studied and compared to the proposed methodology.

Two independent optimization techniques are presented in chapter 5. One technique proposes a new design for clock mesh buffers reducing power consumption and improving clock skew by a large factor. The second technique proposes a clock mesh buffer sizing algorithm that improves power and clock skew with a minimum penalty on clock slew. Other clock mesh optimization techniques present in the literature are also presented. However, the optimization techniques proposed in this work are fundamentally different from all other mesh optimization techniques. We propose to optimize the clock mesh considering the timing of the clock network driving the clock mesh while the other methodologies optimize the clock mesh assuming that the clock signal arrives at the clock mesh times perfectly synchronized.

At last, in chapter 6 we present some concluding remarks and discuss about the future directions of this work. In summary, the main contributions of this work are:

- To summarize a clock distribution scheme for microprocessors. A large set of microprocessor clock distribution architectures was studied. The details for each clock distribution scheme were reported in chapter 3. Section 3.3 summarizes the most significant characteristics of each microprocessor clock distribution by describing a generic clock distribution for microprocessors.

- To compare skew mesh-based clock distribution architectures to a pure tree clock distribution. Section 3.2 compares the clock skew and power consumption among a pure mesh architecture, two hybrid architectures and a pure tree clock distribution. This study allows us to notice the effectiveness of clock meshes in reducing clock skew.

- To propose a simple and effective methodology to enable large meshes electrical simulation. Section 4.2 describes the proposed methodology to simulate large clock meshes. This was the first work to address this problem. Related works later proposed are described and discussed in section 4.3.

- To propose two new strategies for clock mesh optimization. Previous work has been done on clock mesh optimization, but current mesh optimization techniques optimize clock meshes assuming that a perfectly synchronized clock signal is applied to the clock mesh. The two mesh optimization strategies described in chapter 5 are the first ones to address the problem of clock mesh optimization considering the different clock arrival times at the mesh buffers.

The work related to the architecture evaluation study presented in section 3.1 and related to the proposed analysis methodology in chapter 4 were developed while the author was on an intership at Fujitsu Laboratories of America and were developed in coperation with other authors. The author of this thesis has worked, more specifically, on the evalution study of the TLM architecture reported in section 3.1.1.3 and on the study of the effect of the border used to increase the accuracy of the SWS methodology reported in section 4.2.3. The main contribution of this thesis relies on the optimization methodologies proposed in chapter 5.

# 2 CLOCK DESIGN STRATEGIES

Clock distribution has always been an issue for IC designs. Due to this fact, several strategies to address the problem of delivering a high performance clock signal respecting power constraints were developed. In this chapter some of these techniques are presented. The first section presents techniques that tackle at increasing robustness of clock distribution network to noise sources. Section 2.2 presents techniques to reduce clock power consumption. Section 2.3 presents different clock routing topologies. The last section, 2.4, presents architectural level techniques to improve the clock network performance.

# 2.1 Reliability

Clock is the most important signal in any synchronous design. Any glitch in the clock signal can cause many sequential elements to store corrupted data. Clock designers must guarantee that clock is glitch free. Technology scaling increases design sensitivity to noise source due to the increase in the coupling capacitances and decrease of supply voltage levels. This section address techniques to prevent noise sources to affect the correct behavior of the clock signal.

# 2.1.1 Shielding

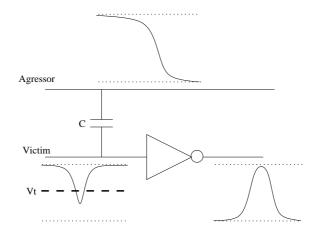

Clock lines must be protected from crosstalk noise. Crosstalk can either speedup or delay the clock signal or even cause a glitch. When two aggressors, the clock wire and a neighbour wire, are switching to the same final value, both signals are going to be sped up. If they switch to opposite values, they will get delayed. When clock is steady, if coupling capacitance is strong enough, a crosstalk aggressor can cause a glitch in the clock wire (victim) as illustrated by figure 2.1.

The best way to protect clock signal from crosstalk aggressors is by shielding it. Shielding relies on adding wires connected to ground or Vdd to protected signal's neighbor tracks. Usually shield wires are added only in the same layer as the protected signal's layer.

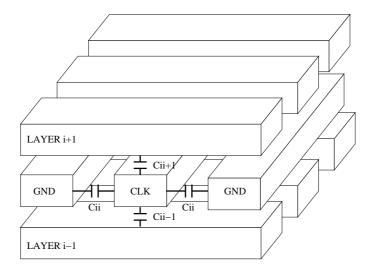

Top and bottom layers are usually not shielded. Multi metal layer designs usually adopt a routing strategy in which every metal layer follows a preferred orientation, except for metal 1 layer. If metal 2 allows only vertical wires metal 3 will allow only horizontal wires, in such a way there will be no neighbor layers following the same orientation. Coupling capacitance between nets on different metal layers is minimal since they are not running in the same orientation. Coupling capacitance between metal 1 and metal 2 layers is also minimal. Although metal 1 allows wires to be

Figure 2.1: Glitch caused by crosstalk noise

Figure 2.2: Routing management for different metal layers

added with any orientation those wires are very short since metal 1 layer is used only for internal cell connections.

Figure 2.2 shows how the routing layers orientation management affects parasitic capacitances. The intersection between wires on different layers is minimal. Coupling capacitance between nets on different layers is not important for crosstalk effects. Unless all aggressors switch in the same direction at the same time they will not affect a victim on a different layer. Neighbor wires on the same layer can have a large coupling capacitance since they can be side by side for a long distance. For these reasons, the capacitance Cii illustrated in figure 2.2 is much larger than  $Cii\pm 1$  and therefore shielding can be performed only within the same layer. If shielding were performed also on top and bottom layers, the routability on those layers would be severely affected.

Shielding is usually applied on the higher branches of clock networks. It can lead to a huge resource utilization penalty if applied to the whole clock network.

# 2.1.2 Differential Signaling

Differential signaling relies on sending a signal through the voltage difference in a pair of wires. This approach protects the signal against crosstalk and allows

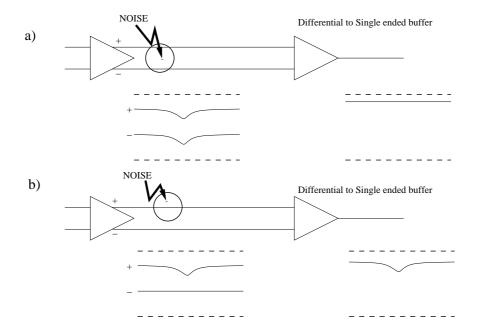

Figure 2.3: Differential signaling noise immunity

the signal to be transmitted using a reduced voltage swing. The differential pair is routed side by side. The differential signal needs to be converted back to a single ended signal before reaching the flip-flops. Usually only the higher branches of the clock network are protected by this technique since each sink of the protected portion of the clock networks requires a differential to single ended converter. The closer to the flip-flops a differential signal is taken higher is the number of converters required, increasing the overhead associated to this technique.

By encoding the information in the voltage difference of a pair of wires any noise source affecting both wires of the differential pair would be filtered. Only when a single wire of the differential pair is affected noise can be observed. Figure 2.3 illustrates both situations.

Shielding is still desired since any aggressor in the same layer would affect mostly a single wire in the pair. The increased protection against noise allows the voltage swing to be reduced, reducing power consumption. This technique does not necessarly improves power since differential voltage repeater and differential to single ended converters consume more power than an inverter.

# 2.2 Low Power

Keeping clock power consumption within its budget is an increasing complexity task. The clock frequency increase linearly increases clock power consumption. At the same time, electronic market demand for low power products is pushing ASIC power consumption down. For many current designs, power constraints have become more important than timing constraints. This section presents two techniques used to reduce clock power consumption.

## 2.2.1 Clock Gating

Clock gating consists in freezing the clock signal for regions of the chip that are not being used. Regions where clock is frozen are said to be on sleep mode.

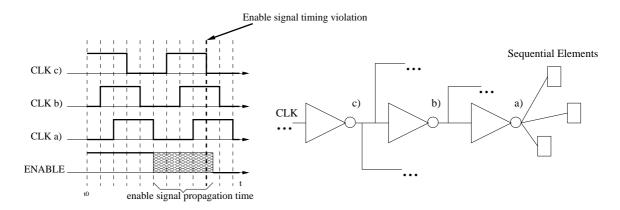

Figure 2.4: Enable signal timing issues

Figure 2.5: Clock gater design

When clock is not switching dynamic power consumption is reduced to zero since no transitions occur in these regions. Clock signal can be set either to zero or one in sleeping regions. All regions in sleep mode are unable to process any data. Sleeping regions are able to restore all information stored in sequential elements after exiting from sleep mode.

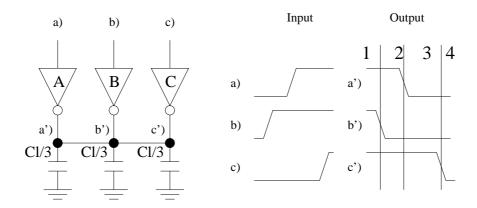

Since a large part of dynamic power consumption comes from the clock network itself, gating clock close to the clock root saves more power than gating it close to the clock sinks. It should be noticed that enable signal timing must be respected when deciding in which stage clock is going to be gated. The closer to the root clock signal is gated, shorter is the time for enable logic to be stable. Figure 2.4 demonstrates how moving clock gaters towards the clock root compromises enable signal timing. In this example clock gaters can not be added above stage c) since enable signal would only be captured in the next clock cycle from this point on.

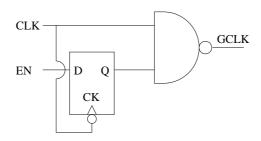

Besides respecting timing constraint, clock gater cells must be glitch free. Enable signal glitches should not propagate to clock lines, since clock glitches cause the circuit to fail. A possible way to prevent enable signal glitches to propagate through the clock gater is by adding a negative level triggered latch as illustrated by figure 2.5. When clock is at level '0' the gater output is set to level '1'. When clock is at level '1' the gater output will be determined by the value stored in the latch.

# 2.2.2 Reduced Swing

One effective way to reduce clock network power consumption is by reducing capacitance charge/discharge power consumption. Equation 2.1 shows how capacitance charge/discharge power is computed

$$P = f \times C_L \times Vdd \times Vs \tag{2.1}$$

where f is the switching frequency,  $C_L$  is the load capacitance, Vdd is the supply voltage and Vs is the output swing of the buffers.

The most effective way to reduce power consumption according to equation 2.1 is by reducing Vdd, since Vs is a fraction of Vdd and most often Vs = Vdd. By reducing Vdd dynamic power consumption is reduced quadratically. Dynamic power consumption could be reduced in a linear fashion by reducing only Vs.

Changing supply voltage and voltage swings for all elements in a chip would heavily affect timing characteristic. A better approach is to change Vdd and Vs only for the clock distribution network. Since clock sinks are not going to be affected by the voltage reduction it is necessary to convert clock back to the standard voltage swing before sinks are reached. (PANGJUN; SAPATNEKAR, 2002) and (IGARASHI et al., 1997) assume that the best approach to minimize clock power is to design most of the clock network within the low power region, i.e., voltage swing is reduced at clock root and restored only before reaching clock sinks. This solution is optimal if power consumption at voltage converters is equivalent to a single inverter power consumption. Adding voltage swing converters in the last stage of the clock distribution maximizes area and power overhead introduced by voltage swing converters since the last level of the clock distribution requires more drivers than any other level of the clock network.

As discussed above, there are two distinct ways of reducing voltage swings in the clock network. It can be reduced either by reducing Vdd for all the elements in the clock network or only by reducing the voltage swing without changing Vdd. Although using different vdds, Vddh and Vddl, for the clock network and for the rest of the chip can save more power, it adds design complexity since another power signal must be distributed over the chip and low Vdd clock cells can only be placed in the regions where Vddl is available. It should also be noticed that reducing voltage swing of any signal makes it more sensitive to noise.

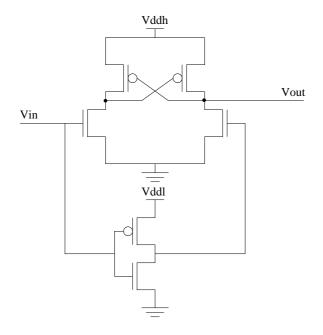

## 2.2.2.1 Multiple Supply Voltages

Using multiple supply voltages allow a low power consumption in low Vdd regions. Low Vdd regions power consumption is reduced quadratically with respect to the Vdd reduction. Assuming that a region that was initially connected to Vddh is now connected to Vddl, where  $Vddl = 0.9 \times Vddh$ , the dynamic power reduction in this region should be in the order of  $0.9^2$  (i. e. 19% reduction from a 10% Vdd reduction).

The design of a Vddh to Vddl converter is straightforward, it consists of a regular inverter supplied by Vddl. Vddl buffers are regular inverters in which VT is adjusted to the new supply voltage values. The design of the Vddl to Vddh converter is more complex. Its design is illustrated by figure 2.6. This approach was used in (IGARASHI et al., 1997).

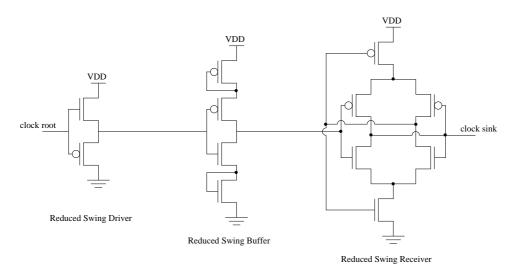

# 2.2.2.2 Reduced Voltage Swing

Conversion from a full swing signal to a reduced swing signal is done by a reduced swing driver. In order to prevent huge delays introduced by interconnection RC, reduced swing buffers are required. Reduced swing buffers receive a reduced swing signal in its input and transmit a reduced swing signal in the output. Since clock sinks require a full swing signal, a reduced swing receiver is required to convert clock signal from a reduced swing back to a full swing.

Figure 2.6: Vddl to Vddh converter

Figure 2.7: Reduced swing driver, buffer and receiver

Figure 2.7 presents the design of all the elements required by the reduced swing clock scheme. The reduced swing driver illustrated in the figure was presented in (HANAFI et al., 1992), the reduced swing receiver was presented in (ZHANG; RABAEY, 1998) and the reduced swing buffer was proposed in (PANGJUN; SAPATNEKAR, 2002).

# 2.3 Routing Topologies

Clock skew, power consumption and tolerance to variations is extremely dependent on the clock routing. Clock routing has the complex task of equalizing the delays from the clock source to each clock sink. At the same time, the longer is the clock routing the higher the power consumption, clock skew and sensitivity to variations are going to be. Usually different routing strategies are used in different levels

Figure 2.8: Htree example

Figure 2.9: Fishbone routing connecting clock sinks to htree sink

of the clock distribution. Each routing strategy presents advantages and disadvantages. The routing strategy has to be selected according to the constraints of each design. This chapter presents five of the most commonly used routing strategies and discusses the advantages and disadvantages of each one.

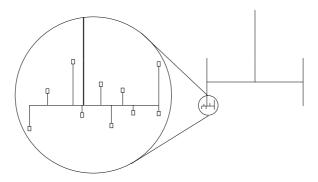

#### 2.3.1 Htree

An htree is a symmetric tree in which wire length from any sink to the root is the same. Figure 2.8 is an illustration of an htree topology. This figure shows a topology in which the clock signal is driven from a central location to multiple clock sinks. Since the clock pin may not be located in the center of the chip it is necessary to route the clock from the clock pin to the center of the htree.

The total number of sinks in a htree is usually much less than the total number of clock sinks connected to it. Clock sinks are directly connected to the htree sinks using a fishbone structure, as shown by figure 2.9.

An htree necessarily presents a homogeneous sink distribution in the X and Y axis. Htree can be used to drive the clock signal directly to the flip-flops or to the inputs of a mesh. Although wire lengths are equalized by the htree structure, buffers must be carefully inserted and sized in order to keep skew small. Wire widths can also be changed either to compensate different loads driven by each branch or to satisfy electro-migration rules. In both cases the larger the load driven is larger the wire width should be.

Htree is highly vulnerable to process and environmental variations since varia-

Figure 2.10: Htree vs xtree example (FRIEDMAN, 2001)

tions may unbalance the delays on the different branches of the htree. Htrees are most often applied to ASICs due to its performance limitations. Still, some microprocessors claim to use a clocking scheme based on htrees without using clock meshes, such as, (ANDERSON; WELLS; BERTA, 2002) and (TAM; LIMAYE; DESAI, 2004).

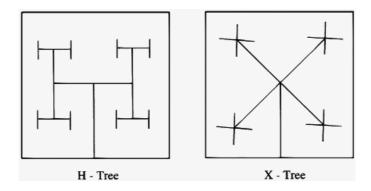

## 2.3.2 Xtree

The xtree architecture is analogous to the htree architecture. Both, xtree and htree present the same wire length from the root to any sink, the difference between them is that the xtree uses 45 degree connections, as shown by figure 2.10. This architecture can be found in the Alpha 1.2GHz microprocessor (JAIN et al., 2001).

The main advantage offered by this architecture compared to the htree is the reduction of total wire length due to 45 degree connections. The wire length reduction comes from the fact that in a square shape with a side length equal to s, the diagonal length (45 degree line) is given by  $s \times \sqrt(2)$  while the Manhattan distance between the opposite corners is given by  $s \times 2$ . By reducing the total wire length a smaller power consumption and smaller clock skew are expected to be achieved.

## 2.3.3 Clock Routing

Clock net requires a very special sort of routing to minimize clock skew. Instead of reducing wire lengths clock routing should try to match, as close as possible, latencies from the root to all sinks. A simple way to do that is by using patterns to equalize the wire length from the clock root to all sinks (e.g. htree and xtree).

Htrees are very easy to build but it presents two major drawbacks, the wire length overhead and the mismatch between htree sinks locations and clock sinks locations. An htree distributes the clock signal to a symmetrical array of buffers that may not match the actual clock sink locations. Extra routing must be added to connect clock sinks to htree sinks, which may increase clock skew.

This section presents two methods to route the clock network from the clock root to the clock sinks with close to zero skew and reduced wire length.

## 2.3.3.1 Method of Mean and Medians (MMM)

The method of mean and medians (MMM) was firstly presented in (JACKSON; SRINIVASAN; KUH, 1990). It can greatly reduce clock skew in comparison to a minimum spanning tree routing and it is also better than an htree for asymmetric

Figure 2.11: MMM algorithm example

Figure 2.12: Clock tree with a a) vertical cut and b) horizontal cut

distributions of clock sinks.

The idea of this algorithm is conceptually simple. Given a distribution of clock sinks, the center of mass of this distribution is computed. The distribution is then divided into two parts by a line crossing at the center of mass either horizontally or vertically. The centers of mass for the two new sink distributions are computed and then connected to the center of mass of the former distribution. This algorithm is executed recursively until each sink distribution is composed by a single sink.

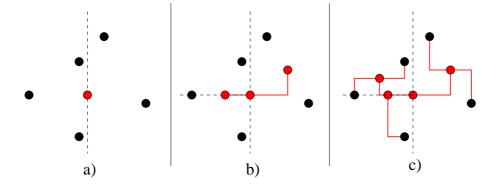

Figure 2.11 illustrates an example of how the algorithm works. In a) the distribution is divided vertically by a line crossing the center of mass. In b) the center of masses for the two new distributions are computed. The centers of mass of the new distributions are connected to the center of mass of the former distribution. The distribution on the left was divided horizontally. The final routing is shown in c).

Deciding whether a set of sinks is going to be divided vertically or horizontally is an important step in this algorithm. Figure 2.12 shows how performing a vertical or a horizontal cut can produce different clock routings. The author in (JACKSON; SRINIVASAN; KUH, 1990) proposes a one level look-ahead strategy to decide which cut should be performed. A horizontal cut followed by a vertical cut is performed, then a vertical cut followed by a horizontal cut is performed. The cut direction that produces the smallest clock skew is chosen.

This algorithm present a  $O(n \log n)$  complexity, where n is the number of sinks in the clock distribution.

Figure 2.13: Construction of a merging segment

# 2.3.3.2 Deferred-Merge Embedding (DME)

The deferred-merge embedding (DME) algorithm is able to generate a zero skew clock tree with minimum wire length. It was proposed in (BOESE; KAHNG, 1992) and in the following years many improvements were proposed to this algorithm. This algorithm requires the clock network topology to be previously defined. It finds the optimal routing for the defined topology.

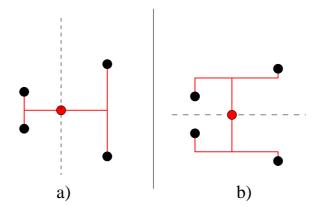

The DME algorithm is divided into two phases, a bottom up phase in which the location of the internal nodes in the clock network are replaced by lines which represent all possible locations, and a top-down phase in which the clock root is fixed and all the internal node locations are fixed thereafter.

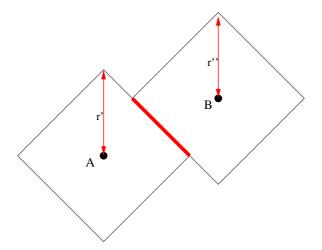

Figure 2.13 shows how a merging segment is constructed when two sinks are merged. If wire lengths need to be matched the merging segment is computed by the intersection of the Manhattan circles with radius r' and r'', where r' equals to r'' which is equal to half of the Manhattan distance between nodes A and B. The same process can be applied when, instead of clock sinks, two segments are merged. In this case, the radius of each Manhattan circle is given by the *minimum Manhattan* distance between both segments.

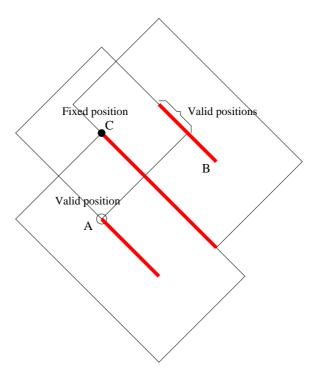

After all the internal node positions were deferred and merged, the position of the clock root is embedded. When the position of a node is fixed the merging segments connected to that node are going to be restricted by this node location. Figure 2.14 illustrates how the set of possible positions to a node is restricted when a position is embedded for its parent. Segment C was built from the merging of segment A and B. When position of C is chosen to be the black dot, the possible positions for A and B are restricted.

The DME algorithm can be modified to, instead of equalizing wire lengths, equalize Elmore Delay values. This algorithm presents a linear complexity in terms of number of nodes in the clock network.

## 2.3.4 Clock Spine

A clock spine is a wire, usually wide, used to take the clock signal from a clock driver across the chip in one dimension. It can be used to deliver the clock to the root of one or several local clock trees. Clock spines are a simplification of a clock

Figure 2.14: Position embedding

mesh, it can be described as a one dimensional clock mesh. Processors such as Intel's Pentium III (SENTHINATHAN et al., 1999) and Pentium 4 (KURD et al., 2001) (KURD et al., 2001) use clock spines.

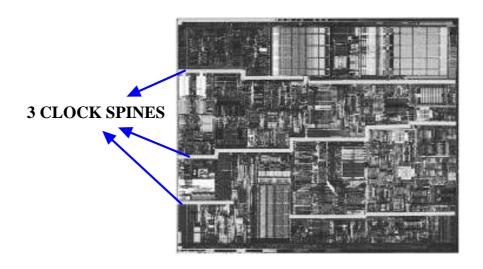

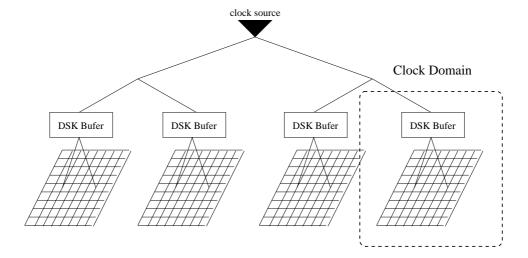

In the design of the clock distribution for the Pentium 4 microprocessor (KURD et al., 2001)(KURD et al., 2001) three clock spines are used. At each clock spine a different binary tree is connected and each binary tree drives a different clock domain.

Figure 2.15 illustrates the three clock spines used in the Pentium 4 design. The clock spines are represented by the white lines crossing the chip in a west-east fashion. Clock spines present a small skew due to the low resistance of its lines. By adding a low skew clock trunk the distance between any clock sink and the clock

Figure 2.15: Pentium Clock Spines (KURD et al., 2001)

Figure 2.16: Mesh architecture example

source is reduced. The total clock skew is also smaller.

Clock spines are not tree-like topologies since it adds cycles to the clock network. Power consumption may be in the same order as a clock mesh with the same number of drivers.

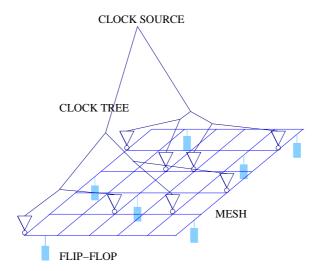

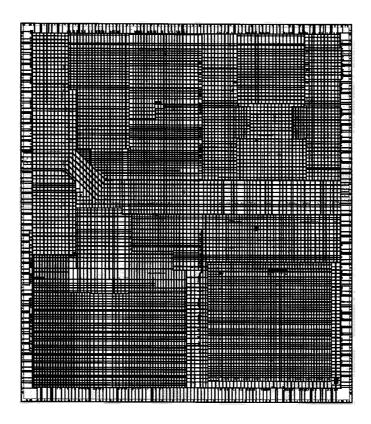

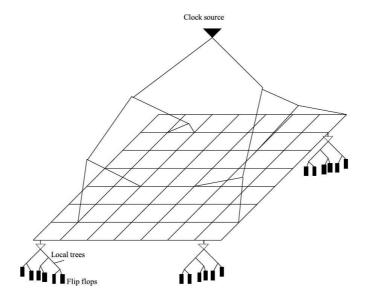

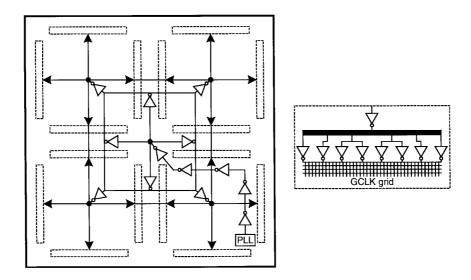

#### 2.3.5 Clock Mesh

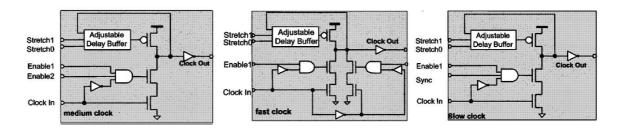

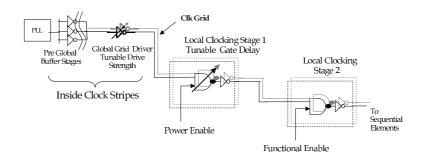

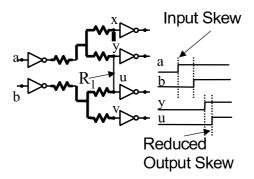

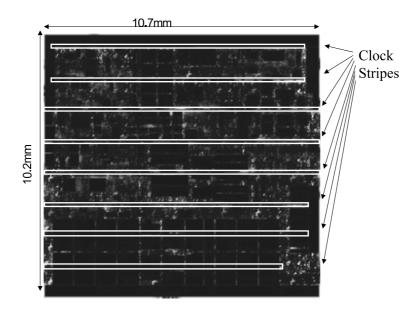

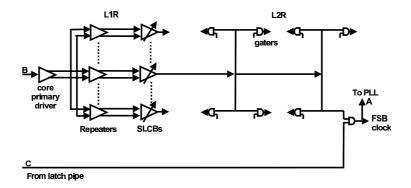

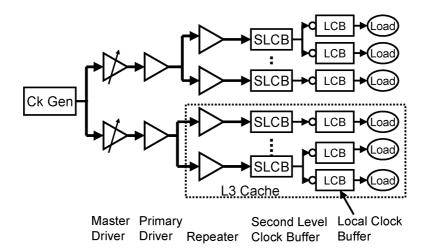

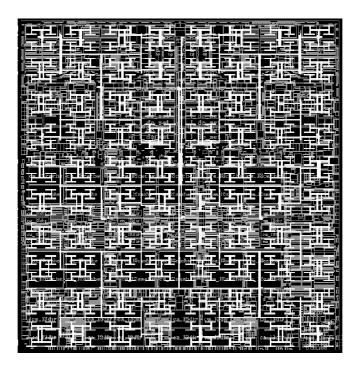

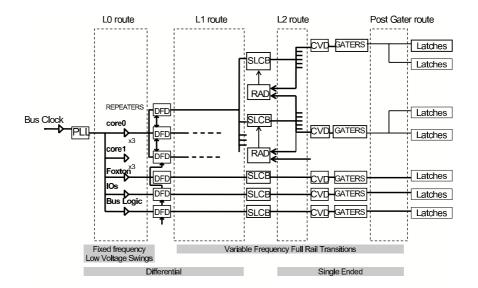

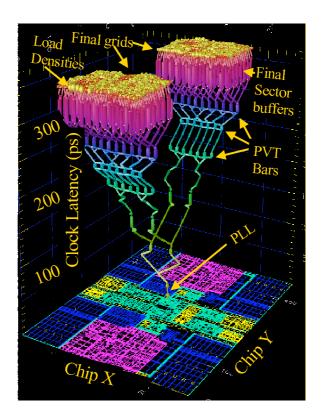

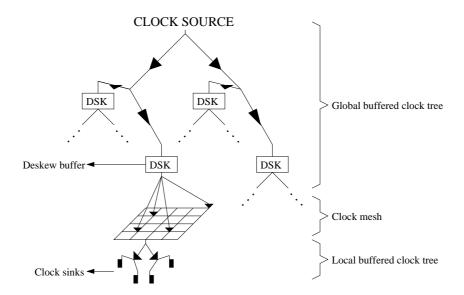

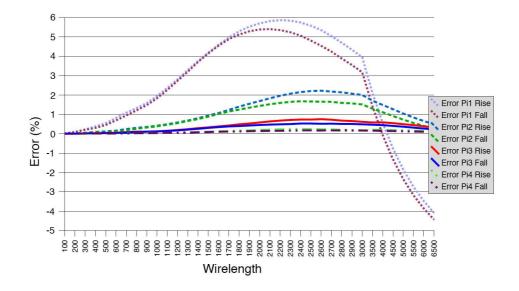

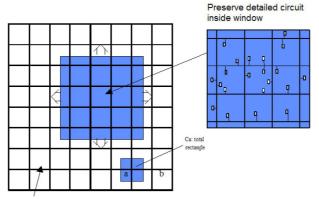

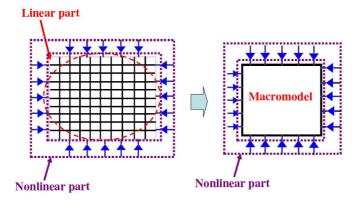

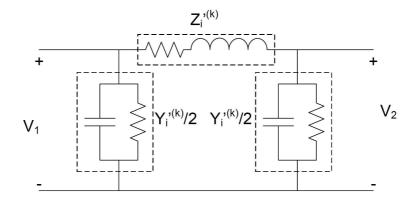

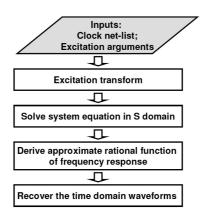

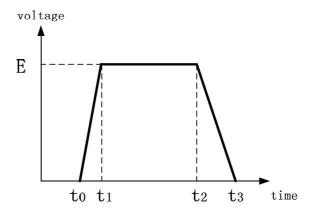

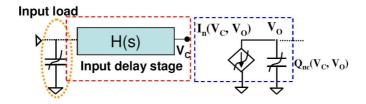

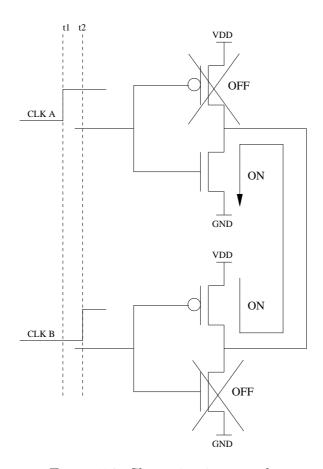

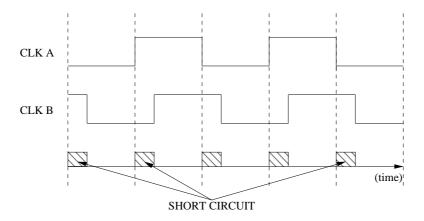

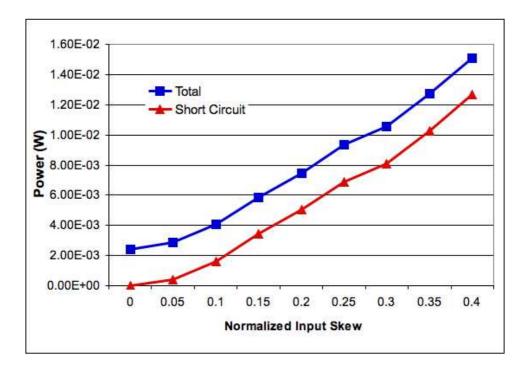

A mesh is a grid composed by wires to which the sequential elements are directly connected. Figure 2.16 illustrates a mesh being driven by a clock source and some elements connected to the mesh wires. Meshes are widely used in the design of the clock distribution for microprocessors (BAILEY; BENSCHNEIDER, 1998), (TAM; LIMAYE; DESAI, 2004), (KURD et al., 2001), (TAM et al., 2000). Reconvergent paths created by the mesh structure are able to smooth out the difference between the clock signal arrival times at the mesh inputs. Since reconvergent paths may produce short circuit currents between the mesh drivers, they are, along with the high capacitance associated with the mesh wire structure, responsible for the higher power consumption in comparison to tree-like clock networks power consumption.