### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

LEOMAR SOARES DA ROSA JUNIOR

## Automatic Generation and Evaluation of Transistor Networks in Different Logic Styles

Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Microelectronics.

Prof. Dr. André I. Reis Advisor

Prof. Dr. Renato P. Ribas Co-advisor

Porto Alegre, July 2008.

# Livros Grátis

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Rosa Junior, Leomar Soares da

Automatic Generation and Evalution of Transistor Networks in Different Logic Styles / Leomar Soares da Rosa Junior – Porto Alegre: Programa de Pós-Graduação em Microeletrônica, 2008.

147 f.: il.

Tese (doutorado) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica. Porto Alegre, BR – RS, 2008. Advisor: André I. Reis; Co-advisor: Renato P. Ribas.

1.Redes de transistores. 2.Células lógicas 3.Mapeamento tecnológico. 4.Teoria de chaves 5.Estilos lógicos 6.Estimativas de células I. Reis, André Inácio. II. Ribas, Renato Perez. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. José Carlos Ferraz Hennemann Vice-reitor: Prof. Pedro Cezar Dutra Fonseca Pró-Reitora de Pós-Graduação: Profa. Valquiria Linck Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PGMicro: Prof. Henri Ivanov Boudinov Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### ACKNOWLEDGEMENTS

I would like to express my gratitude to my parents, Leomar Soares da Rosa and Maria Cecília Machado da Rosa, for their patience, encouragement and love. They were always supporting me and encouraging me with their best wishes.

I would also like to thank my aunt, Gilda Maria da Silva Machado, for her support. All this time that I was far from home she treated me as her son.

I acknowledge my fiancée, Pamela Bilhafan Disconzi. Although we were some kilometers apart, I felt we never were. She shared my all ups and downs over the phone and email and stood by me.

I would like to thank CAPES and Nangate for financial support. And also thank all my colleagues from Nangate-UFRGS Research Lab. They were always willing to help and give their best suggestions.

Finally, I would like to express my sincere gratitude to my advisors, André Inácio Reis and Renato Perez Ribas, for their brilliant guidance and their patience. They were always close and ready to guide me when the things seemed dark and the project seemed endless.

## **TABLE OF CONTENTS**

| LIST  | OF ABBREVIATIONS                                   | 7    |

|-------|----------------------------------------------------|------|

| LIST  | OF FIGURES                                         | 8    |

| LIST  | OF TABLES                                          | . 11 |

| ABST  | TRACT                                              | . 13 |

| RESU  | J <b>MO</b>                                        | . 13 |

| 1     | INTRODUCTION                                       | . 15 |

| 1.1   | Proposal of this Thesis                            | . 20 |

| 2     | LOGIC SYNTHESIS AND SWITCH NETWORKS                | . 22 |

| 2.1   | Basic Concepts and Terminology                     | . 22 |

| 2.2   | A Brief History of Switching Network               | . 32 |

| 2.3   | Logic Switches                                     | . 33 |

| 2.4   | Network Generation                                 | . 38 |

| 2.5   | Network Optimization                               | . 42 |

| 2.5.1 | Factorization Through Functional Composition       | . 45 |

| 2.5.2 | BDD Network Optimization through Unateness (OpBDD) | . 48 |

| 2.5.3 | Lower Bound BDD Network (LBBDD)                    | . 51 |

| 2.6   | Network Ordering                                   | . 55 |

| 2.7   | Conclusions                                        | . 57 |

| 3     | CMOS LOGIC STYLES                                  | . 58 |

| 3.1   | Logic Styles                                       | . 58 |

| 3.1.1 | Complementary Series-Parallel CMOS (CSP) Network          | 59 |

|-------|-----------------------------------------------------------|----|

| 3.1.2 | Gates with Minimum Transistor Chains (NCSP)               | 61 |

| 3.1.3 | Mux-Based Network                                         | 61 |

| 3.1.4 | BDD-based Networks                                        | 64 |

| 3.2   | Classification of Two Terminal Disjoint Networks          | 65 |

| 3.3   | MOS Transistor as a Non-ideal Switch                      | 67 |

| 3.4   | Transistor Sizing                                         | 70 |

| 3.4.1 | Logical Effort and Transistor Networks                    | 70 |

| 3.5   | Conclusions                                               | 71 |

| 4     | ESTIMATION OF COSTS                                       | 72 |

| 4.1   | Profile and Parameters Extraction                         | 72 |

| 4.2   | Timing Estimation                                         | 73 |

| 4.3   | Dynamic Power Estimation                                  | 75 |

| 4.4   | Static Power Estimation                                   | 78 |

| 4.4.1 | A Simple Subthreshold Leakage Estimation                  | 79 |

| 4.4.2 | Gate Leakage Estimation                                   | 81 |

| 4.4.3 | Accurate Analytical Method for Static Current Estimation  | 81 |

| 4.5   | Area Estimation                                           | 84 |

| 4.5.1 | Searching Eulerian Paths                                  | 84 |

| 4.5.2 | Gate Matching                                             | 86 |

| 4.5.3 | Width and Area Estimation                                 | 88 |

| 4.5.4 | Validating Area Estimation                                | 89 |

| 4.6   | Conclusions                                               | 90 |

| 5     | EXPERIMENTAL RESULTS                                      | 91 |

| 5.1   | Results for Genlib 44-6 up to 4-input                     | 92 |

| 5.2   | Results for Additional Logic Cells of a Library Container | 95 |

| 5.2.1 | XOR Logic Functions                                       | 96 |

| 5.2.2 | Cout Function of a Full Adder                                                                |

|-------|----------------------------------------------------------------------------------------------|

| 5.3   | Results for NPN-class Logic Functions up to 5-input                                          |

| 5.4   | Results for Logic Functions Unfeasible in CSP 102                                            |

| 5.5   | Branch-based vs. Factorized Functions103                                                     |

| 5.6   | Fanin and Other Characteristics of P-class Functions up to 4 Inputs 106                      |

| 5.7   | Final Considerations 107                                                                     |

| 6     | CONCLUSIONS AND FUTURE WORKS 108                                                             |

| REFE  | CRENCES 110                                                                                  |

| APPE  | NDIX A AN ACADEMIC LIBRARY DESCRIPTION 117                                                   |

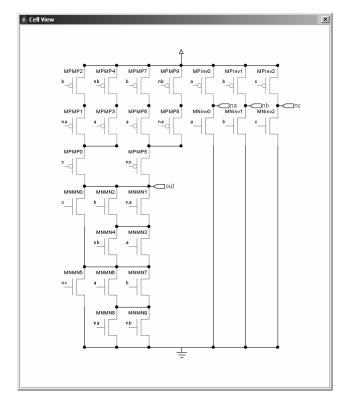

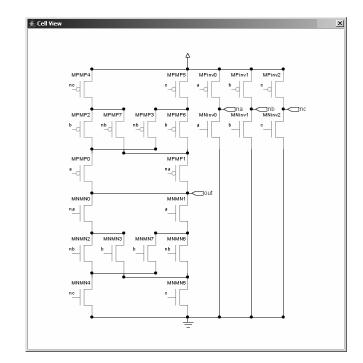

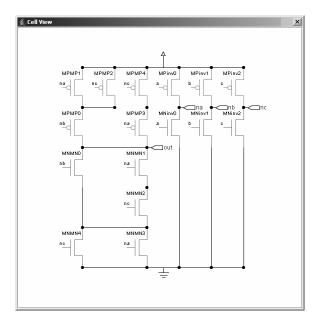

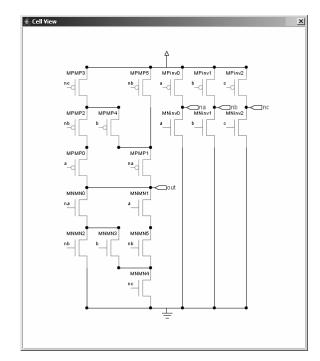

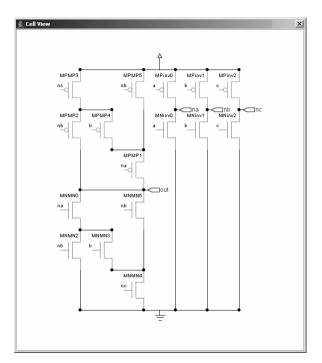

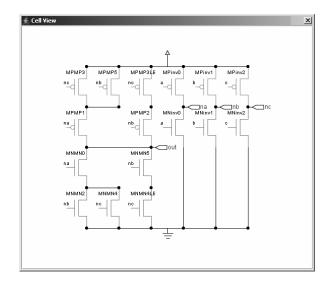

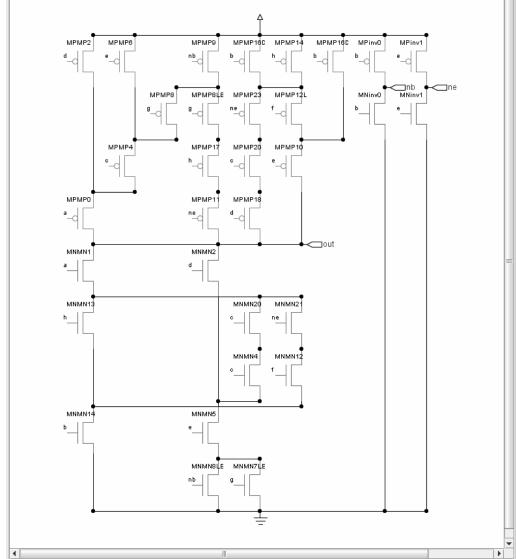

| APPE  | NDIX B XOR TRANSISTOR SCHEMATICS 119                                                         |

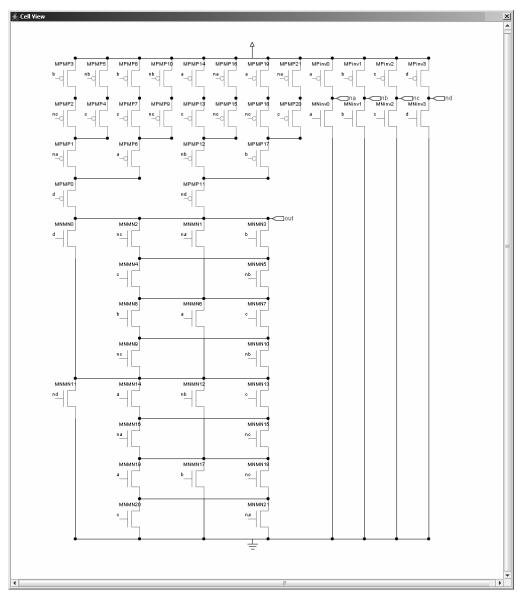

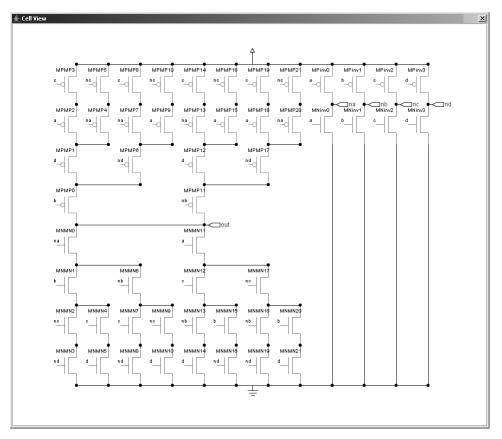

| APPE  | NDIX C COUT_FA TRANSISTOR SCHEMATICS 124                                                     |

|       | NDIX D LOGIC FUNCTIONS USED FOR THE EXPERIMENTAL                                             |

| APPE  | NDIX E DEVELOPED TOOLS 131                                                                   |

| APPE  | NDIX F LIST OF PUBLICATIONS                                                                  |

|       | NDIX G GERAÇÃO AUTOMÁTICA E AVALIAÇÃO DE REDES DE<br>NSISTORES EM DIFERENTES ESTILOS LÓGICOS |

## LIST OF ABBREVIATIONS

| ASIC   | Application-Specific Integrated Circuits          |

|--------|---------------------------------------------------|

| BDD    | Binary Decision Diagram                           |

| CAD    | Computer Aided Design                             |

| CMOS   | Complementary Metal Oxide Semiconductor           |

| CSP    | Complementary Series-Parallel                     |

| CUDD   | Colorado University Decision Diagram              |

| FPGA   | Field-Programmable Gate-Arrays                    |

| IC     | Integrated Circuit                                |

| LBBDD  | Lower Bound Binary Decision Diagram               |

| LO     | Larger Order                                      |

| MOS    | Metal Oxide Semiconductor                         |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| NCSP   | Non-Complementary Series-Parallel                 |

| NO     | Not Smaller and Larger Order                      |

| OpBDD  | Optimized Binary Decision Diagram                 |

| POS    | Product-Of-Sums                                   |

| PTL    | Pass Transistor Logic                             |

| PTM    | Predictive Technology Model                       |

| ROBDD  | Reduced and Ordered Binary Decision Diagram       |

| SO     | Smaller Order                                     |

| SoC    | System-On-Chip                                    |

| SOP    | Sum-Of-Products                                   |

| SP-BDD | Series-Parallel Binary Decision Diagram           |

| TBDD   | Terminal Suppressed Binary Decision Diagram       |

| TM-BDD | Transistor Mapped Binary Decision Diagram         |

| UFRGS  | Universidade Federal do Rio Grande do Sul         |

| ULSI   | Ultra Large Scale Integration                     |

| VLSI   | Very Large Scale Integration                      |

|        |                                                   |

## LIST OF FIGURES

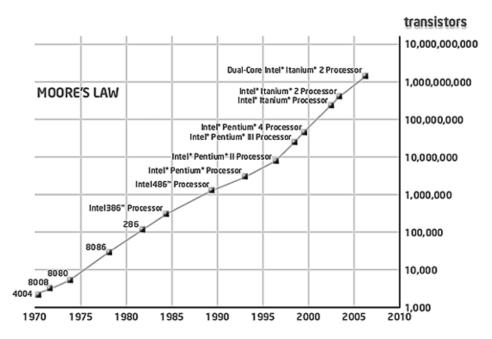

| Figure 1.1: Moore's Law graph showing the exponential increase in the number of transistors along the last three decades for the microprocessors family from Intel |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

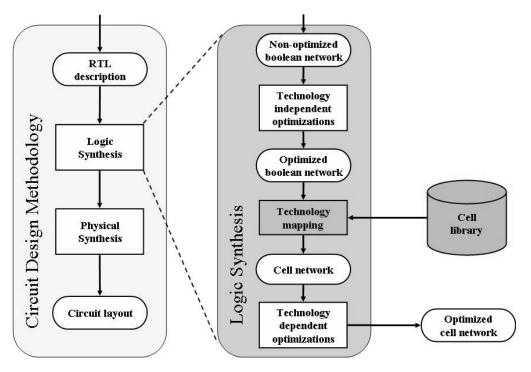

| Figure 1.2: Digital circuit design methodology using predefined cell library                                                                                       |

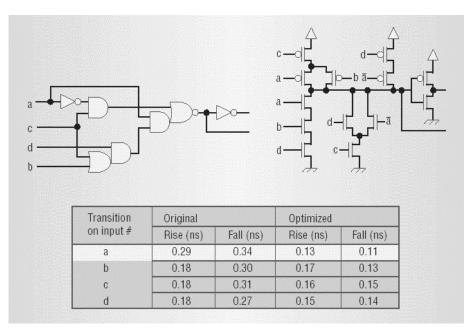

| Figure 1.3: Circuit optimization using complex gates                                                                                                               |

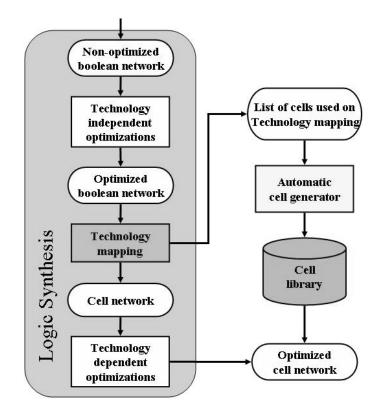

| Figure 1.4: Digital circuit design methodology using virtual library                                                                                               |

| Figure 2.1: Karnaugh map illustration                                                                                                                              |

| Figure 2.2: BDD of 3-input AND function                                                                                                                            |

| Figure 2.3: BDD reduction: (a) eliminating nodes whose two children are isomorphic<br>and (b) merging isomorphic sub-graphs                                        |

| Figure 2.4: Different variable ordering ROBDDs representing a same logic function 31                                                                               |

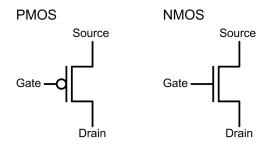

| Figure 2.5: Symbolic notation for PMOS and NMOS transistors                                                                                                        |

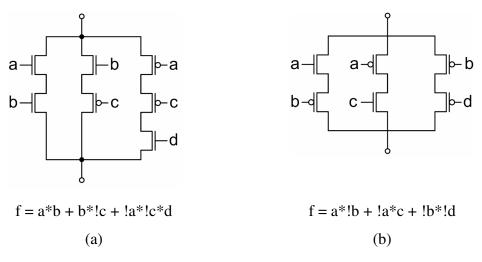

| Figure 2.6: Two logic networks representing arbitrary logic functions                                                                                              |

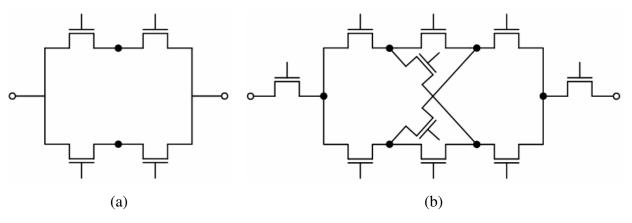

| Figure 2.7: (a) Planar network, (b) non-planar network                                                                                                             |

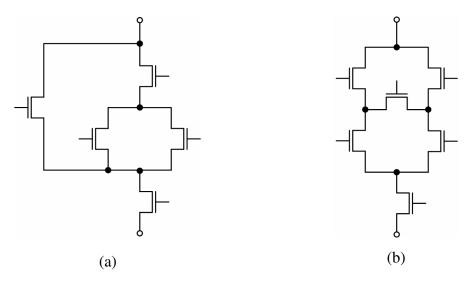

| Figure 2.8: (a) Series-parallel network, (b) bridge network                                                                                                        |

| Figure 2.9: (b) Dual networks obtained through (a) dual graphs                                                                                                     |

| Figure 2.10: Branch-based network                                                                                                                                  |

| Figure 2.11: (a) Single-rail network, (b) dual-rail network                                                                                                        |

| Figure 2.12: (a) Disjoint planes, (b) non-disjoint planes                                                                                                          |

| Figure 2.13: (a) Network derived from the on-set and its dual network, (b) network derived from the off-set and its dual implementation                            |

| Figure 2.14: Logically complementary networks obtained from the on-set and the off-set equations                                                                   |

| Figure 2.15: BDD node and associated switches                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.16: Networks derived from a BDD 41                                                                                        |

| Figure 2.17: Bridge network implementation 42                                                                                      |

| Figure 2.18: Karnaugh map for the Boolean function f                                                                               |

| Figure 2.19: Multilevel representations                                                                                            |

| Figure 2.20: Factorization through composition                                                                                     |

| Figure 2.21: Network derived from a BDD 48                                                                                         |

| Figure 2.22: Switches controlled by variable <i>a</i> are used to choose between cofactors <i>f0</i> and <i>f1</i>                 |

| Figure 2.23: BDD and derived switch network                                                                                        |

| Figure 2.24: Duplication strategies for a switch network                                                                           |

| Figure 2.25: BDD and optimized switch network                                                                                      |

| Figure 2.26: Two BDDs and their derived transistor networks                                                                        |

| Figure 3.1: Logic styles: (a) Static CMOS, (b) PTL using only NMOS transistors, (c) PTL using transmission gates                   |

| Figure 3.2: NMOS logic rules: (a) series devices produce an AND operation, (b) parallel devices produce an OR one                  |

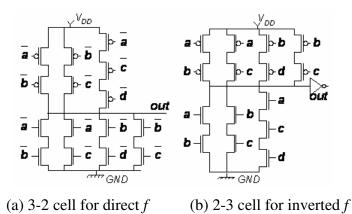

| Figure 3.3: NCSP implementation for equations (3.1) and (3.2)                                                                      |

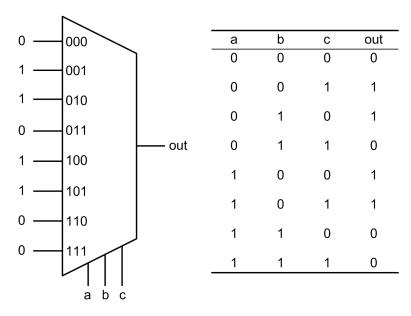

| Figure 3.4: Mux_8x1 implementing a logic function                                                                                  |

| Figure 3.5: Mux_4x1: (a) generic symbol, (b) implementing function from Figure 3.4 63                                              |

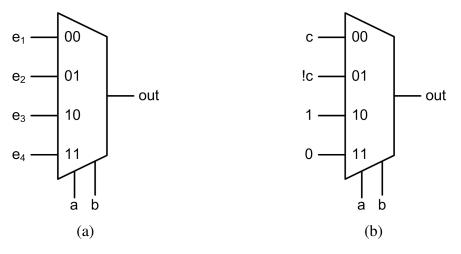

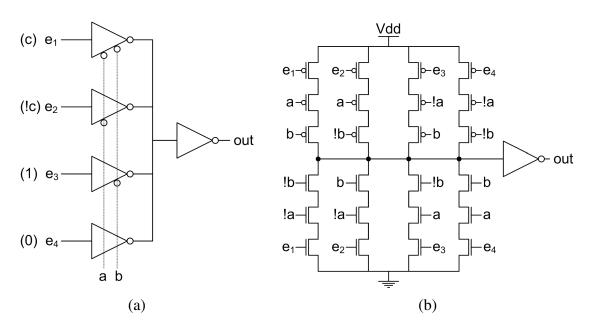

| Figure 3.6: (a) Mux using tri-state inverters, (b) mux_4x1 transistor network                                                      |

| Figure 3.7: Optimized mux_4x1 transistor network                                                                                   |

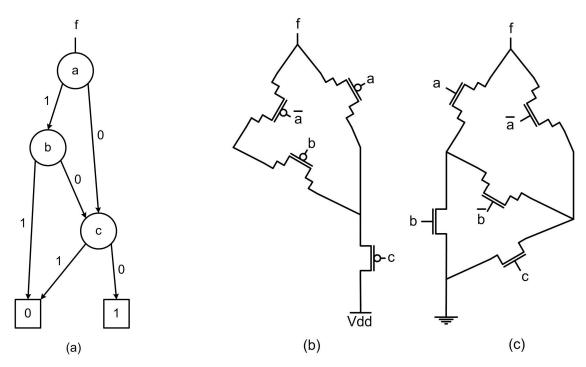

| Figure 3.8: (a) BDD representation, (b) pull-up network and (c) pull-down network derived from it                                  |

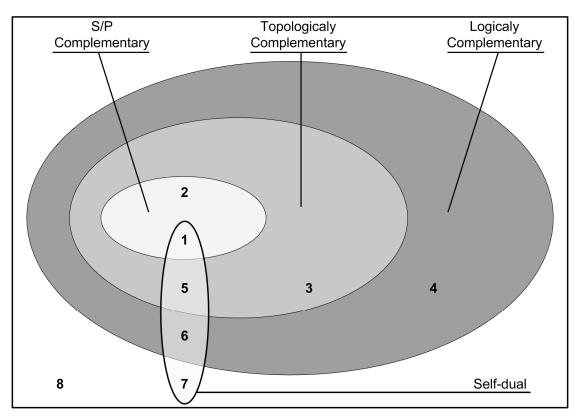

| Figure 3.9: Classification of two terminal disjoint networks                                                                       |

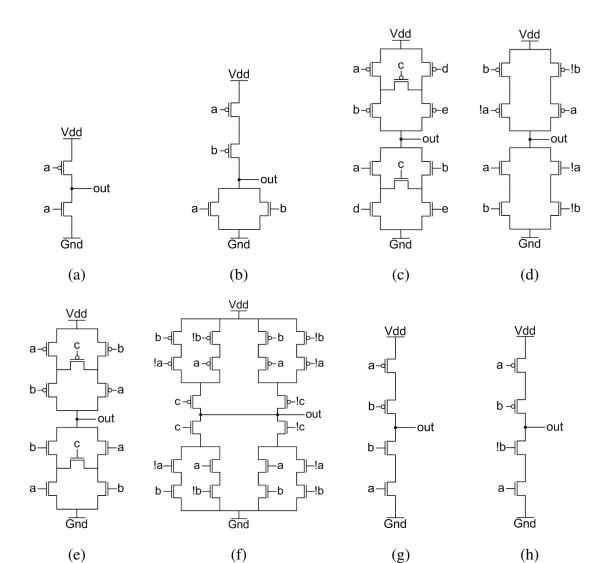

| Figure 3.10: Networks from: (a) group 1, (b) group 2, (c) group 3, (d) group 4, (e) group 5, (f) group 6, (g) group 7, (h) group 8 |

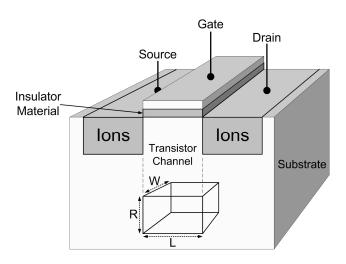

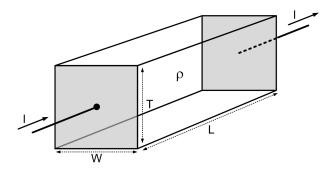

| Figure 3.11: MOS transistor structure                                                                                              |

| Figure 3.12: MOS transistor channel dimensions 69                                                                                  |

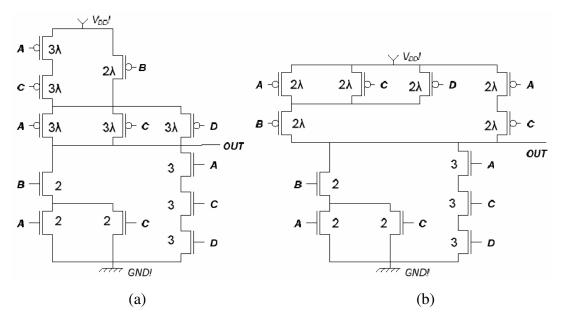

| Figure 3.13: Two circuits for the same logic function                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

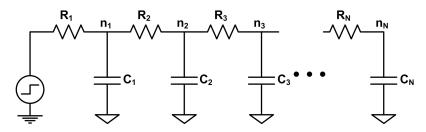

| Figure 4.1: RC ladder for Elmore delay 74                                                                                                                     |

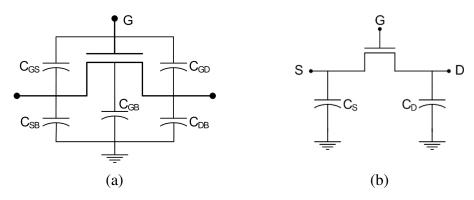

| Figure 4.2: Capacitance model: (a) MOSFET and (b) simplified approach                                                                                         |

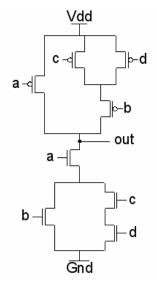

| Figure 4.3: Complex gate77                                                                                                                                    |

| Figure 4.4: Hspice vs. estimated power consumption                                                                                                            |

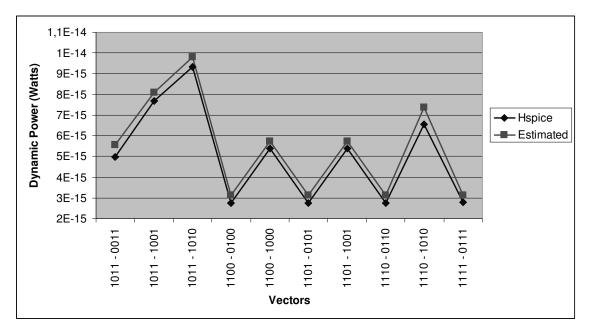

| Figure 4.5: (b) Equivalent conductance for the transistor network described in (a) 79                                                                         |

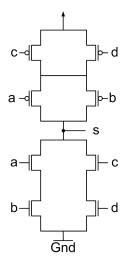

| Figure 4.6: A 4-input transistor network                                                                                                                      |

| Figure 4.7: Subthreshold leakage currents in the CMOS structure from Figure 4.6, for each input vector                                                        |

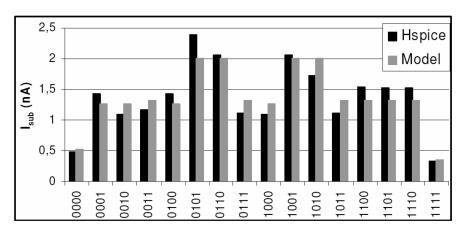

| Figure 4.8: Possible bias condition for NMOS transistors in digital circuits                                                                                  |

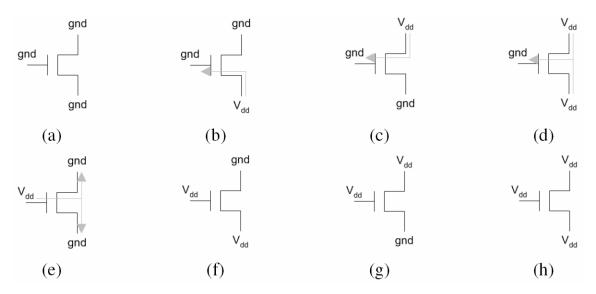

| Figure 4.9: Total leakage estimation comparison for different CMOS gates                                                                                      |

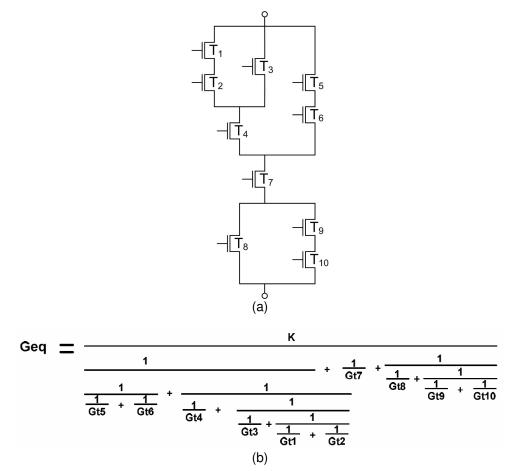

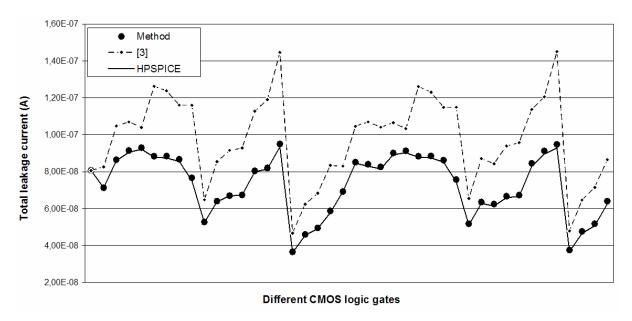

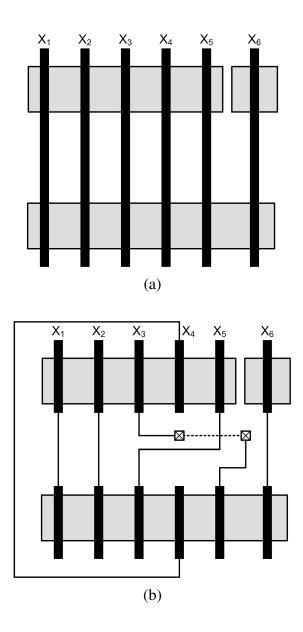

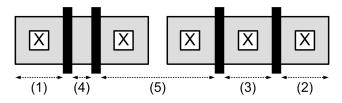

| Figure 4.10: (a) PMOS transistor network and (b) NMOS transistor network showing possible Eulerian paths                                                      |

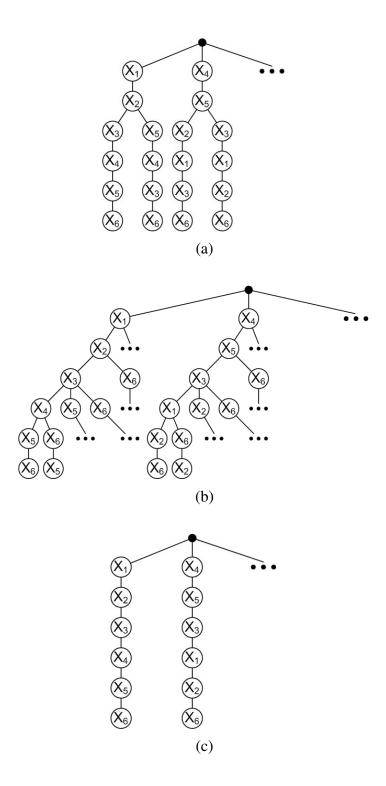

| Figure 4.11: Partial tree for the cell in Figure 4.10, before (a, b) and after (c) the gate matching algorithm                                                |

| Figure 4.12: Two possible symbolic layouts for the cell in Figure 4.10, showing matched (a) and mismatched gates (b)                                          |

| Figure 4.13: Relevant distances extracted from technology process documentation 89                                                                            |

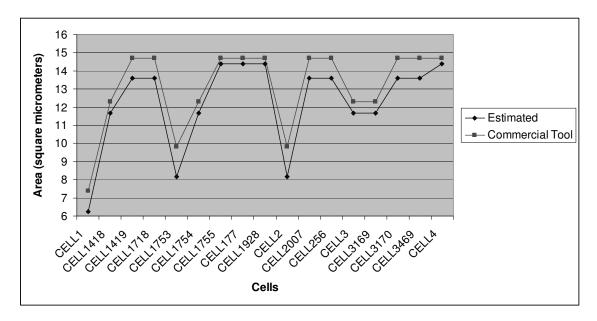

| Figure 4.14: Results for the validation of the area estimation                                                                                                |

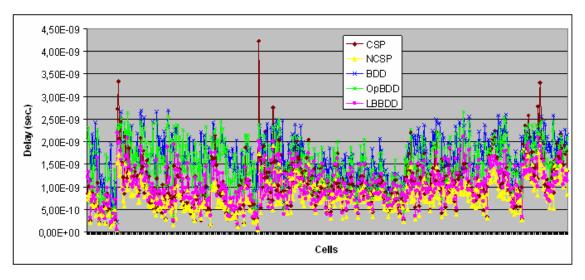

| Figure 5.1: Delay results for 500 cells from NPN-class up to 5-input                                                                                          |

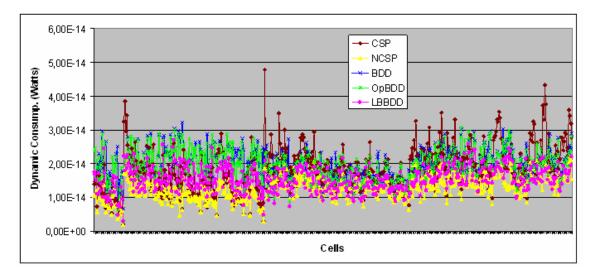

| Figure 5.2: Dynamic consumption results for 500 cells from NPN-class up to 5-input 99                                                                         |

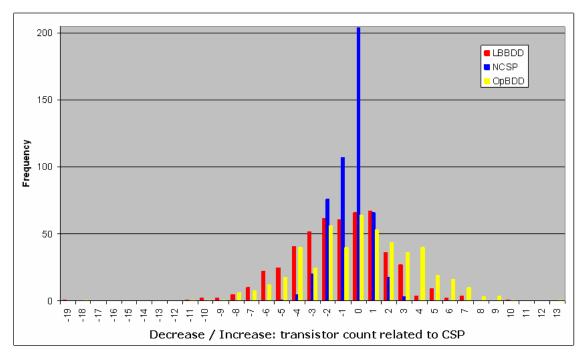

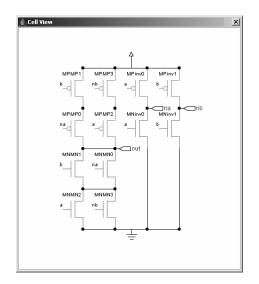

| Figure 5.3: Increase and decrease in transistor count when comparing to CSP 100                                                                               |

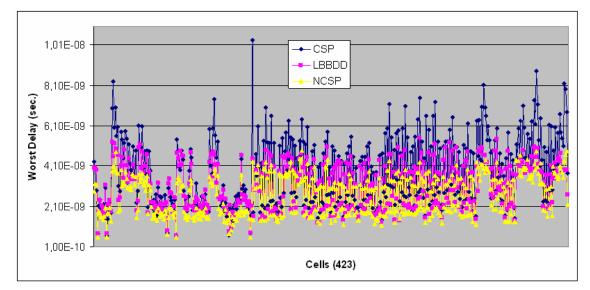

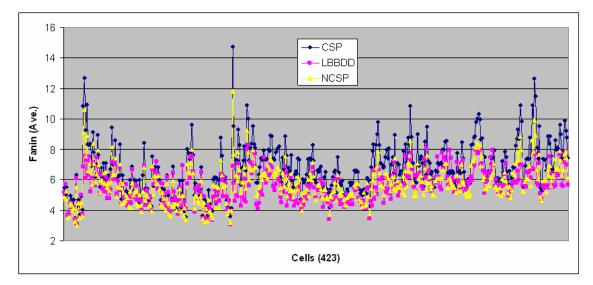

| Figure 5.4: Worst delay for 423 cells that do not respect the minimum number of transistors in series when implemented in CSP                                 |

| Figure 5.5: Average fanin for 423 cells that do not respect the minimum number of transistors in series when implemented in CSP 101                           |

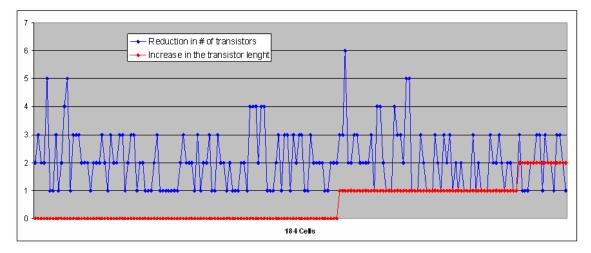

| Figure 5.6: Experiment showing the reduction in transistor count and the increase in the transistor length when mixing LBBDD and Dual network generations 101 |

## LIST OF TABLES

| Table 2.1: Truth table for the 2-input basic functions.    24                                         |

|-------------------------------------------------------------------------------------------------------|

| Table 2.2: Relation between minterms and lines of the truth table.    25                              |

| Table 2.3: Relation between maxterms and lines of the truth table.    26                              |

| Table 2.4: Covering table for function <i>f</i> .    27                                               |

| Table 2.5: Two P-class equivalent functions.    28                                                    |

| Table 2.6: Four N(in)-class equivalent functions.    28                                               |

| Table 2.7: Two equivalent functions after output inversion                                            |

| Table 2.8: Truth table for function $f$ , individualized by pull-up and pull-down planes. 49          |

| Table 2.9: Truth table for function $f$ and pull-up PU( $f$ ) as a function of $a$ , $f0$ and $f1$ 50 |

| Table 2.10: Transistor edge candidate to become a short-circuit.    50                                |

| Table 3.1: Logical effort values for circuits in Figure 3.13                                          |

| Table 4.1: Intrinsic capacitances modeling.    76                                                     |

| Table 4.2: Distances used to validate the area estimation.    90                                      |

| Table 5.1: Average delay results (in seconds) for Genlib 44-6 up to 4-input                           |

| Table 5.2: Average power consumption (in Watts) for Genlib 44-6 up to 4-input 94                      |

| Table 5.3: Average leakage current (in Amperes) for Genlib 44-6 up to 4-input                         |

| Table 5.4: Area results (in square microm.) obtained for Genlib 44-6 up to 4-input 95                 |

| Table 5.5: Transistor count for XOR logic functions                                                   |

| Table 5.6: Transistor in series for XOR logic functions.    96                                        |

| Table 5.7: Average delay (in seconds) for XOR logic functions.    97                                  |

| Table 5.8: Dynamic consumption (in Watts) for XOR logic functions                                     |

| Table 5.9: Leakage current (in Amperes) for XOR logic functions                                     |

|-----------------------------------------------------------------------------------------------------|

| Table 5.10: Area results (in square micrometers) for XOR logic functions                            |

| Table 5.11: Delay results (in seconds) for Cout function of a full adder.       98                  |

| Table 5.12: Dynamic consumption (in Watts) for Cout function of a full adder                        |

| Table 5.13: Leakage current (in Amperes) for Cout function of a full adder                          |

| Table 5.14: Area results (in square micrometers) for Cout function of a full adder 98               |

| Table 5.15: Number of transistor in series    102                                                   |

| Table 5.16: Delay results (in seconds)                                                              |

| Table 5.17: Power results (in Watts)    103                                                         |

| Table 5.18: Leakage current (in Amperes)                                                            |

| Table 5.19: Average delay results (in seconds) for fact. and non-factorized forms 104               |

| Table 5.20: Power consumption (in Watts) for factorized and non-factorized forms. 104               |

| Table 5.21: Leakage current (in Amperes) for factorized and non-factorized forms 105                |

| Table 5.22: Area (in micrometers) for factorized and non-factorized forms.       105                |

| Table 5.23: Comparison of different methods for P-class logic functions up to 4 variables.      107 |

#### ABSTRACT

Currently, VLSI design has established a dominant role in the electronics industry. Automated tools have enabled designers to manipulate more transistors on a design project and shorten the design cycle. In particular, logic synthesis tools have contributed significantly to reduce the design cycle time. In full-custom designs, manual generation of transistor netlists for each functional block is performed, but this is an extremely time-consuming task. In this sense, it becomes comfortable to have efficient algorithms to derive transistor networks automatically. There are several kinds of transistor networks arrangements. These different networks present different behaviors in terms of area, delay and power consumption. Thus, not only automatic transistor networks generation is important, but also an automated technique to evaluate and to compare the distinct switch networks is fundamental to guide designers that need to achieve efficient circuit implementations. This evaluation not necessarily needs to be an expensive electrical characterization process. It can be obtained through estimation processes capable of delivering good information about the logic cells behavior. This idea is useful for those designers that desire to generate and to evaluate potential transistor network implementations to feed standard-cell flow designs (using cell libraries), or for those designers who target the use of library-free technology mapping concept (using automatic cells generators). In this context, this work presents an automated transistor network generator able to delivery different kinds of networks in several logic styles. In order to compare the obtained networks, some estimation techniques are employed. A comparison is done over a set of Boolean function benchmarks, showing the advantages of using alternative logic styles over the traditional Complementary Series-Parallel CMOS (CSP CMOS).

**Keywords:** Transistor Networks, Logic Cells, Technology Mapping, Switch Theory, CMOS Logic Styles.

#### **RESUMO**

O projeto e o desenvolvimento de circuitos integrados é um dos mais importantes e aquecidos segmentos da indústria eletrônica da atualidade. Neste cenário, ferramentas de automação têm possibilitado aos projetistas manipular uma elevada quantidade de transistores em circuitos cada vez mais complexos, diminuindo, assim, o tempo de projeto. Em especial, ferramentas de síntese lógica têm contribuído significativamente para reduzir o ciclo de desenvolvimento. Na metodologia de projeto full-custom, cada bloco funcional tem sua geração realizada de forma manual, desde a implementação das redes de transistores até a geração do leiaute. Entretanto, esta tarefa é extremamente custosa em tempo de projeto. Neste contexto, torna-se confortável ter a disposição algoritmos dedicados para derivar redes de transistores automaticamente. Diversos tipos de arranjos de transistores são encontrados na literatura. Estas diferentes redes de transistores apresentam diferentes comportamentos em termos de consumo de área, consumo de potência e velocidade. Desta forma, não apenas a geração automática de redes de transistores é importante, mas também técnicas automatizadas para avaliar e comparar estas distintas redes de chaves é de fundamental importância para guiar o projetista que deseja alcançar implementações de circuitos eficientes. Estas avaliações não precisam ser necessariamente processos custosos de caracterização elétrica. Elas podem ser realizadas através de estimativas capazes de fornecer informações acuradas sobre o comportamento das redes. Esta idéia pode ser utilizada por projetistas que desejam gerar e avaliar potenciais soluções em redes de transistores para alimentar fluxos standard-cell (utilizando bibliotecas de células), ou por aqueles que utilizam a abordagem de mapeamento tecnológico library-free (fazendo uso de geradores de células). Neste contexto, este trabalho apresenta um gerador automático de redes de transistores capaz de fornecer diferentes tipos de redes em diversos estilos lógicos. Para comparar as redes geradas, algumas técnicas de estimativa são empregadas. Comparações são realizadas sobre conjuntos distintos de funções Booleanas, demonstrando as vantagens da utilização de lógicas alternativas em relação ao difundido padrão CMOS.

**Palavras-chave:** Redes de Transistores, Células Lógicas, Mapeamento Tecnológico, Teoria de Chaves, Estilos Lógicos CMOS.

### **1 INTRODUCTION**

Microelectronics became the key technology of many industry branches like information technology, telecommunication, medical equipment and consumer electronics. The ability of microelectronics to process, transport and store data digitally made many new applications possible. The continuously increasing level of integration of electronic devices on a single substrate has led to the fabrication of increasingly complex systems. An **Integrated Circuit** (IC) is an electronic system consisting of a number of miniaturized electronic devices, such as transistors, resistors, capacitors and inductors, built on a monolithic semiconductor substrate. The large majority of the current ICs are implemented in the Metal-Oxide-Semiconductor (MOS) technology (WESTE, 2005; RABAEY, 2003).

The IC design can be divided into two broad categories: analog and digital design. **Analog design** is used in the development of operational amplifiers, linear regulators, phase-locked loops, oscillators and active filters. Analog design is more concerned with the physics of the semiconductor devices such as gain, matching, power dissipation, and resistance. Fidelity of analog signal amplification and filtering is usually critical and as a result, analog ICs use larger area active devices than digital designs and are usually less dense in circuitry. In the other hand, **digital IC design** is used to produce components such as microprocessors, FPGAs (Field-Programmable Gate-Arrays), memories and digital ASICs (Application-Specific Integrated Circuits). Digital design focuses on logical correctness, maximizing circuit density, and placing circuits so that clock and timing signals are routed efficiently.

Since the advent of the technology for constructing ICs, integration density and performance of these electronic systems have gone through an astounding revolution driven by the ability of integrating in a single system more and more transistors, the devices responsible by most of the complexity of digital ICs. Indeed, the increase in the number of transistors that can be integrated in a single die has grown exponentially in the last three decades, as predicted by the so called **Moore's Law** (INTEL, 2007; MOORE, 1965). Figure 1.1 illustrates how this increase prediction has been proved correct so far. Although it has been frequently stated that such increase might cease in a few years due to physical limitations of IC manufacturing technologies, new design

methodologies and fabrication process breakthroughs have proven that such cease can be postponed (MOORE, 2003).

Figure 1.1: Moore's Law graph showing the exponential increase in the number of transistors along the last three decades for the microprocessors family from Intel (INTEL, 2007).

Essentially, there are two main flows when designing digital ICs that lead to two contrasting situations: fast design and high-performance design. Fast design here means short time-to-market; for this kind of approach for IC design, a **standard-cell design methodology** is the most commonly used approach. On the other hand, design for high-performance uses a **full-custom design methodology**, as this kind of design is completely customized to the high performance in terms of area, speed and power consumption (DEMICHELI, 1994).

In full-custom design the logic and physical synthesis attain usually the highest performance and smallest size, making use of the most advanced technologies (CHEN, 2000). It is the most technology dependent design approach, since each switch element present in every cell is manually fine-tuned in order to explore all the performance advantages that a given technology can deliver. The benefits of full-custom design in general include reduced area, performance improvements and also the ability to integrate analog components and other pre-designed components such as microprocessor cores that form a System-on-Chip (SoC). The disadvantages of fullcustom can include increased manufacturing and design time, and much higher skill requirements on the part of the design team.

The proposal of standard-cell design is to reduce the implementation effort by reusing a library of cells. The advantage of this approach is that the cells only need to be

designed and verified once for a given technology, and they can be reused many times, thus amortizing the design cost. The disadvantage is that the constrained nature of the library, especially due to the limited number of cells, reduces the possibility of fine-tuning the design (RABAEY, 2005). According to Scott (1994), the quality of a synthesized design based on standard-cells depends on three main components: (a) the synthesis tool, (b) the place and route tools, and (c) the target cell library. Choosing the right cell library may have a significant impact on the characteristics of a circuit (VUJKOVIC, 2002; SECHEN, 2003).

**Cell library** is a finite set of logic cells that implements different Boolean functions with different drive strengths and topologies. Traditionally, the technology mapping methods rely on static pre-characterized libraries aiming delay, area and power optimizations. Each cell in the library is fully characterized through many simulations, resulting in a set of accurate information about the behavior of the cell. According to Sechen (2003), the design and characterization costs of a library are expensive. Therefore, commercial libraries are typically composed of few hundred combinational cells and sequential elements (latches and flip-flops) for which layouts have been optimized for a particular technology. As a result, designers are restricted to use these cells in their circuits. An example of a well-known and widely used academic library is presented in Appendix A.

**Technology mapping** is the procedure of expressing a given Boolean network in terms of logic cells or gates. Typically, the objective function aims the optimal use of all gates in the library to implement a circuit with critical-path delay less than a target value and minimum area. The most existing techniques for technology mapping are based on pre-characterized cell libraries (KEUTZER, 1987; KUKIMOTO, 1998; STOK, 1999; MISCHENKO, 2005). These techniques are also known as **library-based methodology**. Ideally, technology mapping algorithms and tools should be able to satisfy several goals and to handle different libraries. It is a quite hard task since the cell libraries normally have a different set of cells that implements a limited set of logic functions. A library of fixed size restricts the choices for covering a given circuit. Figure 1.2 shows the typical design flow considering technology mapping methodologies based on libraries with a fixed size.

Some works in the literature try to optimize logic cells on specific circuits and implementations. Typical optimizations have been limited to the design of buffers and inverter chains, implemented to minimize power consumption (MA, 1994) and delay (VEMURA, 1991; PRUNTY, 1992). Other ones try to optimize logic cells from existing cell libraries in order to adjust them to the circuit requirements (FISHER, 1996). Recent researches advocate that transistor-level optimizations are a powerful technique to improve the circuit performance (PANDA, 1998; BHATTACHARYA, 2002; YOSHIDA, 2006). In Roy (2005) some parts of the circuit are removed and replaced by optimized cells to attain the technical specification. This replacement is done as a post-processing step, after the circuit has been defined by two types of cells, mapping task. In this strategy, the final circuit is composed by two types of cells,

derived from commercial library container and handcrafted complex gates. Figure 1.3 illustrates this idea, indicating a considerable propagation delay gain for the circuit.

Figure 1.2: Digital circuit design methodology using predefined cell library (MARQUES, 2007).

Figure 1.3: Circuit optimization using complex gates (ROY, 2005).

Usually, cell libraries are composed of a few tens of logic cells, due to the engineering effort to design and characterize each one. These cells have been previously

tested and validated, and all information about their behavior is described in a database which, in turn, is used during the technology mapping procedure.

Some researchers have observed that large cell libraries could lead to a better circuit implementation (VUJKOVIC, 2002). However, the number of potential logic function increases exponentially with the number of inputs. Therefore, it is not possible to characterize and implement all existing functions in a huge library. The processes of electrical characterization and layout generation are extremely computing demand, making the possibility of having large cell libraries unfeasible (SECHEN, 1996).

Other approaches for technology mapping propose techniques based on automatic cell generators. These approaches are known as **library-free** (BERKELAAR, 1988; REIS, 1998; STOK, 1999; JIANG, 2001; CORREIA, 2004; MARQUES, 2007). Instead of having a predefined static library, they assume that arbitrary cells can be generated on-the-fly through a cell generator, increasing the matching search space. The mapping algorithm defines the set of cells required in the circuit implementation, and this **virtual library** is used as input for a cell generator which provides the logic cell layouts that are further used in the physical synthesis. Figure 1.4 illustrates the logic synthesis flow of this approach.

Figure 1.4: Digital circuit design methodology using virtual library (MARQUES, 2007).

Notice that, the quality of mapped circuits is highly dependent on the richness of the library in terms of the number of implemented logic functions, drive strengths and topologies. Libraries that implements a large number of Boolean functions leads to better results when compared to sparsely populated libraries. In Keutzer (1987) the impact of a library size was investigated. In this work it was demonstrated that a better area optimization can be achieved using large libraries. As Jiang (2001) has observed, the most recent device technologies encourage the usage of complex gates in deepsubmicron circuits. It leads to better circuit performance. But, the main barrier for virtual library approach is the dependency of a good layout generator and the lack of accurate information about the cell behavior. Due to this, static pre-characterized libraries are still popular in the industry. This work addresses two problems associated with this flow. The first one is to find good quality transistor networks to implement the cells in the library. The second one is to use fast models to estimate cell area, timing and power on-the-fly.

#### **1.1 Proposal of this Thesis**

According to the previously statements, this work addresses the digital cell implementation and optimization at the transistor cell level. It is known that different logic styles result in transistor networks with different electrical and physical behavior. Although several transistor network styles are available, the standard-cell industry keeps using the standard CMOS. The library-free approach is a promising solution, but it presents the disadvantage of lacking the characterization information. The characterization process is expensive in terms of CPU, making impracticable the use of this technique to generate and evaluate cells on-the-fly. An alternative is the use of estimation techniques. By using fast and efficient methods to obtain estimative about the logic cells behavior, it is possible to generate library cells considering these estimated information as costs, avoiding the characterization process.

The estimation approach, adopted as solution in this work, not only can be used to feed library-free technology mapping flow, but also as a method to generate information about the behavior of cells to compose library containers. Thus, it is possible to generate specific libraries composed of cells with estimated costs regarding area, timing and power. These libraries are suitable to be used in traditional standardcells design flow. The circuits can be mapped, tested and simulated. Once they meet the design constraints, them the designer can effectively implement the layout of the cells to obtain the final circuit. Commercial layout generators are available in the market, like the Nangate Library Creator, which accepts Spice netlist description as input to automatically generate the cell layout (NANGATE, 2008).

In this sense, this thesis proposes an automated flow for generating transistor cell networks in different logic styles and a technique to obtain information about the behavior of these cells through estimation methods. Furthermore, scientific contributions of this thesis are also:

- A new BDD-based transistor network logic style that respects the minimum number of switches in series to implement a given logic function;

- A factorization algorithm to optimize logic expressions and electrical networks;

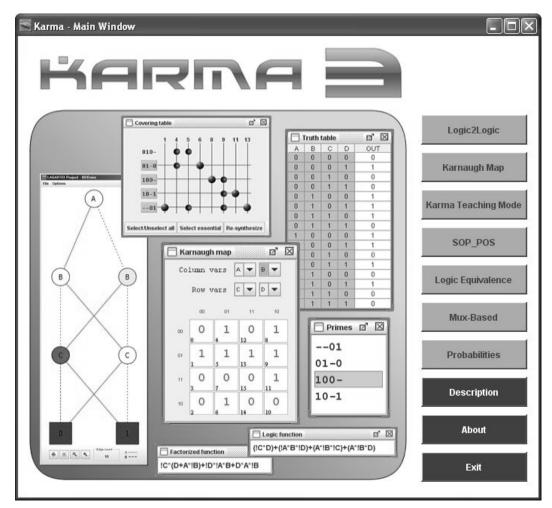

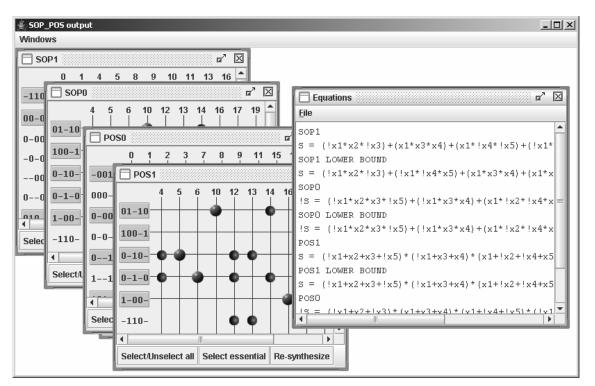

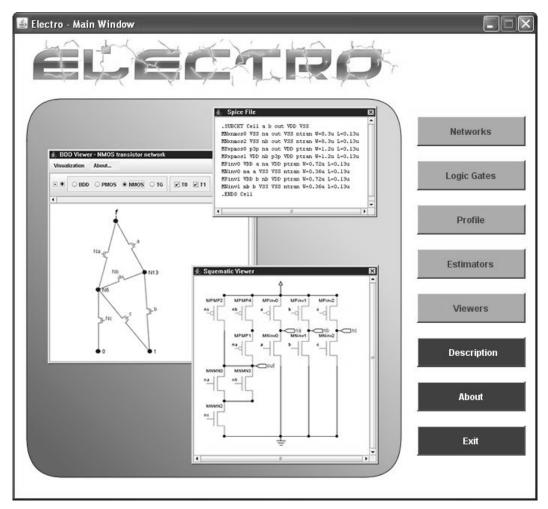

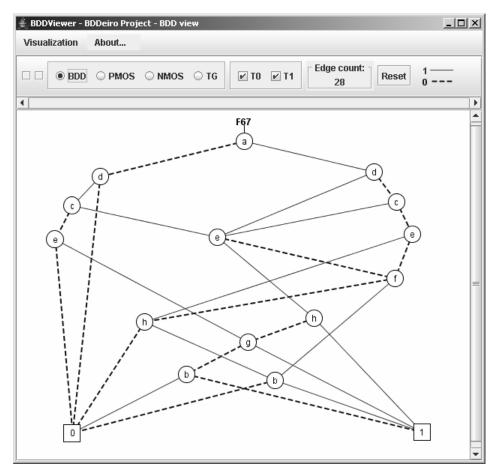

- CAD tools for logic synthesis of Boolean functions, as well as for automatic generation and evaluation of transistor networks.

### **2** LOGIC SYNTHESIS AND SWITCH NETWORKS

Integrated circuits design presents a set of concepts and terminologies very specific and necessary for the understanding of the field. More specifically, logic synthesis definitions must be reviewed in order to permit the whole understanding of this work. The goal of this chapter is to present the conceptual framework on top of which work is built. This chapter is organized as follows. Firstly, this chapter introduces these concepts that will be used in following chapters. Secondly, this chapter presents a brief discussion about the history of switch theory and about logic switches. Finally, it discusses possible optimizations performed at the logic level, presenting a factorization method to achieve minimum literal Boolean expressions and a new kind of transistor network derived from BDD. For the following chapters, it is assumed that the reader has the knowledge of definitions described herein.

#### 2.1 Basic Concepts and Terminology

The **Boolean set** *B* is defined as a two element set,  $B = \{0, 1\}$ , whose elements are interpreted as **logic values**, typically '0' = false and '1' = true. An n-dimensional Boolean set  $B^n$  is composed of all the distinct Boolean vectors of length 'n'. For instance  $B^0 = \{\mathcal{O}\}$ ,  $B^1 = B = \{0, 1\}$ ,  $B^2 = \{00, 01, 10, 11\}$  and  $B3 = \{000, 001, 010, 011, 100, 101, 110, 111\}$ . It is easy to observe that  $B^n$  has  $2^n$  elements. A **Boolean function** describes how to determine a Boolean value output based on some logic calculation from Boolean input vectors of length 'n'. A **Boolean function** is a function of the form  $f: B^n \to B$ , where  $B = \{0, 1\}$  is the Boolean domain and where 'n' is a non-negative integer. A Boolean function  $f: B^n \to B$  can be viewed as a function whose domain is composed of the set of all n-bit Boolean vectors (that means  $B^n$ , which contains  $2^n$ elements) and whose image is composed of unidimensional Boolean vectors (i.e.  $B^1=B$ , which contains two elements). So every distinct n-input Boolean vector of  $B^n$  can point to a distinct one dimensional Boolean vector. This way, a function  $f: B^n \to B$  has  $2^n$ input positions pointing to a fixed value from *B*. As changing the value pointed by a single input vector changes the logic function, there are  $2^{2^n}$  such functions, as the output has  $2^n$  positions that can be associated to two distinct values from *B*. In the case where n = 0, the function is simply a constant element of *B*. Boolean functions are also called **logic functions**.

**Boolean variables** are variables defined in the Boolean domain and generally assigned using alphanumeric characters. Examples of Boolean variables are: a, b, c, x0, x1, y2; if they are defined over the Boolean set. Boolean variable can assume arbitrary values in the Boolean domain B, i.e. Boolean variables can assume the values '0' or '1'.

There are three basic **Boolean operators**: *AND* ("\*"), *OR* ("+") and *NOT* ("!"), which can be applied to Boolean values or functions. *AND* operator returns one (or true) when all the operands are true and returns false for the other cases. *OR* operator returns zero (or false) when all the operands are false and returns true otherwise. *AND* and *OR* operators are binary operators, as they require at least two elements to perform the operation. *NOT* operator, also called inversion or negation operator, is unary and can be applied to one element alone. *NOT* operator returns zero when the operand is one and *vice-versa*. The operands may be Boolean functions or Boolean constants.

**Phase** or **polarity** of a Boolean variable indicates if it is used in its direct or inverted form. Positive phase specifies the use of a variable without inversion, while negative phase specifies the use of its complement. A variable in its negative phase is noticed by the anteriority of a *NOT* operator ('!') as, for instance, !a, !t, etc. **Literal** is an instance of a Boolean variable in its positive or negative phase. Examples of literals are: a, !a, x0, !y2. Notice that a and x0 are positive literals, while !a and !y2 are negative literals.

**Input vector** is an element that indicates the value of each Boolean variable in a given Boolean function. For a certain number of variables there is  $2^n$  input vectors, where *n* is the total number of Boolean variables.

**Boolean expressions** or **Boolean equations** are representations of a Boolean function. Each Boolean function is distinct, as it represents just one association  $f: B_n \rightarrow B$ . However, it is possible to write a Boolean function in different forms using Boolean operators. For example, the two following Boolean equations represent the same Boolean function:

$$Eql = a * (b * c) + d * (e + c)$$

(2.1)

$$Eq2 = c * (a * b + d) + d * e$$

(2.2)

Boolean functions can also be represented in tabular form known as **truth table**. In a **truth table** representation, the output values are shown according to all possible input combinations. In other words, the truth table is a representation form where all function values are specified for all domain function. The truth table can be built for any number of input variables. However, all possible combinations for these input variables must be present. It means that each line of the truth table represents an input vector and its respective output value. Table 2.1 illustrates truth tables for basic

Boolean functions with two inputs A and B. Notice that those are functions defined as  $B^2 \rightarrow B$ ; which means that the input vectors [A,B] can assume any of the four (2<sup>2</sup>=4) values in  $B^2 = \{00, 01, 10, 11\}$ . The AND and OR operators were already defined above. The operator XOR returns '1' when an odd number of inputs are equal to '1'. The operators NAND, NOR and XNOR are the inverted versions of AND, OR and XOR, respectively.

| Α | В | AND | OR | XOR | NAND | NOR | XNOR |

|---|---|-----|----|-----|------|-----|------|

| 0 | 0 | 0   | 0  | 0   | 1    | 1   | 1    |

| 0 | 1 | 0   | 1  | 1   | 1    | 0   | 0    |

| 1 | 0 | 0   | 1  | 1   | 1    | 0   | 0    |

| 1 | 1 | 1   | 1  | 0   | 0    | 0   | 1    |

Table 2.1: Truth table for the 2-input basic functions.

For a given Boolean function, the set of input vectors that produces an output value '1' is called **on-set**. In the same way, the set of input vectors that produces an output value '0' is called **off-set**.

A product of literals is an *AND* logic operation between these literals. (a\*b\*c\*e) and (!a\*c\*!d) are examples of products. The **sum-of-products** (**SOP**) representation is the Boolean equation composed of *OR* logic operation in between two or more products. The following equations are examples of SOP:

$$Eq3 = !a * b * !c * d + a * b * !c * !d + !a * !b * c * d$$

(2.3)

$$Eq4 = x0 * !x1 * x2 + x1 * x2 * !x3 + !x0 * x1 * !x2 * x3$$

(2.4)

$$Eq5 = (a * b * c) + (!a * c * d) + (b * !c * !d)$$

(2.5)

There is a straightforward manner to derive a SOP representation from a truth table. To do that, it is only necessary to extract all lines (products), that present output values *one* in the truth table, and to implement *OR* operations between these products. Such equation is known as a Boolean equation in the **SOP canonical form**. Canonical forms have this name because they preserve a one-to-one relation with the truth table, meaning that there is only one canonical SOP per Boolean function, even if many different non-canonical equations can exist. Some of the non-canonical equations can present a reduced number of literals compared to canonical SOPs. As a consequence, a canonical SOP is not necessarily the minimal representation for most Boolean functions. The procedure of building a SOP with minimum number of literals is more elaborate, and can be done with algorithms like Quine-McCluskey (QUINE, 1955; MCCLUSKEY, 1956). It is important to notice that all variables must be present in each product to guarantee that the equation is in the canonical form. Moreover, it cannot

contain repeated products. An example of equation in canonical form is the equation (2.3).

The **product-of-sums** (**POS**) representation is very similar to the sum-ofproducts one. The difference is that the Boolean equation is composed of AND logic operation in between two or more sums of literals. Also, to build the sums, all lines that present output value '0' in the truth table are considered. Notice that, similar to SOP, all variables must be present in each sum to guarantee the POS in the canonical form. Again, a canonical POS is not necessarily the minimal representation of Boolean functions.

A product containing all variables that compose the function is called **minterm**. A minterm keeps a unique relation with just one line of the truth table. The Table 2.2 illustrates a truth table for a 3-input function and the minterms for each line.

| Α | В | С | Minterm  | Equation |

|---|---|---|----------|----------|

| 0 | 0 | 0 | m0       | !A*!B*!C |

| 0 | 0 | 1 | m1       | !A*!B*C  |

| 0 | 1 | 0 | m2       | !A*B*!C  |

| 0 | 1 | 1 | m3       | !A*B*C   |

| 1 | 0 | 0 | m4       | A*!B*!C  |

| 1 | 0 | 1 | m5       | A*!B*C   |

| 1 | 1 | 0 | m6       | A*B*!C   |

| 1 | 1 | 1 | m7 A*B*C |          |

Table 2.2: Relation between minterms and lines of the truth table.

**Implicant minterms** are all minterms whose the function value is equal to '1'. Thus, as mentioned before, a canonical SOP is the one composed of all implicant minterms of a given logic function.

A sum containing all variables that compose the function is called **maxterm**. A maxterm also keeps a unique relation with just one line of the truth table. The Table 2.3 illustrates a truth table for a 3-input function and the maxterms for each line.

**Cube** is a set of minterms. While a minterm presents a relation with just one line of the truth table, a cube presents a relation with one line or a set of lines of the truth table. For instance, considering the two minterms (!a\*b\*c\*!d) and (!a\*b\*c\*d), that compose the equation f = (!a\*b\*c\*!d) + (!a\*b\*c\*d), it is possible to group them through equation manipulations, as follow:

$$(!a*b*c*!d) + (!a*b*c*d) = (!a*b*c)*(!d+d) = (!a*b*c)*1 = (!a*b*c)$$

(2.6)

This new simplified product (!a\*b\*c), derived from the two given minterms, is called a cube. When a cube is only composed of implicant minterms, this cube is called an **implicant cube**.

| Α | B | С | Maxterm     | Equation |

|---|---|---|-------------|----------|

| 0 | 0 | 0 | M0          | A+B+C    |

| 0 | 0 | 1 | M1          | A+B+!C   |

| 0 | 1 | 0 | M2          | A+!B+C   |

| 0 | 1 | 1 | M3          | A+!B+!C  |

| 1 | 0 | 0 | M4          | !A+B+C   |

| 1 | 0 | 1 | M5          | !A+B+!C  |

| 1 | 1 | 0 | M6          | !A+!B+C  |

| 1 | 1 | 1 | M7 !A+!B+!C |          |

Table 2.3: Relation between maxterms and lines of the truth table.

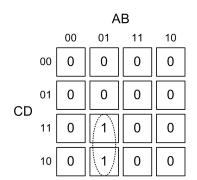

The **Karnaugh map** representation is an indexed matrix that permits to identify the adjacent minterms. Figure 2.1 illustrates a 4-input Karnaugh map for the minterms (!a\*b\*c\*!d) and (!a\*b\*c\*d). In this example, the values in the columns represent the logic values for variables 'a' and 'b', while the values in the lines represent the logic values for variables c and d.

Figure 2.1: Karnaugh map illustration.

As shown in the example, it is possible to group the two adjacent minterms to obtain a cube. When a cube cannot be grouped with any other cube or existing minterm, in order to form a larger cube, then this cube is called a **prime cube**.

When grouping adjacent minterms to compose cubes, some important definitions become apparent. The first one is related to the **cube literal cost** of a SOP. The cube literal cost of a SOP is the maximum number of literals in a single cube of the SOP. Consider the function given by the following prime irredundant SOP.

$$f = !a*!b*!d + !a*b*!c + a*!d*!e + a*c*d + b*c*!d*e$$

(2.7)

The cube literal cost of this SOP is four, as it has cubes with up to four literals.

The second definition is related to the **prime irredundant SOP with minimum cube literal cost** (SCHNEIDER, 2007). A prime irredundant SOP with minimum cube literal cost for function f is a prime irredundant SOP where the maximum number of literals in a single cube is minimum for function f. Consider the function given by the following prime irredundant SOP.

$$f = !a^{*!}b^{*!}d + !a^{*}b^{*!}c + a^{*!}d^{*!}e + a^{*}c^{*}d + !a^{*!}d^{*}e + a^{*}b^{*}c$$

(2.8)

The cube literal cost of this SOP is three, as it has only cubes with three literals. The prime irredundant SOPs given by equations (2.7) and (2.8) represent the same logic function. It is possible to show that the SOP in equation (2.8) is a prime irredundant SOP with minimum cube literal cost for function f, as no solution containing cubes with at most two literals is possible for f.

Consider now, as an example, the function f given by equations (2.7) and (2.8). The cubes !a\*b\*!c and a\*c\*d are **essential primes**, the remaining cubes and minterms are shown in the **covering table** of Table 2.4. It is possible to see that the cube b\*c\*!d\*e, with four literals, would be chosen in a **minimum literal cost SOP solution** like that presented in equation (2.7). However, this cube can be deleted from the covering table, leading to the **minimum cube literal cost SOP** presented in equation (2.8). The deletion of cubes with three literals would lead to an unfeasible covering table, as no minterm could be covered.

|          | minterms |   |   |   |    |    |    |    |    |    |

|----------|----------|---|---|---|----|----|----|----|----|----|

| cubes    | 0        | 1 | 4 | 5 | 13 | 16 | 20 | 24 | 28 | 29 |

| !a*!c*!d | •        | • |   |   |    |    |    |    |    |    |

| !c*!d*!e | •        |   |   |   |    | •  |    | •  |    |    |

| !b*!d*!e | •        |   | • |   |    | •  | •  |    |    |    |

| !a*!b*!d | •        | • | • | • |    |    |    |    |    |    |

| !a*!d*e  |          | • |   | • | •  |    |    |    |    |    |

| b*c*!d*e |          |   |   |   | •  |    |    |    |    | •  |

| a*b*c    |          |   |   |   |    |    |    |    | •  | •  |

| a*c*!e   |          |   |   |   |    |    | •  |    | •  |    |

| a*!d*!e  |          |   |   |   |    | •  | •  | •  | •  |    |

Table 2.4: Covering table for function f.

As mentioned before, for a given number of input variables there is a welldefined **number of functions**. This number is given by  $2^{2^n}$ , where 'n' is the number of input variables (SASAO, 2000). According to this statement, the number of 2-input functions is 16, 3-input functions is 256, 4-input functions is 65,536, 5-input functions is 4,294,967,296, and so on. This exponential relation lead to a search space almost intractable if many operations need to be repeated in a set of functions with more than 4-input. The set of *n*-input functions can be classified into different classes (set of functions) for different reasons: one is to reduce the search space, other is to group functions with equivalent or similar implementations. These sets are known as **equivalence classes**, and they may be obtained through input permutation/inversion as well as output inversion. P-class, N(in)-class, N(out)-class, NP-class, PN-class, and NPN-class are the possible reduced sets (SASAO, 2000; CORREIA, 2001). A class is a subset of logically equivalent functions as a result of a specific operation or their combination.

The first possible operation to obtain equivalent functions is the permutation of inputs. Table 2.5 presents an example of that operation. Notice that the input vectors are ordered differently for the truth tables of f2 (ABC ordering) and f4 (BCA ordering). The two functions are equivalent as once the permutation of inputs is done the truth tables are identical. Thus, f2 and f4 are equivalent by permutation, and can be gathered in a P-class set. The second operation to achieve equivalent functions is the inversion of inputs. In a similar way, Table 2.6 shows an example of obtaining an N(in)-class of 4 equivalent functions from this operation. In this case, f1, f2, f4 and f8 are equivalents. The last operation used is the inversion of the output. Table 2.7 illustrates this operation. Notice that the three operations can be combined. For instance, NP-classes are obtained after combining permutation and inversion of outputs. For NPN-classes all operations are performed.

| ABC | f2=AB+C | BCA | <i>f4=A+BC</i> |

|-----|---------|-----|----------------|

| 000 | 0       | 000 | 0              |

| 001 | 1       | 001 | 1              |

| 010 | 0       | 010 | 0              |

| 011 | 1       | 011 | 1              |

| 100 | 0       | 100 | 0              |

| 101 | 1       | 101 | 1              |

| 110 | 1       | 110 | 1              |

| 111 | 1       | 111 | 1              |

Table 2.5: Two P-class equivalent functions.

Table 2.6: Four N(in)-class equivalent functions.

| AB | <i>f1</i> | A!B | f2 | !AB | <i>f4</i> | !A!B | <i>f</i> 8 |

|----|-----------|-----|----|-----|-----------|------|------------|

| 00 | 1         | 01  | 0  | 10  | 0         | 11   | 0          |

| 01 | 0         | 00  | 1  | 11  | 0         | 10   | 0          |

| 10 | 0         | 11  | 0  | 00  | 1         | 01   | 0          |

| 11 | 0         | 10  | 0  | 01  | 0         | 00   | 1          |

| AB | f9 | <i>f6</i> |

|----|----|-----------|

| 00 | 1  | 0         |

| 01 | 0  | 1         |

| 10 | 0  | 1         |

| 11 | 1  | 0         |

Table 2.7: Two equivalent functions after output inversion.

Another possible classification of functions is related to their polarity behavior. **Positive unate** function is the one that presents a positive  $(0 \rightarrow 1)$  transition in its output when a positive input variation occurs in one (or more) of its inputs. The AND function (f=a\*b) is a positive unate function. Negative unate function, in turn, is the one that presents a negative transition  $(1 \rightarrow 0)$  in its output when a positive input transition occurs in one (or more) of its inputs. The NAND function (f=!a+!b) is a negative unate function. Binate function may present both positive and negative behavior in its output when a positive (or negative) transitions are applied in one (or more) of its inputs, depending on the values of the other inputs. The XOR function (f=!a\*b+a\*!b) is a binate function. Notice that, unate or binate behavior in a given logic function is always related to one of its inputs; for instance the function f=!a\*b+a\*!c is binate on variable 'a', positive unate on variable 'b', negative unate on variable 'c' and does not depend on variable 'd'. When all inputs of a logic function have monotonic increasing behavior, then it is said that the function is positive unate in all variables. The same occurs for the monotonic decreasing behavior, which determines that the function is negative unate in all variables. AND and OR logic functions are positive unate in all input variables. On the other hand, NAND and NOR ones are negative unate in all input variables. XOR function is an example of binate function in all variables.

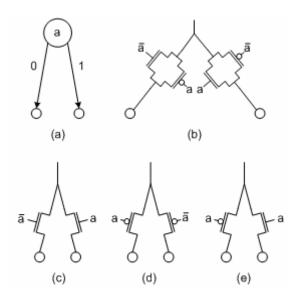

**Binary Decision Diagram (BDD)** is a data structure that can be used to represent a Boolean function. The function can be represented as a rooted, directed, acyclic graph, which consists of decision nodes and two terminal nodes called *0-terminal* and *1-terminal*. Each decision node is labeled by a Boolean variable and has two child nodes called *child-0* and *child-1*. The edge from a node to a *child-0* represents an assignment of the variable to *zero*. The edge from a node to a *child-1* represents an assignment of the variable to *one* (LEE, 1959).

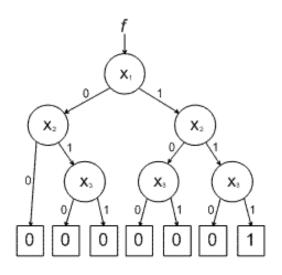

Figure 2.2 illustrates a BDD of 3-input AND function. In this example, the function f is '1' only if X1=1, X2=1 and X3=1. In case a variable is equal to '0', the function f presents the value '0' at the output. Notice that, the nodes in a BDD are sequentially evaluated until arriving in a terminal node.

Figure 2.2: BDD of 3-input AND function.

The basic idea from which the data structure was created is the Shannon's decomposition. A switching function is split into two sub-functions, knows as **cofactors**, by assigning one variable. If such a sub-function is considered as sub-tree, it can be represented by a binary decision tree. BDDs are considered the state-of-the-art structure for logic synthesis because they can be efficiently used as compact and suitable representation of logic functions (EBENDT, 2005).

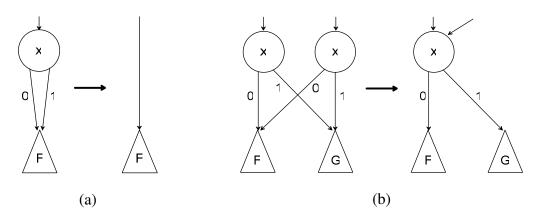

In Bryant (1986) a special class of BDDs is proposed. This class is known as **Reduce and Ordered BDD** (ROBDD). A ROBDD presents a fixed **variable ordering** and redundancy removal of BDD edges. The fixed variable ordering guarantees that a variable is evaluated just once along the BDD paths. The reduction of a BDD is based on two rules. The first one consists of removing BDD nodes that have their two edges connected to the same node. The second consists of sharing isomorphic nodes in the structure. Figure 2.3 illustrates these two rules.

Figure 2.3: BDD reduction: (a) eliminating nodes whose two children are isomorphic and (b) merging isomorphic sub-graphs.

Due to the fixed variable ordering in ROBDDs, the canonical form concept becomes noticeable. As presented before, the canonical concept is the capability of representing a logic function in a unique form. That is, equivalent functions are represented for isomorphic structures. Notice that, in ROBDDs, the canonical concept is valid only for a given fixed variable ordering. It means that two ROBDDs representing a function f with variable ordering o1 and o2 are guaranteed to be canonical if and only if o1 = o2.

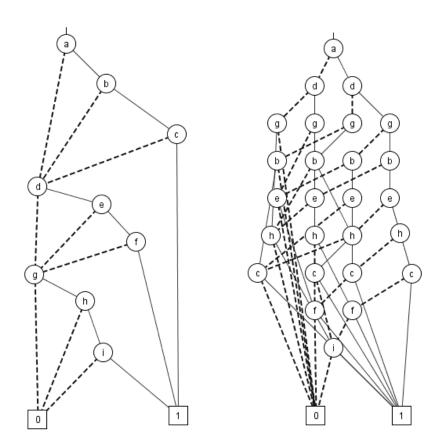

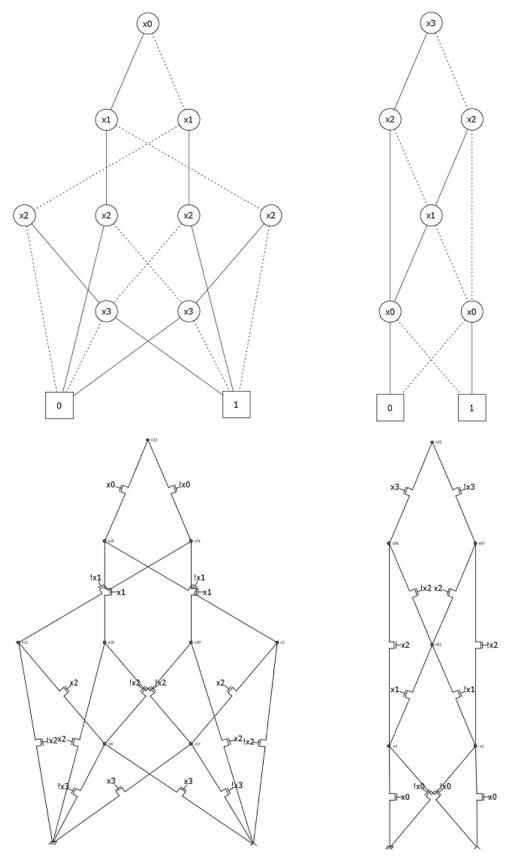

Another important issue of using BDDs to represent logic functions is related to the variable ordering. The size of the BDD is determined by the function being represented and the chosen ordering of the variables. For some functions, the size of a BDD may vary between a linear to an exponential range depending upon the ordering of the variables. As presented in Drechsler (1998) and Bollig (1996) the problem of finding the best variable ordering is *NP-hard*. However, there exist efficient heuristics to deal with the problem and to obtain acceptable orders in a reasonable CPU execution time (EBENDT, 2005). Figure 2.4 shows two BDD representing the same logic function, but with different variable orderings.

Figure 2.4: Different variable ordering ROBDDs representing a same logic function.

Examples of academic BDD packages used to manipulate Boolean functions are the CUDD (*Colorado University Decision Diagram*) developed in University of 32

Colorado (CUDD, 2008), and the BuDDy developed in Information Technology University of Copenhagen (BUDDY, 2008).

#### 2.2 A Brief History of Switching Network

Switch theory is an old discipline. Back in the 30's, when Claude E. Shannon started his work, the main logic elements were electromechanical, for instance, switches and relays. Vacuum tubes, diodes and transistors were used to make logic elements. In Shannon (1938) an analysis about relay networks and switching circuit implementation is presented. In Shannon (1953a) an investigation about how many contacts are necessary and sufficient to simultaneously realize all 16 switching functions of two variables was made. In Shannon (1853b) a machine built using selector switches and relays was conceived for helping the design of circuits composed of logic elements. In those days, the logic elements were very expensive. Also, networks to be realized were relatively small, allowing manual logic design procedures. In this context, during the 50's (MOORE, 1958) and in the 60's (HARRISSON, 1965), catalogs of minimum switch implementations were produced for the set of 4-input functions. Notice that, since old researches were done using relays, only the total number of switches was considered, without further investigation on how the arrangements of switches affect other characteristics of the circuit, like maximum number of devices in series and parallel. Recently, a method to determine the exact lower bound for the number of switches in series to implement a combinational logic cell was proposed in Schneider (2007). This opened the way for the generation of efficient networks having minimum length transistor chains. In the pioneer catalogs of Moore (1958) and Harrisson (1965), the lengths of transistor chains was not taken into account. Additionally, Moore and Harrisson proved that for most Boolean functions, the minimum implementation was not a series/parallel implementation. However, most of the library-free approaches are restricted to series-parallel implementations (BERKELAAR, 1988; REIS, 1998; CORREIA, 2004). Some exceptions are (JIANG, 2001) and (MARQUES, 2007). Jiang mixes pass-transistors with series-parallel implementations. Marques uses the lower bound from Schneider (2007) combined with the method presented here for the automatic generation of transistor networks with minimum chains in order to minimize the depth of a circuit in terms of transistor count. The work proposed here concentrate at the cell level, and investigates more efficient area and delay methods to optimize transistor networks taking into account the length of chains and the overall transistor counts.

#### 2.3 Logic Switches

Several different methods have been proposed for implementing switch networks. The resulting networks may present different properties, which are not described in a comprehensive way in the literature.

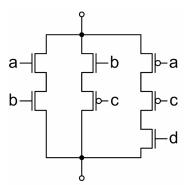

The basic element to implement networks is the **switch**. This element can be called as **direct switch**, when it conducts by applying a '1' logic value in its control terminal, or **complementary switch**, when it conducts by applying a '0' logic value in its control terminal. By composing these elements, it is possible to build arrangements, known as **logic networks**, to allow the interconnection between two different terminals according to a given logic function that this network represents.

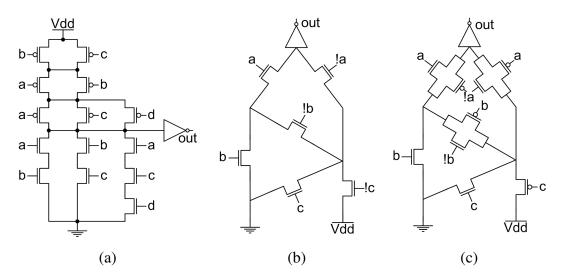

Depending of the technology used, these switches can be implemented as physical devices. In the currently CMOS technology, they are represented by the **NMOS** transistor (direct switch) and the **PMOS** transistor (complementary switch). Figure 2.5 illustrates the symbolic notation of these elements, and Figure 2.6 presents some logic networks representing arbitrary logic function.

Figure 2.5: Symbolic notation for PMOS and NMOS transistors.

Figure 2.6: Two logic networks representing arbitrary logic functions.

When looking at a single two terminal network, it may present the following properties:

- **Planar** Networks corresponding to a planar graph (HARARY, 1994). This king of graph can be drawn in the plane without crossing lines. In the case of networks, it is additionally required that the terminals be externally connected without crossing any lines. Planar networks have a dual graph, which has the interesting property of being the logically complementary. Figure 2.7a illustrates a planar network, while Figure 2.7b illustrates a non-planar network.

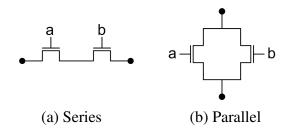

- Series-parallel When all switches in the network are connected in series or in parallel recursively. A network is series-parallel if and only if there is no embedded network having a Wheatstone bridge configuration (DUFFIN, 1965). All series-parallel networks are planar. This king of network is exemplified in Figure 2.8a.

- **Bridge network** A network with an embedded network containing the Wheatstone bridge configuration. A bridge network may or may not be planar. A bridge network is never a series-parallel network. Figure 2.8b presents a bridge network.

Also, some lemmas can be derived from these properties:

Lemma 1: all series-parallel networks are planar.

Lemma 2: all planar networks have a dual graph (from which a logically complementary network can be derived).

Lemma 3: all-non planar networks are bridge networks.

Lemma 4: bridge networks may or may not be planar.

Figure 2.7: (a) Planar network, (b) non-planar network.

Figure 2.8: (a) Series-parallel network, (b) bridge network.

When thinking about networks composed of two planes and about complementary properties, they can be basically classified as logically and/or topologically complementary.

A network is said to be **logically complementary** when there is one and only one of the networks conducting for every input vector condition. A **topologically complementary** network is the one that presents dual planes. Figure 2.9 exemplifies this idea. The usual method of construction of the dual is the following:

- 1. In a given planar graph, place a point in every region of the graph. In Figure 2.9a this points are labeled as 1, 2, 3 and 4.

- 2. Draw all lines connecting these points through one branch of the graph. It is illustrated by the dotted lines in Figure 2.9a.

Notice that the external points, which are not inside to any internal face of the graph, correspond to the terminals. It is done for the engineering purpose. Pay attention, in graph theory, it is not necessary to set two external points to build the dual graph (HARRISSON, 1965).

It is important to keep in mind that dual networks are implemented through dual graphs. These networks are logically complementary, but they are not derived from complementary graphs. Complementary graphs are a totally different concept, which do not lead to generation of logically complementary networks.

Figure 2.9: (b) Dual networks obtained through (a) dual graphs.

In the example presented in Figure 2.9b, the dual networks are bridge networks. But the same principle can be used to generate series-parallel networks, if the original graph is a series-parallel implementation. Another important point is related to the planar characteristic. If such graph is not planar, then it is not possible to derive the dual graph from it (HARARY, 1994). In this case, algorithms for graph planarization could be applied.

**Branch-based** is a logic network where the transistor arrangements are composed only by branches. It presents purely series-transistors connections to attach two terminal nodes (PIGUET, 1984; PIGUET, 1994; PIGUET, 1995; NÈVE, 2001). The main advantage of transistor branches is the absence of interconnections among branches, which is a positive characteristic in terms of physical design representation point of view. The construction of branch-based networks is rather simple. It takes a sum-of-products and translates each product into an *AND*-stack in the network. Figure 2.10 presents an example of a branch-based network.

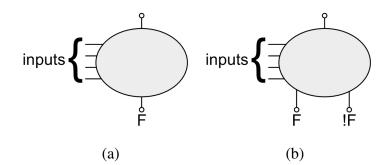

Figure 2.10: Branch-based network.

Additionally, logic networks can be also classified as **single-rail** or **dual-rail**. Single-rail networks provide the connection between two nodes. Dual-rail networks are capable of attaching one node to other two terminals, which very frequently are one for the direct polarity signal and one for the inverted polarity signal. Also, in dual-rail structures, a codification using the direct and inverted signal is done in order to guarantee the right signal propagation along circuit paths. Dual-rail logic is commonly used to build asynchronous circuits. Figure 2.11 illustrates the concept of a single and a dual-rail network.

Figure 2.11: (a) Single-rail network, (b) dual-rail network.

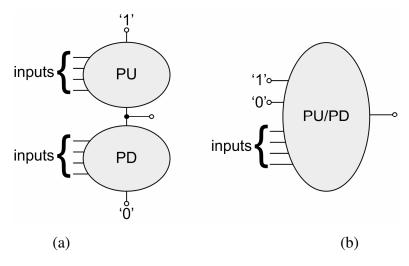

Basically, logic network can be constructed with their logic planes in a shared structure or not. In figure 2.12a the logical network is composed of two **disjoint planes**, where the **pull-up** and **pull-down** networks are implemented separately. Figure 2.12b illustrates a logic network built in a **non-disjoint plane**, where the pull-up and pull-down networks are sharing switch elements in a single plane.

Figure 2.12: (a) Disjoint planes, (b) non-disjoint planes.

The pull-up plane is the one that connects the output terminal to the '1' logic value, while the pull-down plane connects the output to the '0' logic value.

# 2.4 Network Generation

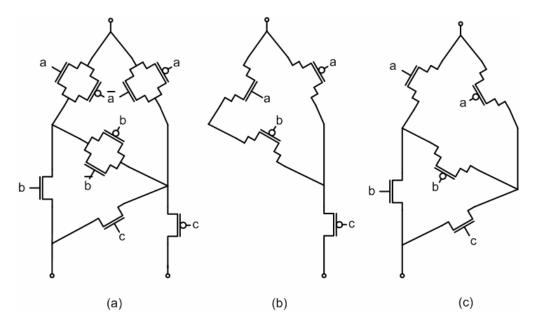

Two main approaches exist to synthesize switch networks. The first approach is the equation-based solution. In this approach, an equation is translated to a switch arrangement. The methods following this approach are devoted to the synthesis of series-parallel implementations, since bridge networks cannot be obtained through series-parallel association. Figure 2.13a shows a logic network obtained from the on-set equation presented in equation (2.9). Figure 2.13b illustrates a logic network obtained from the off-set equation presented in equation (2.10).

$$on-set = a*b + b*!c + !a*!c*d$$

(2.9)

$$off-set = a^{*!}b + !a^{*}c + !b^{*!}d$$

(2.10)

Notice that, in both cases, it is possible to attain the topologically and logically complementary networks using the dual graph generation.

Figure 2.13: (a) Network derived from the on-set and its dual network, (b) network derived from the off-set and its dual implementation.

Also it is possible to obtain the logically complementary network directly using the on-set equation to implement a given logic plane and using the off-set equation to generate the other. In this case, the obtained networks are not topologically complementary. Figure 2.14 illustrates this idea, showing the networks achieved from equation (2.9) and (2.10).

Figure 2.14: Logically complementary networks obtained from the on-set and the off-set equations.

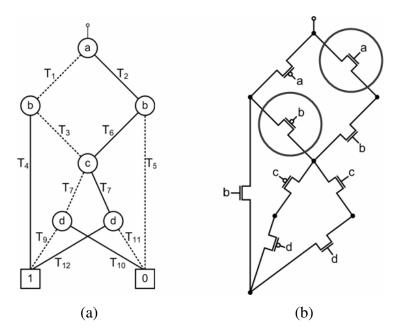

The second approach is a graph-based solution. In this approach a graph that represents the function is created (as a BDD, for instance), optimized and then a switch network is derived from this graph. This kind of approach is interesting as it can be used to derive both series-parallel as well as non series-parallel (bridge) implementations (ROSA, 2006).

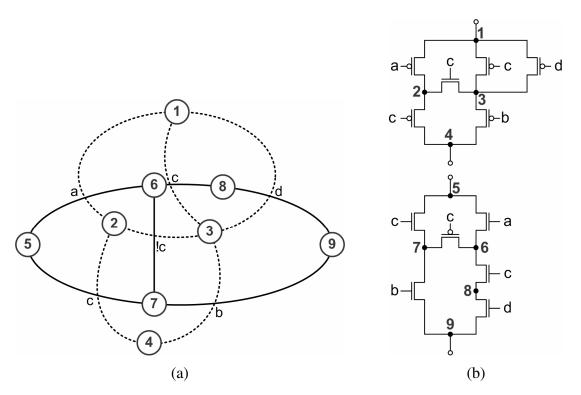

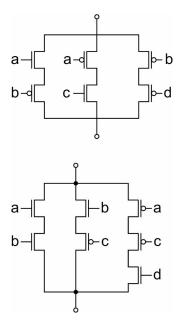

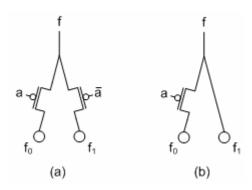

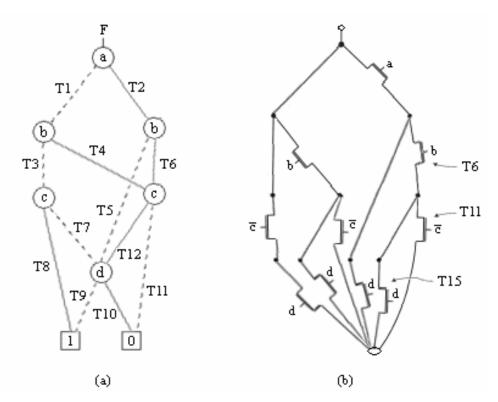

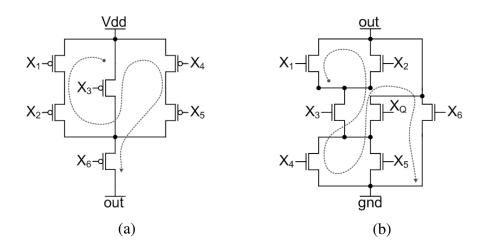

The basic action when deriving a switch network from a BDD is to associate a controlled switch to each arc of a BDD node. This concept is illustrated in Figure 2.15, which shows a BDD node and four possible ways to associate switches: transmition gates, NMOS transistors only, PMOS transistors only, and mixed PMOS/NMOS transistors (POLI, 2003).

Figure 2.15: BDD node and associated switches.

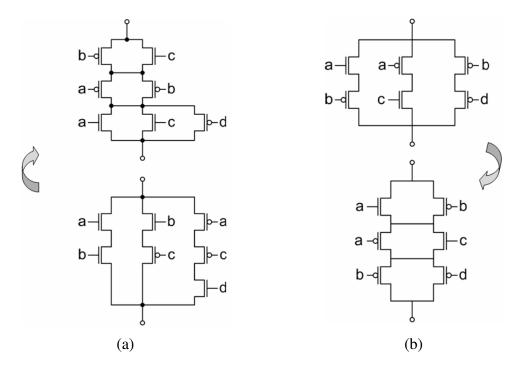

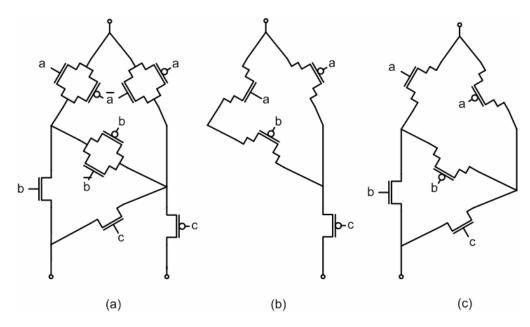

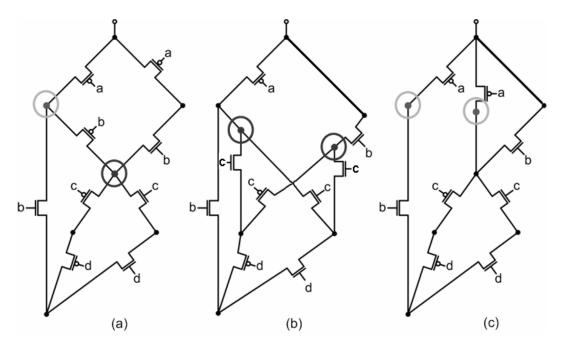

When a non-disjoint transistor network is built with a pair of PMOS and NMOS transistors associated to BDD edges, there is the possibility to derive disjoint networks from it. The procedure is straightforward, as it is illustrated in Figure 2.16. Notice that in the first case, Figure 2.16a, the network in a non-disjoint and a dual-rail implementation. On the other hand, Figure 2.16b and 2.16c are disjoint and single-rail implementations.

Figure 2.16: Networks derived from a BDD.

As an effect of using disjoint planes, the number of switches into the logic networks remains the same, but the number of nodes increases. Another important point is that, as the number of nodes increases while the number of elements remains the same, the number of connections to be performed among elements is reduced. This effect is visible in Figure 2.16.

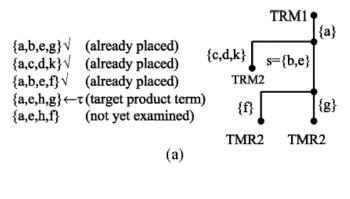

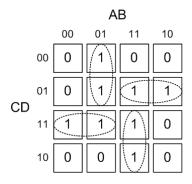

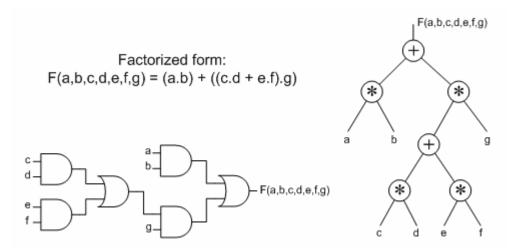

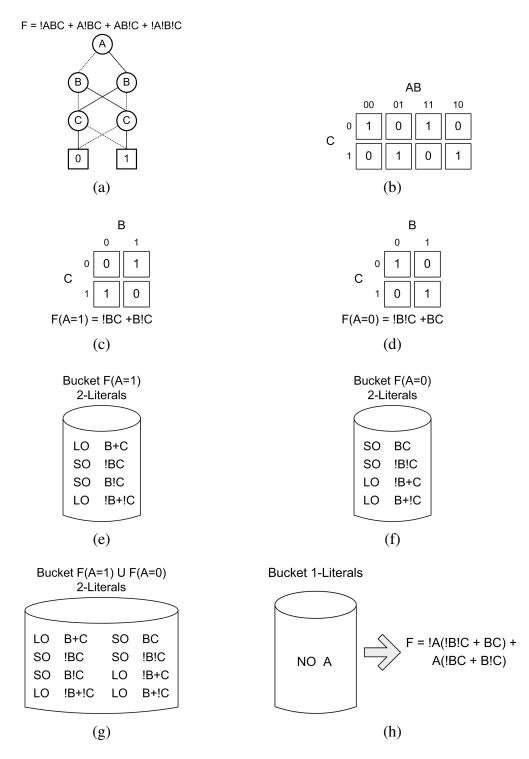

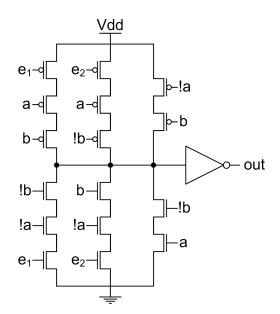

The most recent work regarding switch network synthesis was developed by Kagaris (2007). In this work the authors proposed a methodology to achieve bridge networks in order to optimize the circuit in terms of transistor count. A preliminary version of it appears in (KAGARIS, 2006). The switch network is built explicitly by computing the most economical placement for the next product term of the function in the currently constructed transistor network. The most economical placement is chosen each time among several alternatives, one of which is bridging.