# UNIVERSIDADE CATÓLICA DE PELOTAS ESCOLA DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM INFORMÁTICA

# Gerenciamento de Dispositivos de Borda Reconfiguráveis na Computação Pervasiva

por Eduardo da Silva Möller

Dissertação apresentada como requisito parcial para a obtenção do grau de Mestre em Ciência da Computação

Orientador: Prof. Dr. Maurício Lima Pilla Co-orientador: Prof. Dr. Adenauer Corrêa Yamin

DM-2008/1-004

Pelotas, abril de 2008

# **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

## **AGRADECIMENTOS**

Agradeço a Deus por me dar força dia após dia ao longo desta caminhada.

A minha família, em especial ao meu pai pela força e colaboração nesta jornada.

A minha esposa Fabiana pela compreensão e carinho nos momentos de stress.

Aos meus amigos e colegas da UFPel pelo apoio na realização deste trabalho, em especial ao meu chefe Lúcio e ao Diretor do Centro de Informática da UFPel e colega de mestrado João Ladislau.

A todos os meus colegas de mestrado pelo apoio nos momentos difíceis em especial: Rosaura, Rogério e Vanessa.

A Secretária Kátia pela colaboração e carinho.

A todo o corpo docente, em especial ao Prof. Dr. Adenauer C. Yamin pelo incentivo e apoio .

Ao Prof. Dr. Maurício L. Pilla pela competência e empenho na orientação desta dissertação e pela confiança depositada em mim.

E por fim, a todas as pessoas de forma direta ou indireta, que contribuíram para a realização deste trabalho.

# **SUMÁRIO**

| LIST                             | A DE FIGURAS                                                          | 5                          |  |  |

|----------------------------------|-----------------------------------------------------------------------|----------------------------|--|--|

| LIST                             | LISTA DE TABELAS                                                      |                            |  |  |

| LIST                             | A DE ABREVIATURAS E SIGLAS                                            | 8                          |  |  |

| RESU                             | J <b>MO</b>                                                           | 10                         |  |  |

| RESU                             | J <b>MO</b>                                                           | 11                         |  |  |

| 1 II<br>1.1<br>1.2<br>1.3<br>1.4 | NTRODUÇÃO Contexto e Histórico Motivação Objetivos Estrutura do Texto | 12<br>12<br>13<br>13<br>14 |  |  |

|                                  | COMPUTAÇÃO PERVASIVA                                                  | 15                         |  |  |

| 2.1                              | Evolução e Definições                                                 | 15                         |  |  |

| 2.1.1                            | Computação em Grade                                                   | 16                         |  |  |

| 2.1.2                            | Computação com Consciência de Contexto                                | 16                         |  |  |

| 2.1.3                            | Computação Móvel                                                      | 17                         |  |  |

| 2.1.4                            | Computação Pervasiva ou Ubíqua                                        | 17                         |  |  |

| 2.2                              | <b>EXEHDA:</b> Conceitos e Tecnologias                                | 18                         |  |  |

| 2.2.1                            | Aspectos de Modelagem e de Serviços                                   | 20                         |  |  |

| 2.2.2                            | A Organização do Ambiente Pervasivo                                   | 21                         |  |  |

| 2.2.3                            | O Núcleo                                                              | 23                         |  |  |

| 2.2.4                            | Definindo Perfis de Execução                                          | 24                         |  |  |

| 2.2.5                            | Organização Baseada em Serviços                                       | 25                         |  |  |

| 2.2.6                            | Conclusão                                                             | 29                         |  |  |

| <b>3</b> C                       | COMPUTAÇÃO RECONFIGURÁVEL                                             | 30                         |  |  |

| 3.1                              | Introdução                                                            | 30                         |  |  |

| 3.2                              | Definições da Computação Reconfigurável                               | 31                         |  |  |

| 3.3                              | Dispositivos Lógicos Programáveis - FPGAs                             | 32                         |  |  |

| 3.3.1                            | Arquitetura de um FPGA                                                | 33                         |  |  |

| 3.3.2                            | Vantagens e Desvantagens dos FPGAs                                    | 36                         |  |  |

| 3.3.3                            | Classificação dos FPGAs                                               | 36                         |  |  |

| 3.3.4                            | Aplicações dos FPGAs                                                  | 41                         |  |  |

| 3.4   | Conclusão                                                          | 42 |

|-------|--------------------------------------------------------------------|----|

| 4 S   | ERVIÇO DE ATUALIZAÇÃO DE CONFIGURAÇÕES DE <i>HARD</i> -            |    |

| V     | VARE - SACH                                                        | 43 |

| 4.1   | Modelagem do Serviço de Atualização de Configurações de Hardware - |    |

|       | SACH                                                               | 43 |

| 4.1.1 | Visão da Arquitetura do SACH                                       | 44 |

| 4.1.2 | Visão de Caso de Uso: Atores e Atividades do Serviço               | 47 |

| 4.1.3 | Visão da Implementação do Protótipo SACH                           | 61 |

| 4.1.4 | Visão das Estratégias de Instalação do SACH                        | 65 |

| 4.1.5 | Ativações Típicas na Operacionalização do SACH                     | 67 |

| 4.2   | Conclusão                                                          | 72 |

| 5 R   | RESULTADOS                                                         | 73 |

| 5.1   | Ambiente de Avaliação                                              | 73 |

| 5.2   | Resultados por Número de Dispositivos Simulados                    | 74 |

| 5.3   | Resultados por Tamanho de Pacote Distribuído                       | 75 |

| 5.4   | Conclusão                                                          | 78 |

| 6 (   | CONSIDERAÇÕES FINAIS                                               | 80 |

| 6.1   | Principais Conclusões                                              | 80 |

| 6.2   | Publicações Realizadas                                             | 81 |

| 6.3   | Trabalhos Futuros                                                  | 81 |

| REFI  | ERÊNCIAS                                                           | 83 |

# LISTA DE FIGURAS

| Figura 2.1  | Consolidação do Cenário da Computação Pervasiva                   | 16 |

|-------------|-------------------------------------------------------------------|----|

| Figura 2.2  | Visão Geral da Arquitetura EXEHDA                                 | 19 |

| Figura 2.3  | Visões de Atuação do EXEHDA                                       | 21 |

| Figura 2.4  | Composição do Ambiente Pervasivo                                  | 22 |

| Figura 2.5  | Organização do Núcleo do EXEHDA                                   | 23 |

| Figura 2.6  | Formato do Documento de Definição de Perfil de Execução do EXE-   |    |

| _           | HDA                                                               | 24 |

| Figura 2.7  | Exemplo de Documento de Definição de Perfil de Execução do EX-    |    |

|             | EHDA                                                              | 25 |

| Figura 2.8  | Organização dos Subsistemas do EXEHDA                             | 26 |

| Figura 3.1  | Estrutura de um Sistema Reconfigurável com Processador Hospedeiro | 32 |

| Figura 3.2  | Estrutura Básica de um FPGA                                       | 34 |

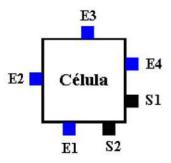

| Figura 3.3  | Célula Genérica da Maioria dos FPGAs                              | 34 |

| Figura 3.4  | Localização das Entradas e Saídas de uma Célula                   | 34 |

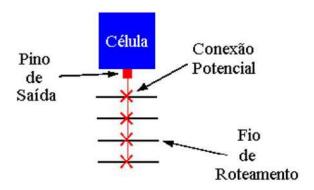

| Figura 3.5  | Ligação do Pino de Saída aos Segmentos do Canal de Roteamento     | 35 |

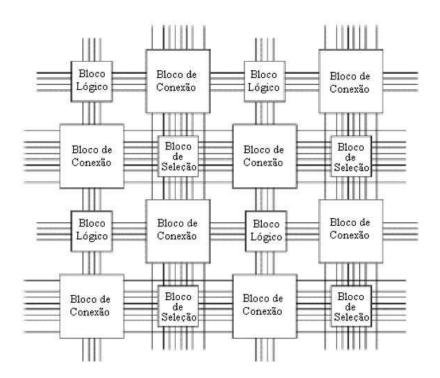

| Figura 3.6  | Estrutura Genérica de um FPGA                                     | 35 |

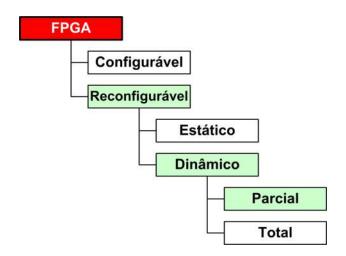

| Figura 3.7  | Classificação das FPGAs em Função dos Modos de Configuração       | 37 |

| Figura 3.8  | Reconfiguração Estática                                           | 37 |

| Figura 3.9  | Reconfiguração Dinâmica Global                                    | 38 |

| Figura 3.10 | Reconfiguração Dinâmica Parcial                                   | 38 |

| Figura 3.11 | Vários Tipos de Dispositivos Reconfiguráveis                      | 39 |

| Figura 3.12 | Exemplo de Reconfiguração Dinâmica                                | 40 |

| Figura 3.13 | Arquitetura do FPGA Virtex-II Pro                                 | 41 |

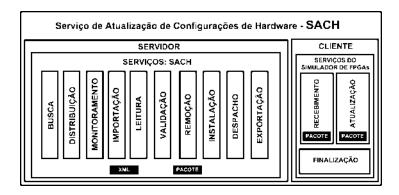

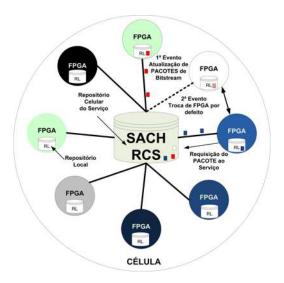

| Figura 4.1  | Visão da Arquitetura do Sistema SACH                              | 44 |

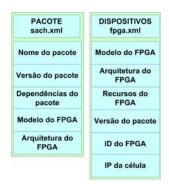

| Figura 4.2  | Arquivos Descritores - XML                                        | 46 |

| Figura 4.3  | Operações do SACH                                                 | 46 |

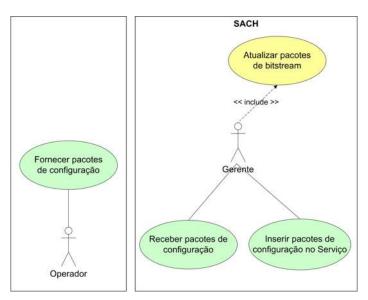

| Figura 4.4  | Atores do Sistema SACH                                            | 47 |

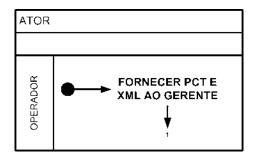

| Figura 4.5  | Diagrama de Atividades do Operador                                | 48 |

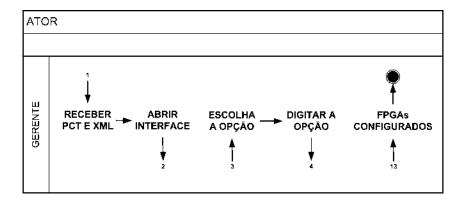

| Figura 4.6  | Diagrama de Atividades do Gerente                                 | 49 |

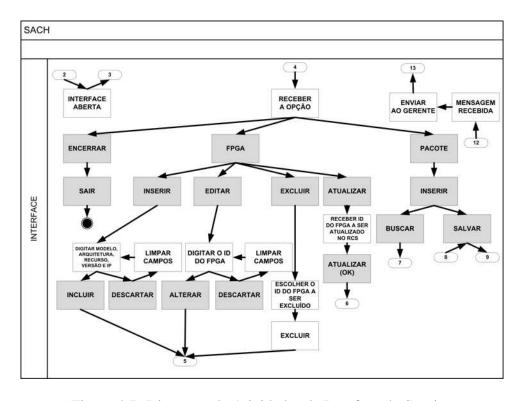

| Figura 4.7  | Diagrama de Atividades da Interface do Serviço                    | 49 |

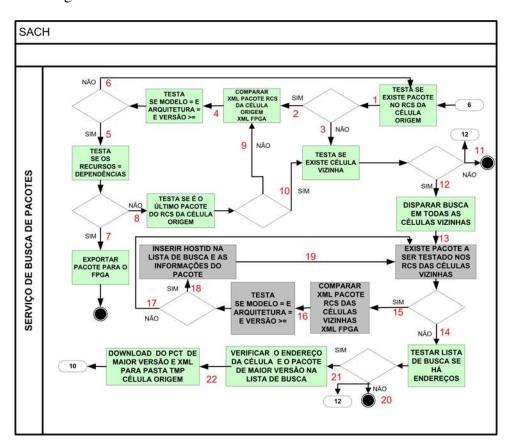

| Figura 4.8  | Diagrama de Atividades do Serviço de Busca de Pacotes             | 51 |

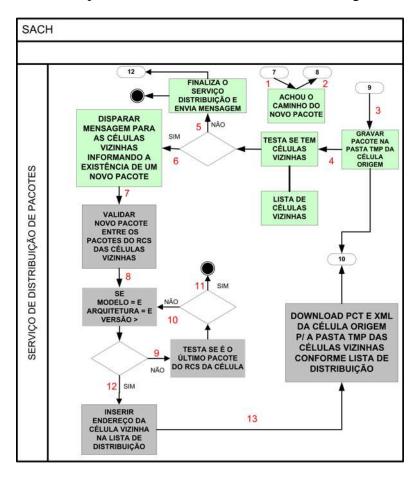

| Figura 4.9  | Diagrama de Atividades do Serviço de Distribuição de Pacotes      | 53 |

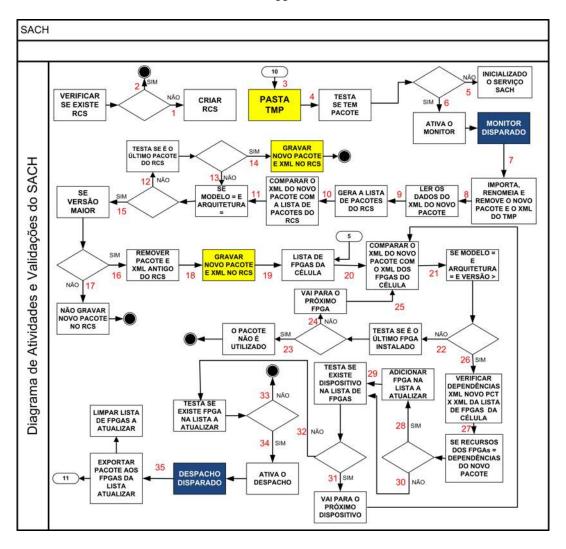

| Figura 4.10 | Diagrama de Atividades com as Validações de Pacotes do SACH       | 55 |

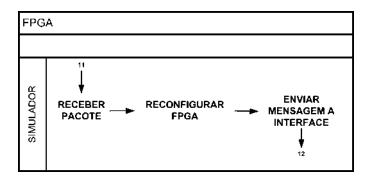

| Figura 4.11 | Diagrama de Atividades do Simulador de FPGA                       | 58 |

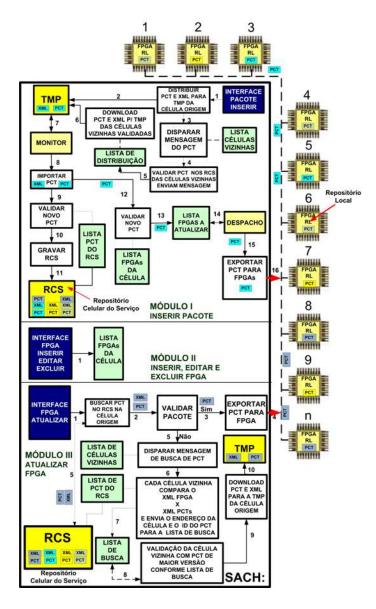

| Figura 4.12 | Funcionamento do SACH                                             | 59 |

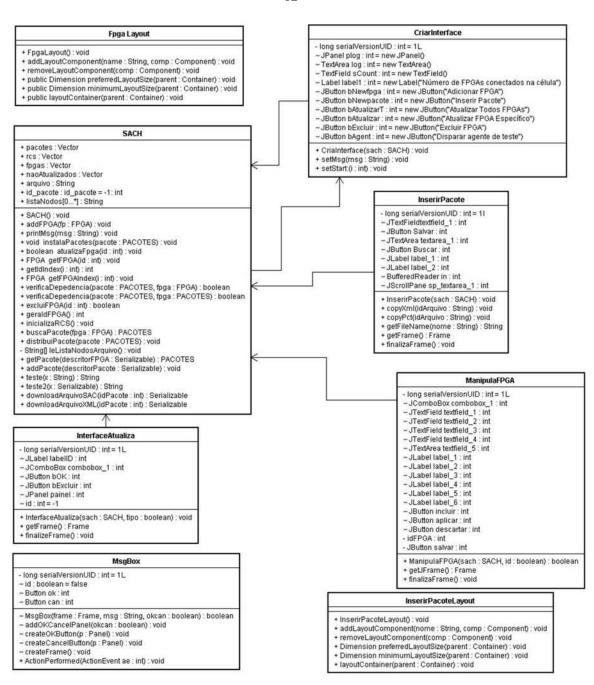

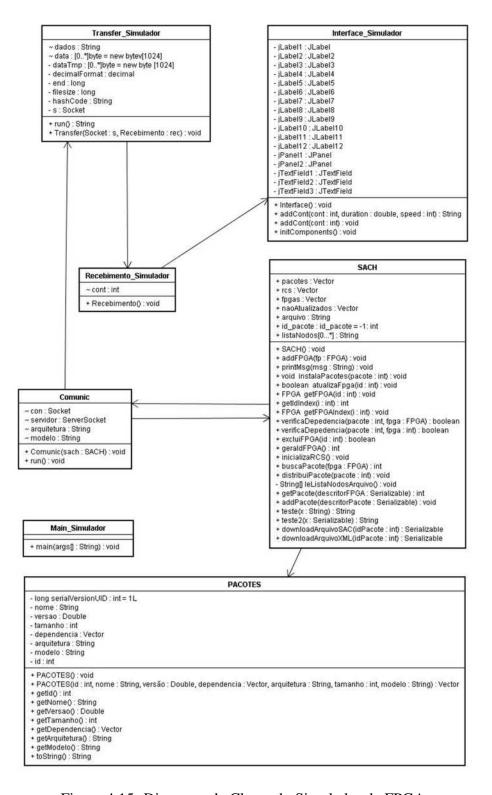

| Figura 4.13 | Diagrama de Classe da Interface do SACH                            | 62  |

|-------------|--------------------------------------------------------------------|-----|

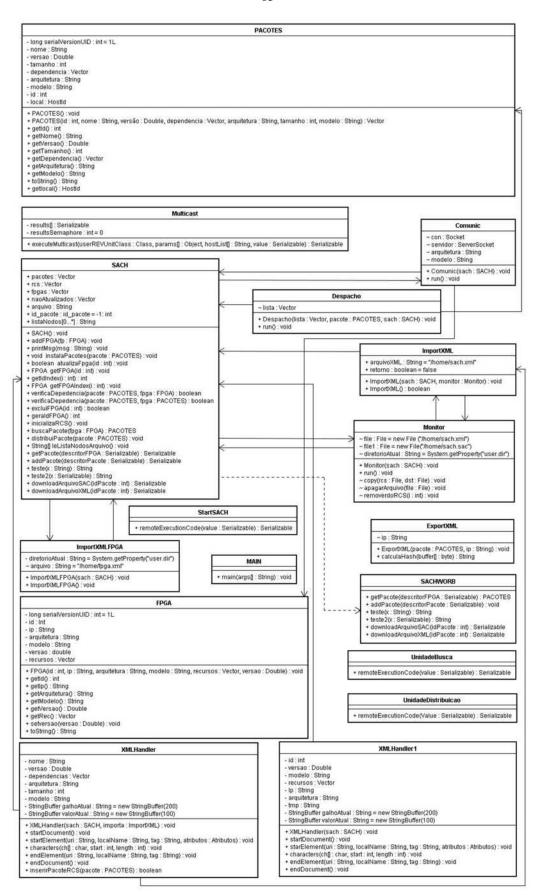

| Figura 4.14 | Diagrama de Classe do SACH                                         | 63  |

| Figura 4.15 | Diagrama de Classe do Simulador de FPGA                            | 64  |

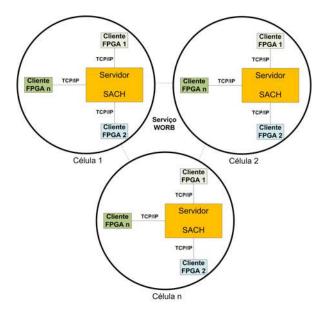

| Figura 4.16 | Diagrama de Instalação do SACH                                     | 65  |

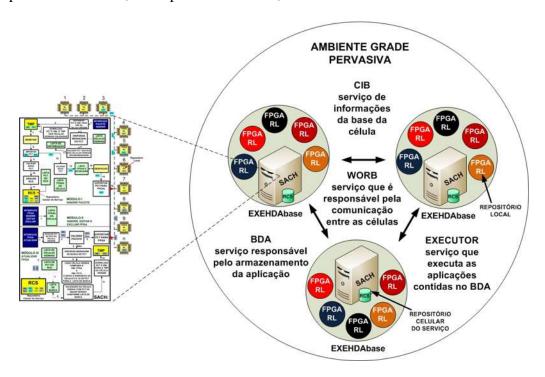

| Figura 4.17 | SACH em um Ambiente de Grade Pervasiva                             | 66  |

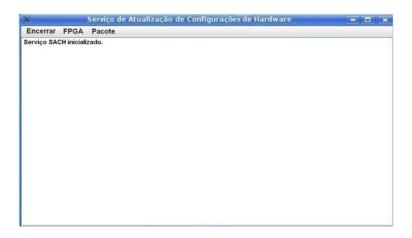

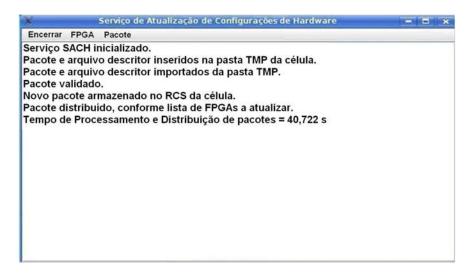

| Figura 4.18 | Tela de Abertura do SACH                                           | 68  |

| Figura 4.19 | Tela Inicial do SACH                                               | 68  |

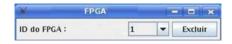

| Figura 4.20 | Tela de Inserção de um Novo FPGA                                   | 69  |

| Figura 4.21 | Tela de Alteração de um FPGA                                       | 69  |

| Figura 4.22 | Tela de Exclusão de um FPGA                                        | 69  |

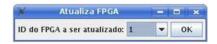

| Figura 4.23 | Tela de Atualização de um FPGA                                     | 70  |

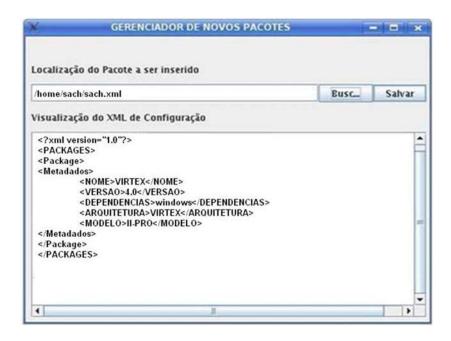

| Figura 4.24 | Tela de Inserção de um Novo Pacote                                 | 70  |

| Figura 4.25 | Tela de Controle e Tempo de Processamento e Distribuição de pacote |     |

|             | do SACH                                                            | 71  |

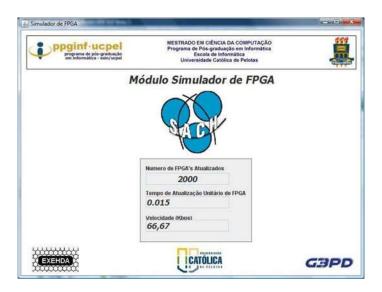

| Figura 4.26 | Tela do Módulo Simulador de FPGA                                   | 72  |

| D' 6.1      |                                                                    |     |

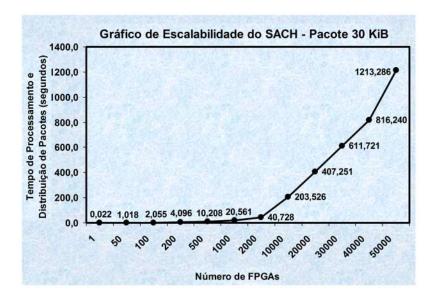

| Figura 5.1  | Gráfico de Escalabilidade x Tempo de Processamento e Distribuição  | 7.4 |

| F: 7.0      | de pacotes do SACH - Pacote de 30 KiB                              | 74  |

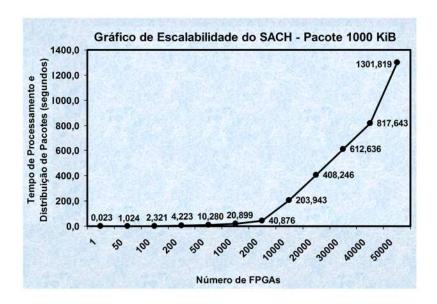

| Figura 5.2  | Gráfico de Escalabilidade x Tempo de Processamento e Distribuição  | 7.5 |

| F: 5.0      | de pacotes do SACH - Pacote de 1000 KiB                            | 75  |

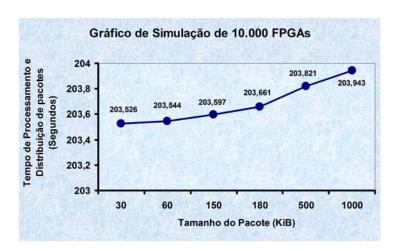

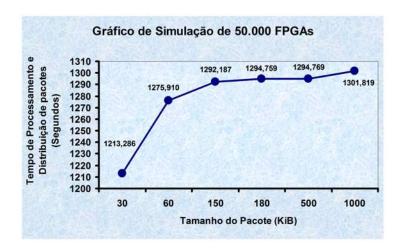

| Figura 5.3  | Gráfico de Tempo de Processamento e Distribuição de pacotes do     | 7.0 |

| F: 5.4      | SACH - 10.000 FPGAs                                                | 76  |

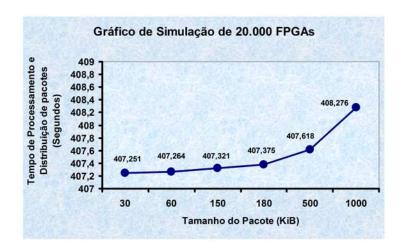

| Figura 5.4  | Gráfico de Tempo de Processamento e Distribuição de pacotes do     | 76  |

| F: 6.5      | SACH - 20.000 FPGAs                                                | 76  |

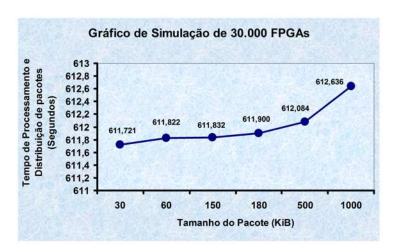

| Figura 5.5  | Gráfico de Tempo de Processamento e Distribuição de pacotes do     | 77  |

| T: # 6      | SACH - 30.000 FPGAs                                                | 77  |

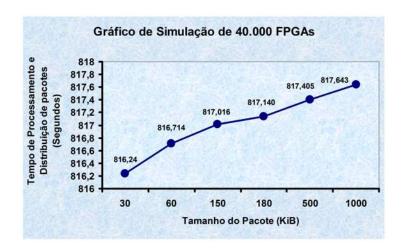

| Figura 5.6  | Gráfico de Tempo de Processamento e Distribuição de pacotes do     |     |

| T: 5.5      | SACH - 40.000 FPGAs                                                | 77  |

| Figura 5.7  | Gráfico de Tempo de Processamento e Distribuição de pacotes do     | 70  |

|             | SACH - 50.000 FPGAs                                                | 78  |

# LISTA DE TABELAS

| Tabela 5.1 | Informações Técnicas dos Equipamentos Utilizados | <br>74 |

|------------|--------------------------------------------------|--------|

|            |                                                  |        |

## LISTA DE ABREVIATURAS E SIGLAS

ASIC Application-Specific Integrated Circuit

AVA Ambiente Virtual de Aplicação

AVU Ambiente Virtual de Usuário

BDA Base de Dados Pervasiva das Aplicações

CIB Cell Information Base

CLB Configurable Logic Blocks

DCM Digital Clock Manager

EPROM Erasable Programmable Read-Only Memory

E/S Entrada e Saída

EXEHDA Execution Environment for Highly Distributed Applications

FIPSOC Field Programmable System On a Chip

FPGA Field Programmable Gate Array

IBM International Business Machines

ICC Integrated Circuit Cards

IOB Input/Output Blocks

I/O Input/Output

J2SE Java Standard Edition

J2ME Java Micro Edition

LUT Look-up Table

MAC Media Acess Control

MCS Master Control Station

OX Objeto EXEHDA

P2P Peer-to-Peer

PCT Pacote

PDA Personal Digital Assistent

PLD Programmable Logic Device

RCS Repositório Celular do Sistema

RL Repositório Local

RMI Remote Method Invocation

RPUs Reconfigurable Processing Units

RTR Run-Time Reconfiguration

SACH Sistema de Atualização de Configurações de *Hardware*

SDR Sistema de Distribuição Reconfigurável

SoC System-on-a-chip

TCP/IP Transmission Control Protocol/Internet Protocol

UI User Interface

UML Unified Modeling Language

XML eXtensible Markup Language

### **RESUMO**

Com o crescente desenvolvimento de novas tecnologias para redes de computadores com e sem fio, a miniaturização de dispositivos e o aumento da capacidade de processamento e armazenamento de informações observadas nos últimos anos, a computação e os diversos tipos de dispositivos computacionais estão cada vez mais presentes no dia-adia. Uma nova área que surge desse cenário é a Computação Pervasiva. Ao contrário dos sistemas desktop tradicionais, nesse novo paradigma os sistemas computacionais estão em contato com o usuário em qualquer lugar, a qualquer momento. A Computação Pervasiva pode ser entendida como um ambiente computacional, no qual o usuário fica liberado do gerenciamento da execução das suas aplicações, podendo dedicar-se às funcionalidades da computação pretendida. A Computação Reconfigurável, por sua vez, fornece dispositivos lógicos com a possibilidade de agregar o desempenho de um hardware fixo com a flexibilidade do hardware reprogramado através de software. No entanto, não há ferramentas que possam executar reconfigurações nestes dispositivos em ambientes de alta heterogeneidade, elevada dispersão geográfica e grande número de dispositivos. Neste sentido, este trabalho implementa um Serviço de Atualização de Configurações de Hardware - SACH, que possibilita a propagação de pacotes de bitstream de forma distribuída e concorrente para vários dispositivos de borda do tipo FPGA (Field Programmable Gate Array) para o middleware EXEHDA. O trabalho tem como principal objetivo: Desenvolver um Serviço de Atualização de Configurações de Hardware - SACH, incorporado ao middleware EXEHDA - Execution Environment for Highly Distributed Applications, utilizando dispositivos lógicos programáveis - FPGAs (Field Programmable Gate Array) como dispositivos de borda reconfiguráveis, em um ambiente pervasivo. Os resultados obtidos nos testes foram satisfatórios, o SACH gerenciou pacotes de reconfiguração, validando e distribuindo os mesmos aos dispositivos.

Palavras-chave: Computação Pervasiva, Computação Reconfigurável.

**TITLE:** "MANAGING BORDER RECONFIGURABLE DEVICES IN PERVASIVE COMPUTING"

## **RESUMO**

With the increasing development of new technologies for networks of computers with wireless and the miniaturization of devices and increase the capacity of processing and storage of information seen in recent years, the computing and the different types of computing devices are increasingly present in the day-to-day. A new area that comes of this scenario is the Pervasive Computing. Unlike traditional desktop systems, computing systems are in contact with the user anywhere at any time in this new paradigm. The Pervasive Computing can be understood as a computational environment, in which the user is freed of the management of the implementation of its applications, and can devote itself to the desired features. Reconfigurable Computing, in turn, provides logic devices with the possibility of adding the performance of a fixed hardware with the flexibility of the hardware reprogrammed through software. However, there are tools that can perform reconfigurations these devices in environments of high heterogeneity, high geographic dispersion and large number of devices. In that sense, this work implements a service to update reconfigurable hardware configurations - SACH, which enables the spread of package bitstreams to multiple FPGA (Field Programmable Gate Array) devices for the middleware EXEHDA. The work has as main goal: develop a service-Update Settings Hardware - SACH, embedded in the middleware EXEHDA - Execution Environment for Highly Distributed Applications, using programmable logic devices - FPGAs - Field Programmable Gate Array, as devices to edge reconfigurable, an environment pervasivo. The results obtained in the tests were satisfactory, the SACH managed packages of reconfiguration, validating and distributing them to the devices.

Palavras-chave: Pervasive Computing, Reconfigurable Computing.

# 1 INTRODUÇÃO

Este capítulo apresenta o contexto da pesquisa realizada, as motivações deste trabalho, bem como discrimina os objetivos tanto geral como os especificos desta dissertação.

#### 1.1 Contexto e Histórico

Vários benefícios são decorrentes da difusão dos sistemas computacionais, tais como mobilidade, velocidade e comodidade. Porém, esses benefícios têm seu custo. Na maioria das vezes, as pessoas são obrigadas a mudar de hábitos e métodos a fim de se adaptarem à onipresença do computador, ou seja, à ubiquidade (WEISER, 1991). Segundo Weiser, as facilidades computacionais devem ser incorporadas aos ambientes, a fim de auxiliar as atividades humanas, mudando minimamente a forma como tais atividades são realizadas.

Em sua visão em 1991, Weiser previa o crescimento no mercado dos dispositivos computacionais ubíquos de vários tamanhos: pequenos e pessoais (*inch-scale*), de médio porte (*foot-scale*) e grandes e de uso coletivo (*yard-scale*). De fato, isso acabou acontecendo: dispositivos pessoais de pequeno e médio porte tais como PDAs, *tablets* digitais e *laptops* tornaram-se comuns no final da década de 90. Da mesma forma dispositivos maiores, tais como lousas eletrônicas, passaram a fazer parte de ambientes de uso comum, tais como salas de reuniões, salas de aula e laboratórios.

Um outro aspecto importante colocado por Weiser, que também se confirmou é dado pelas novas aplicações computacionais que surgiram para explorar o uso desses novos dispositivos. O desenvolvimento de tais aplicações está diretamente associado a três temas, que atualmente são os principais focos de pesquisa na área da Computação Pervasiva, (i) interfaces naturais, (ii) computação ciente de contexto e (iii) captura e acesso de atividades humanas (ABOWD; MYNATT, 2000).

À medida que ambientes pervasivos tornam-se uma realidade e a computação não intrusiva passa a fazer parte da vida das pessoas, uma nova questão torna-se relevante que é a dimensão temporal das interações humanas. Essa questão fez surgir um novo tema que se associa aos três anteriormente citados: a computação no cotidiano (everyday computing), segundo a qual se faz necessário prover disponibilidade de serviço vinte quatro horas por dia, sete dias por semana, de forma a auxiliar computacionalmente atividades informais e não estruturadas comuns no dia-a-dia das pessoas.

A *Internet* e a difusão da Computação Distribuída estão conduzindo para o paradigma da Computação Pervasiva. A era do *mainframe* é caracterizada por muitas pes-

soas compartilhando um único e raro recurso computacional. Na era da computação pessoal, essa relação muda para um computador para cada pessoa. A *Internet* e a difusão da computação distribuída representam uma fase de transição, agregando componentes das eras do *mainframe* e da computação pessoal através do uso massivo do modelo Cliente-Servidor, em que os computadores pessoais são os clientes *webservices* e os *mainframes*, os servidores *webservices*. Essa transição conduz a uma terceira era: a da Computação Pervasiva, com vários computadores disponíveis para cada pessoa. Esses computadores estariam embutidos em praticamente tudo (nas paredes, na mobília e até nas roupas, etc.) e, principalmente, estariam interligados à *Internet*, formando, assim, uma gigantesca rede e possibilitando as mais diversas formas de utilização, (WEISER; BROWN, 1997).

## 1.2 Motivação

Três grandes motivações foram centrais no desenvolvimento deste trabalho de dissertação: a perspectiva de poder explorar a capacidade das arquiteturas reconfiguráveis no provimento de soluções para o atendimento das demandas introduzidas pela Computação Pervasiva; prover uma proposta que permita a reprogramação de dispositivos de forma distribuída e concorrente, sem intervenção humana direta, de arquiteturas reconfiguráveis de borda - FPGAs e dotar o *middleware* EXEHDA de um novo serviço. Este *middleware* é direcionado à Computação Pervasiva e o *hardware* previsto é do tipo *FPGA*.

Dentre os exemplos de aplicações deste novo serviço para o EXEHDA, destacase: os sistemas básicos de medição geral de energia elétrica e água, sistemas embarcados como as máquinas de auto-atendimento, postos de atendimento de sistemas bancários e máquinas de refrigerantes e outros.

## 1.3 Objetivos

O presente trabalho tem por objetivo geral:

• Desenvolver um Serviço de Atualização de Configurações de *Hardware* - SACH, incorporado ao *middleware* EXEHDA - *Execution Environment for Highly Distributed Applications*, utilizando dispositivos lógicos programáveis - FPGAs (*Field Programmable Gate Array*) como dispositivos de borda reconfiguráveis, em um ambiente pervasivo.

Por sua vez, destacaríamos como objetivos específicos:

- Modelar um Serviço de Atualização de Configurações de pacotes de bitstream para os dispositivos de borda - FPGAs na perspectiva da Computação Pervasiva;

- Implementar e testar o serviço modelado, utilizando como estudo de caso o *middle-ware* EXEHDA.

- Validar a operação do SACH no gerenciamento dos pacotes de reconfiguração de *hardware* a serem utilizados.

### 1.4 Estrutura do Texto

No Capítulo 2 são abordadas as definições e evoluções, relacionadas ao paradigma da Computação Pervasiva e as as definições e serviços do *middleware* EXEHDA. Já no Capítulo 3 são descritas as definições de Computação Reconfigurável. No Capítulo 4 é abordada a modelagem do Sistema de Atualização de Configurações de *Hardware*, bem como, a implementação de um protótipo, incorporando este serviço ao conjunto de serviços que o *middleware* EXEHDA fornece. Já no Capítulo 5 são descritos o ambiente de avaliação, os resultados obtidos em relação ao número de dispositivos simulados e tamanho de pacote distribuído e no Capítulo 6 são apresentadas as considerações finais, principais conclusões, publicações realizadas e os trabalhos futuros.

# 2 COMPUTAÇÃO PERVASIVA

Este capítulo apresenta diversas definições que contextualizam o escopo do trabalho, bem como revisa algumas tecnologias utilizadas na área.

## 2.1 Evolução e Definições

Segundo Weiser (WEISER, 1991), a Computação Ubíqua ou Pervasiva promove facilidades computacionais que devem ser incorporadas ao ambiente a fim de auxiliar atividades humanas de forma transparente. Dentro deste contexto, o computador tem a capacidade de acessar informações do ambiente no qual ele está inserido para a construção dinâmica de modelos computacionais.

Na perspectiva da Computação Pervasiva, os dispositivos que hoje nos cercam serão enriquecidos de novas facilidades de uso, necessitarão pouca manutenção, serão leves e portáteis, contemplarão bom poder de processamento e terão suporte à conectividade intermitente. As áreas de aplicação da computação pervasiva incluem: ensino, trabalho colaborativo, residências e automóveis inteligentes, entre outras (AUGUSTIN et al., 2006).

É possível verificar as transformações da Computação Móvel e da Computação em Grade, em relação a demanda real e qualificada de produtos, serviços e pesquisas. A Computação Pervasiva pode ser construída através da integração de três áreas da Computação: Computação Móvel, Computação em Grade e a Computação Consciente ao Contexto (YAMIN et al., 2005).

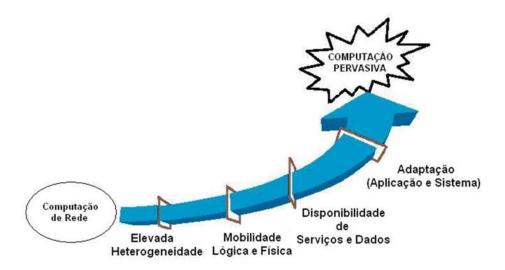

A Computação Pervasiva começou a ser potencializada com a evolução das Redes de Computadores e dos Dispositivos Móveis e Embarcados, quando confrontada com aspectos de heterogeneidade elevada, mobilidade, disponibilidade de dados e serviços, e adaptação ao contexto (YAMIN et al., 2005). A Figura 2.1 caracteriza, a consolidação do cenário em direção à Computação Pervasiva.

A área é de grande importância e vem sendo tratada sob diversas visões: Computações em Grade, com Consciência ao Contexto, Móvel, Pervasiva ou Ubíqua e outros tantos que têm sido usados muitas vezes como sinônimos, embora sejam diferentes conceitualmente, e empreguem diferentes idéias de organização e gerenciamento dos serviços computacionais. Com a evolução da área, os conceitos associados as visões com o passar do tempo vão se consolidando. Resumos dos conceitos associados são apresentados na seqüência.

Figura 2.1: Consolidação do Cenário da Computação Pervasiva (YAMIN, 2004)

### 2.1.1 Computação em Grade

A Computação em Grade introduz conceitos novos para infra-estruturas de tecnologia da informação, pois suporta uma Computação Distribuída sobre uma rede de recursos dispersos e heterogêneos, e trabalha para otimizar o uso de recursos já disponíveis com vistas à redução de investimentos de capital. Registra-se que a Computação em Grade tem um histórico de uso bem sucedido na computação de alguns tipos de aplicação de alto desempenho. A infra-estrutura pode consistir-se de todos os recursos em rede, desde computadores e dispositivos de armazenamento de variados tipos de capacidade até base de dados. A próxima geração associa novas tecnologias à Computação em Grade, como webservices, P2P e Computação Móvel (YAMIN, 2004).

## 2.1.2 Computação com Consciência de Contexto

Uma das primeiras pesquisas de investigação em computação com consciência de contexto foi apresentada no trabalho *Olivetti Active Badge* (WANT et al., 1992). Outro trabalho que teve forte significado na consolidação da área foi introduzido por Schilit que considera a Computação com Consciência de Contexto ser uma estrutura de *software* que se adapta de acordo com sua localização, coleção de pessoas e objetos próximos, bem como mudanças que ocorrem com os objetos durante determinado tempo (SCHILIT; THEIMER, 1994). Desde então, existem muitas tentativas para definir a Computação com Consciência de Contexto.

Segundo Dey, consciência de contexto foi se tornando de certa forma sinônimo de outros termos: adaptável, reativo, responsivo, sensível ao contexto. As diferentes definições de consciência de contexto estão inseridas em duas grandes categorias: uso de contexto e adaptação de contexto (DEY; ABOWD, 2000).

As definições prévias para estabelecer aplicações com consciência de contexto não são adequadas. Por isso Dey, define que um sistema é consciente de contexto quando o sistema usa o contexto para fornecer informações relevantes e/ou serviços para o usuário (DEY, 2001).

### 2.1.3 Computação Móvel

Dependendo da área, a Computação Móvel pode ser definida de diferentes formas:

- No caso do *hardware*, associamos ao termo Computação Móvel, a possibilidade de mobilidade física dos equipamentos. Um exemplo é o uso de *notebooks*, *laptops* e PDAs;

- No caso do software, chamamos de Computação Móvel quando um programa se desloca entre equipamentos interconectados por rede (CARDELLI, 2000). Neste caso, a Computação Móvel pode começar sua execução em uma célula de uma rede e em certo ponto ser movida para uma outra célula da estrutura distribuída dando continuidade a sua execução. Assim a computação pode ser executada localmente em várias células, utilizando o máximo de processamento e recursos disponíveis na rede. A mobilidade de software traz também grandes vantagens para os usuários de dispositivos móveis. Um usuário de um dispositivo de pouco poder computacional pode enviar um programa para ser executado em um outro equipamento disponível na rede e logo depois desconectar-se, reconectando novamente mais tarde para receber os resultados dessa computação.

### 2.1.4 Computação Pervasiva ou Ubíqua

Mark Weiser, considerado o pai da Computação Pervasiva ou Ubíqua, vislumbrou há uma década atrás, que no futuro, os computadores habitariam os mais triviais objetos.

Exemplos desses objetos seriam: etiquetas de roupas, xícaras de café, interruptores de luz, canetas e outros objetos de forma invisível para o usuário (WEISER, 1991).

Nesta perspectiva, a Computação Pervasiva, promove facilidades computacionais que devem ser incorporadas ao ambiente a fim de auxiliar atividades humanas mudando minimamente a forma como tais atividades são realizadas. Essa forma transparente de integrar tecnologia às atividades diárias das pessoas foi denominada Computação Pervasiva, (WEISER, 1991).

De maneira geral, o **grau de embarcamento** fornece o nível de inteligência dos computadores que estão inseridos dentro de um ambiente pervasivo, detectando, explorando e construindo dinamicamente vários modelos computacionais de seus ambientes.

Neste sentido, entende-se como Computação Pervasiva aquela onde os recursos de computação estariam onipresentes na vida diária de cada usuário e que estariam conectados com a finalidade de fornecer a informação ou serviços que os usuários solicitassem de qualquer lugar e em qualquer momento.

De modo mais específico, Mark Weiser definiu como característica da Computação Pervasiva, uma intercomunicação entre os computadores presentes em vários objetos PDAs, PCs, *laptops*, celulares, geladeiras, etc.).

Por sua vez, a disseminação dos computadores tanto em número quanto na dispersão geográfica, sugere além da disponibilidade de infra-estrutura computacional, um novo paradigma inspirado pelo acesso constante à informação e às capacidades computacionais (ABOWD; MYNATT, 2000).

O termo Computação Pervasiva ficou agregado à IBM quando da edição intitulada *Pervasive Computing* do *IBM System Journal* (PERVASIVE *Computing IBM System Journal*, 1999) (M., 1999), onde foi organizada uma digressão sobre os aspectos promissores da Computação Pervasiva, nesta mesma edição foi resgatada por Weiser, no artigo

intitulado *The origins of ubiquitous computing research at PARC in the late 1980s*, a sua visionária proposta quanto ao futuro da computação, na qual recursos de computação onipresentes se ajustariam, de forma autônoma, para atender os usuários.

Do ponto de vista da usabilidade, a Computação Pervasiva contempla um ambiente carregado de dispositivos de computação e comunicação que vai interagir com o homem de forma tranqüila - (Calm Technology). O usuário não perceberá que estará envolvido com máquinas, o ambiente interage com ele de forma autônoma e interativa (WEISER; BROWN, 1997). Embora esta proposta esteja ainda longe da realidade, vem sendo concretizada aos poucos, através da disponibilização de novas tecnologias como PDAs, SmartPhones, Palms e outros e também a consolidação de padrões para redes sem fio como o bluetooth e o IEEE 802.11, (YAMIN, 2004).

O objetivo da Computação Pervasiva é criar Ambientes Inteligentes (salas de aula, residências, escritório, hospitais, automóveis, etc.), onde os dispositivos em redes embebidos no ambiente forneça conexão discreta todo o tempo, melhorando assim a experiência do homem e a qualidade de vida sem conhecimento explícito sobre as comunicações e as tecnologias de computação. A informação caracteriza a situação de uma entidade, no caso, pessoa, lugar e objeto que é importante para o usuário e a aplicação.

## 2.2 EXEHDA: Conceitos e Tecnologias

O EXEHDA é um *middleware* direcionado a promover o suporte às aplicações distribuídas, móveis e conscientes do contexto da Computação Pervasiva (YAMIN et al., 2005). O EXEHDA fornece serviços com diferentes funcionalidades, dentre estes destacaríamos: migração de componentes de *software* de uma localização física para outra; persistência, aumentando a disponibilidade e o desempenho no acesso aos dados; descoberta de recursos, dando suporte ao movimento dos dispositivos móveis e dos componentes entre diferentes células; comunicação, que possibilita ser anônima e assíncrona; escalonamento, decidindo onde executar as aplicações, (YAMIN, 2004).

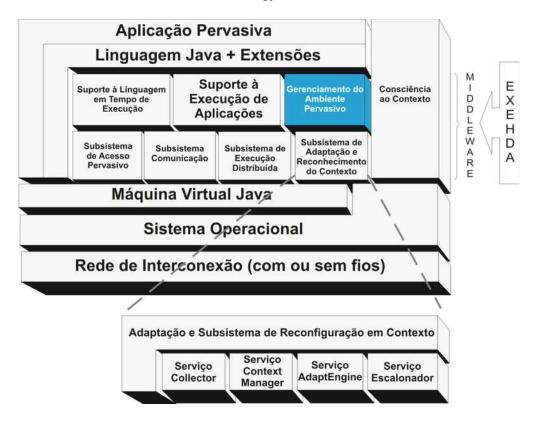

Com o objetivo de baixar o custo de especificar os aspectos necessários para o tratamento da semântica **siga-me** relacionados à mobilidade lógica e física, de distribuição e de adaptação, os mecanismos referentes aos aspectos oferecidos na linguagem programação, estão integrados ao ambiente de execução. A arquitetura de *software* do EXEHDA está resumida na Figura 2.2.

Desta forma, a arquitetura, modelada com esta perspectiva, apresenta uma organização lógica em três camadas (YAMIN, 2004):

- Camada de aplicação;

- Camada de suporte e ambiente de execução;

- Camada de sistemas básicos.

A **camada de aplicação** situa-se no topo, ilustrada na Figura 2.2, está a linguagem de programação, no qual disponibiliza abstrações para programação de aplicações distribuídas, móveis e conscientes do contexto direcionadas à Computação Pervasiva.

Na **camada intermediária** encontram-se os mecanismos de suporte à execução da aplicação pervasiva e às estratégias de adaptação ao *middleware* EXEHDA (YAMIN, 2004). Esta camada é formada por dois níveis.

Figura 2.2: Visão Geral da Arquitetura EXEHDA (YAMIN, 2004)

O primeiro nível é composto por três módulos de serviço à aplicação:

- Acesso pervasivo a código e dados;

- Reconhecimento de contexto:

- Ambiente de execução da aplicação.

O Acesso Pervasivo a Dados e Código é formado pelos componentes que disponibilizam o Ambiente Pervasivo, incluindo Ambiente Virtual do Usuário (*AVU*), Ambiente Virtual da Aplicação (*AVA*) e Base de Dados pervasiva das Aplicações (*BDA*).

O Ambiente Virtual do Usuário é composto pelos elementos que integram a interface de interação do usuário com o sistema. Este módulo é responsável pela implementação do suporte para que a aplicação que o usuário está executando em uma localização possa ser instanciada e continuada em outra localização sem descontinuidade, permitindo o estilo de aplicações (*follow me*) em um ambiente pervasivo.

O desafio da adaptabilidade para implementar o AVU é suportar os usuários em diferentes localizações, com diferentes sistemas de interação, que demandam diferentes sistemas de apresentação, dentro dos limites da mobilidade.

O *AVU* é o conjunto de atributos que identifica uma execução específica de uma aplicação, enquanto a *BDA* constitui o repositório de códigos das aplicações em geral.

O Ambiente de Execução da Linguagem tem a função de se encarregar pelo gerenciamento da aplicação durante seu tempo de vida. O SACH está aninhado na camada intermediária do primeiro nível no módulo de Gerenciamento do Ambiente Pervasivo, conforme é apresentado na Figura 2.2.

O Serviço de Reconhecimento de Contexto tem a função de informar o estado dos elementos de contexto de interesse da aplicação e do próprio ambiente de execução.

No **segundo nível**, localizada na camada intermediária, estão os serviços básicos do EXEHDA, que são compostas pelas funcionalidades necessárias para o primeiro nível e que cobrem vários aspectos, tais como:

- Migração: são os mecanismos para deslocar um componente de *software* de uma localização física para outra;

- Persistência: é o mecanismo para aumentar a disponibilidade e o desempenho do acesso aos dados;

- Descoberta de recursos dá suporte ao movimento dos dispositivos móveis e dos componentes entre diferentes células;

- Comunicação: possibilidade de ser anônima e assíncrona;

- Escalonamento: permite a decisão do melhor nodo para criar os componentes da aplicação;

- Monitoramento: os sensores que fornecem informações sobre o ambiente de execução e aplicação.

A camada inferior da arquitetura é constituída por sistemas e linguagens nativas que integram o meio físico de execução. Por questões de portabilidade, nesta camada a plataforma base de implementação é a Máquina Virtual Java em suas diferentes abordagens. Duas plataformas são utilizadas:

- J2SE (Java Standard Edition);

- J2ME (Java Micro Edition).

A existência de uma rede global, como a *Internet*, é suposta por esta arquitetura, e essa rede por sua vez é composta de um suporte à operação sem fio, interligada e outra cabeada que disponibiliza uma infra-estrutura de equipamentos e serviços em escala global (Rede Pervasiva).

A organização da arquitetura é em camadas lógicas, com níveis diferenciados de abstração e está direcionada para a busca de manutenibilidade de qualidade de serviços que é oferecida ao usuário através do conceito de adaptação.

O sistema se adapta para fornecer qualidade dos serviços prestados, enquanto que a aplicação se adapta para atender a expectativa do usuário, mantendo a funcionalidade da aplicação (YAMIN, 2004).

### 2.2.1 Aspectos de Modelagem e de Serviços

Nesta seção, além dos aspectos de modelagem, será feita uma (i) descrição dos principais serviços que compõem o EXEHDA, (ii) da sua interdependência, (iii) e da sua contribuição na construção do suporte à Computação Pervasiva.

A caracterização dos serviços tem o foco na descrição das funcionalidades providas através da sua interface, não sendo priorizados aspectos de implementação. Particularmente, a interface de cada serviço é documentada usando diagramas de classe da UML (*Unified Modeling Language*) de diagramas de classe.

É entendido como ambiente pervasivo, o ambiente computacional onde recursos e serviços são gerenciados pelo EXEHDA, no objetivo de atender os requisitos impostos pelo perfil da aplicação-alvo do projeto. A sua composição acontece tanto pelos dispositivos dos usuários, como pelos equipamentos da infra-estrutura de suporte, todos instanciados pelo seu respectivo perfil de execução do middleware.

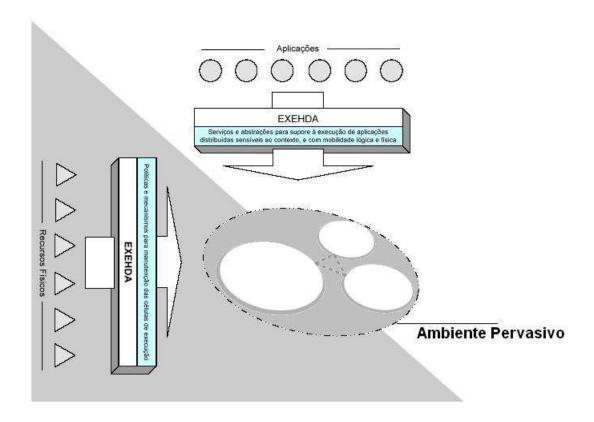

O EXEHDA tem duas grandes perspectivas: (ilustradas na Figura 2.3)

- A primeira é com relação às aplicações da Computação Pervasiva. O EXEHDA é

o provedor dos serviços que dão suporte às abstrações definidas quando do desenvolvimento. A interação das aplicações com o meio físico distribuído, através dos

serviços disponibilizados pelo EXEHDA proporciona a estas aplicações a visão do

ambiente pervasivo;

- E em uma segunda perspectiva, os recursos que compõem o meio físico distribuído: o EXEHDA executa a definição das políticas que normatizam a organização dos recursos e os mecanismos para sua gerência.

Figura 2.3: Visões de Atuação do EXEHDA (YAMIN, 2004)

### 2.2.2 A Organização do Ambiente Pervasivo

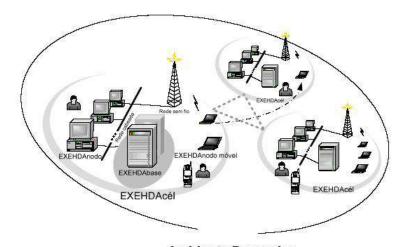

Com o objetivo de integralizar os cenários da Computação em Grade, da Computação Móvel e da Computação Sensível ao contexto, é mapeada em uma organização composta pela agregação de células de execução - em EXEHDAcels,

ilustrada na Figura 2.4. O meio físico o qual o ambiente pervasivo é definido é constituído por uma rede de infra-estrutura, no qual sua composição final pode ser modificada pela agregação dinâmica de nodos móveis, (YAMIN, 2004).

Os recursos da infra-estrutura física são mapeados para três abstrações básicas, utilizadas na construção do ambiente pervasivo:

- EXEHDAcel: é composta por duas abstrações principais: EXEHDAbase e EXEH-DAnodos. Os principais aspectos que devem ser considerados na definição da abrangência de uma célula são: o escopo institucional, a proximidade geográfica e o custo de comunicação;

- EXEHDAbase: pode-se definir como o ponto de contato para os EXEHDAnodos. Esta abstração tem a responsabilidade por todos os serviços básicos do ambiente pervasivo e, embora constitua uma referência lógica única, seus serviços, sobretudo por aspectos de escalabilidade, poderão estar distribuídos entre vários equipamentos. Isto é ilustrado na Figura 2.4 pelo sombreado associado ao símbolo da EXEHDAbase;

- EXEHDAnodo: representam os equipamentos de processamento disponíveis no ambiente pervasivo, sendo responsáveis pela execução das aplicações. Um subcaso deste tipo de recurso é o EXEHDAnodo móvel.

Esses nodos do sistema têm uma elevada portabilidade, tipicamente dotados de interface de rede para operação sem fio e, neste caso, integram a célula a qual seu ponto-de-acesso está subordinado. São funcionalmente análogos aos EXEHDAnodos, porém eventualmente com uma capacidade mais restrita (por exemplo, PDAs) (YAMIN, 2004).

Ambiente Pervasivo

Figura 2.4: Composição do Ambiente Pervasivo (YAMIN, 2004)

O ambiente pervasivo é composto por equipamentos multi-institucionais, o que direciona a um procedimento de gerência análogo ao utilizado nos ambientes de Grade Computacional - *Grid Computing* (YAMIN, 2004). A forma em que a organização celular do ambiente pervasivo é gerenciada e tem o objetivo central de resguardar a autonomia das instituições envolvidas. A procura de soluções para o gerenciamento multi-institucional tem feito parte da agenda de pesquisa de projetos de Computação em Grade.

#### **2.2.3 O Núcleo**

A funcionalidade promovida pelo EXEHDA é personalizável individualmente em cada nodo, sendo determinada pelo conjunto de serviços ativos e controlada por meio de perfis de execução. Um perfil de execução define um conjunto de serviços a ser ativado em um EXEHDAnodo, associando a cada serviço uma implementação específica dentre as disponíveis, bem como definindo parâmetros para sua execução.

O perfil de execução também controla a política de carga a ser utilizada para um determinado serviço, a qual se traduz em duas opções:

- Quando da ativação do nodo (bootstrap do middleware);

- Sob demanda.

Entretanto, a informação que é definida nos perfis de execução é também consultada quando da carga de serviços sob demanda, assim, a estratégia adaptativa para carga dos serviços acontece tanto na inicialização do nodo, quanto após este já estar em operação e precisar instalar um novo serviço (YAMIN, 2004).

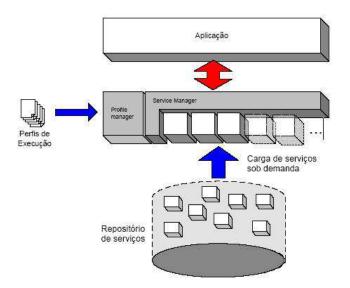

Esta política para carga dos serviços é disponibilizada pelo núcleo mínimo do EXEHDA, o qual é instalado em todo EXEHDAnodo que for integrado ao ambiente pervasivo. Este núcleo é formado por dois componentes, ilustrado na Figura 2.5:

*ProfileManager*: este componente executa a interpretação da informação disponível nos perfis de execução e a disponibiliza aos outros serviços do middleware. Cada EXEHDAnodo apresenta um perfil de execução individualizado;

ServiceManager: este componente tem a função de ativar os serviços no EXEH-DAnodo a partir das informações disponibilizadas pelo *ProfileManager*. Para que aconteça isto, ele carrega sob demanda o código dos serviços do middleware, a partir do repositório de serviços que pode ser local ou remoto, dependendo da capacidade de armazenamento do EXEHDAnodo e da natureza do serviço (YAMIN, 2004).

Figura 2.5: Organização do Núcleo do EXEHDA (YAMIN, 2004)

#### 2.2.4 Definindo Perfis de Execução

A definição do perfil de execução do EXEHDA, implica que cada EXEHDAnodo tenha o seu perfil de execução do middleware registrado através de um documento XML (Extensible Markup Language). Este documento traz a associação de nomes simbólicos de serviços a componentes que implementam a interface definida para os mesmos. O nome canônico de um serviço é padronizado, sendo determinado pela interface exportada. É possível, também, definir no perfil de execução para um determinado nodo, propriedades em que os valores sejam recuperados em tempo de processamento, com o objetivo de personalizar o funcionamento de um serviço. A forma genérica do documento XML que descreve o perfil de execução do middleware é ilustrado na Figura 2.6. Entretanto, um exemplo de documento instanciado para definição de perfil de execução do EXEHDA pode representado na Figura 2.7.

```

<EXEHDA>

<PROFILE name="profileName">

<SERVICE name="sName" impl="className" loadPolicy="boot"|"demand">

<PROP name="paramName" value="paramValue" />

</SERVICE>

</PROFILE>

</EXEHDA>

```

Figura 2.6: Formato do Documento de Definição de Perfil de Execução do EXEHDA (YAMIN, 2004)

Na Figura 2.7, um bloco *PROFILE* define um perfil de execução, sendo o valor do atributo *name* quem define o nome associado àquele perfil de execução. Internamente ao bloco *PROFILE*, blocos *SERVICE* são utilizados para descrição dos serviços que integram aquele perfil de execução específico.

No tocante ao bloco *SERVICE* pode-se descrever os seguintes atributos: *name* que caracteriza o nome do serviço, o *impl* especifica o componente (uma classe Java na versão atual do protótipo do EXEHDA) e o atributo *loadPolicy* define a política de carga que o núcleo do EXEHDA deve utilizar para o serviço.

Os elementos PROP são usados dentro de um bloco *SERVICE* para definir as propriedades que poderão ser recuperadas em tempo de execução pelo serviço, para personalização de sua execução e a parametrização dos serviços, via perfil de execução, também tem o papel de suportar a visão unificada da EXEHDAbase, repassando para os serviços em execução nos EXEHDAnodos à estratégia específica que deve ser utilizada para localização da instância celular daquele serviço (YAMIN, 2004).

Duas estratégias estão previstas:

- A primeira estratégia é uma referência para o dado armazenado na CIB (*Cell Information Base*);

- A segunda estratégia é uma referência direta para o nodo que hospeda a instância celular daquele serviço.

Esta segunda estratégia, via de regra, é reservada para indicação da instância celular da CIB.

```

<EXEHDA>

<PROFILE name="desktop-node">

<SERVICE name="logger"loadPolicy="boot">

<PROP name="imp1" value="org.isam.exehda.services.logging.BasicLogger"/>

<PROP name="logLevel" value="5000"/>

</SERVICE>

<SERVICE name="worb"loadPolicy="boot">

<PROP name="impl" value="org.isam.exehda.services.worb.worblmpl"/>

</SERVICE>

<SERVICE name="cib"loadPolicy="boot">

<PROP name="impl" value="org.isam.exehda.services.cib.CiblmplClient"/>

<PROP name="contactAddress" value="//143.54.7.137/cib"/>

<SERVICE name="bda"loadPolicy="boot">

<PROP name="impl" value="org.isam.exehda.services.bda.BdalmplClient"/>

<PROP name="bdaHost" value="lunaris.inf.ufrgs.br"/>

</SERVICE>

<SERVICE name="avu"loadPolicy="demand">

<PROP name="impl" value="org.isam.exehda.services.avu.AvulmplClient"/>

<PROP name="bdaHost" value="lunaris.inf.ufrgs.br"/>

</SERVICE>

<SERVICE name="executor"loadPolicy="boot">

<PROP name="impl" value="org.isam.exehda.services.primos.Executorlmpl"/>

</SERVICE>

<SERVICE name="gatekeeper"loadPolicy="boot">

<PROP name="impl" value="org.isam.exehda.services.avu.GatekeeperServices"/>

<PROP name="port" value="29901"/>

</SERVICE>

<SERVICE name="objectseed"loadPolicy="demand">

<PROP name="impl" value="org.isam.exehda.services.avu.ObjectSeedlmpl"/>

<\PROFILE>

\EXEHDA>

```

Figura 2.7: Exemplo de Documento de Definição de Perfil de Execução do EXEHDA (YAMIN, 2004)

#### 2.2.5 Organização Baseada em Serviços

Em um ambiente altamente heterogêneo, o requisito de operação, onde não só o *hardware* que exibe capacidades variadas de processamento e memória, mas também as bibliotecas de *software* disponíveis em cada dispositivo, trouxeram uma motivação com relação a adoção de uma abordagem na qual um núcleo mínimo do middleware tem suas funcionalidades estendidas por serviços carregados sob demanda.

Essa organização se reflete em um padrão de projeto do tipo micro-kernel. Adiciona-se a isto, que a carga sob demanda tem perfil adaptativo. Entretanto, poderá ser utilizada versão de um determinado serviço, melhor sintonizada às características do dispositivo em questão. Isto é possível, porque na modelagem do EXEHDA, os serviços estão definidos por sua interface, e não pela sua implementação (YAMIN, 2004).

Por isso que a contra-proposta à estratégia micro-kernel de um único binário monolítico, cujas funcionalidades cobrissem todas as combinações de necessidades das aplicações e dispositivos, se mostra impraticável na Computação Pervasiva, cujo ambiente computacional apresenta elevada heterogeneidade de recursos de processamento.

Contudo, o requisito do middleware de manter-se operacional durante os períodos de desconexão planejada motivou, além da concepção de primitivas de comunicação adequadas a esta situação, a separação dos serviços que implementam operações de natureza distribuída em instâncias locais ao EXEHDAnodo (instância nodal), e instâncias locais à

EXEHDAbase (instância celular) (YAMIN, 2004).

Neste sentido, o relacionamento entre instância de nodo e celular assemelha-se à estratégia de *proxies*, enquanto que o relacionamento entre instâncias celulares assume um caráter P2P. A abordagem P2P nas operações inter-celulares está alinhada com requisito de escalabilidade. Com isso, os componentes da aplicação em execução em determinado dispositivo podem permanecer operacionais, desde que, para satisfação de uma dada requisição pelo middleware, o acesso a um recurso externo ao dispositivo seja prescindível.

Por outro lado, a instância celular, em execução na base da célula, provê uma referência para os outros recursos, no caso da realização de operações que requeiram coordenação distribuída. Neste sentido, observe-se que a EXEHDAbase é uma entidade estável dentro da EXEHDAcel, permitindo que os demais integrantes, no caso os recursos, da célula tenham um caráter mais dinâmico no que se refere a sua disponibilidade na célula.

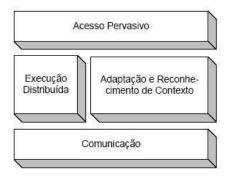

A organização do núcleo mínimo do EXEHDA, e o conjunto atual de serviços projetados para atender as necessidades da arquitetura, são apresentados nas seções seguintes. Os serviços do EXEHDA estão organizados em quatro grandes subsistemas, ilustrado na Figura 2.8.

Figura 2.8: Organização dos Subsistemas do EXEHDA (YAMIN, 2004)

- 1. Execução distribuída;

- 2. Adaptação;

- 3. Comunicação;

- 4. Acesso pervasivo.

A seguir estão descritos os vários subsistemas que compõem o EXEHDA. Seu estudo teve por objetivo reunir subsídios para modelagem e implementação do protótipo SACH, resguardando a integração do mesmo a infra-estrutura de *software* já existente.

Com o intuito de preservar a objetividade do texto serão comentados com um pouco mais de detalhes, os serviços cuja a relação com o SACH é mais direta. É importante observar de modo indireto, quando do processamento de aplicações ocorrem uma interação que via de regra irá envolver os serviços do EXEHDA como um todo.

#### 2.2.5.1 Subsistema de Execução Distribuída

Este subsistema tem a responsabilidade de dar suporte ao processamento distribuído no EXEHDA. O objetivo é produzir uma execução pervasiva. O subsistema interage com outros subsistemas do EXEHDA como o subsistema de reconhecimento de contexto e adaptação, para produzir o comportamento distribuído e adaptativo às aplicações da arquitetura. O subsistema é composto pelos seguintes serviços: (YAMIN, 2004)

#### Serviço Executor

Este serviço tem o objetivo de acumular as funções de disparo de aplicações, e de criação e migração de seus objetos. Com relação à implementação destas funções é empregada a instalação de código sob demanda. Ele interage com os serviços *CIB* e *BDA*. Já a interface do serviço Executor define métodos que controlam os ciclos de vida das aplicações e dos objetos.

#### Cell Information Base - CIB

O objetivo deste serviço é implementar a base de informações da célula. A funcionalidade deste serviço se relaciona com a manutenção da infra-estrutura distribuída que constrói o ambiente pervasivo. Os dados estruturais do EXEHDAcel são mantidos por este serviço, tais como:

- Informações sobre os recursos que a compõem;

- Informação de vizinhança;

- Atributos que descrevem as aplicações em execução.

O serviço se responsabiliza também pela manutenção das informações referentes aos usuários registrados na célula. Estas mesmas informações incluem um certificado assinado que mantém a chave pública do usuário.

#### **OXManager**

Toda a gerência e manutenção da meta-informação associada a um *OX* - Objeto eXehda é uma função do serviço *OXManager*. Este serviço consiste de uma instância de objeto, que é desenvolvida por intermédio do serviço Executor, podendo ser associada a meta-informação em tempo de execução.

O serviço faz todas as operações de consulta e atualização dos atributos do OX no ambiente pervasivo, possibilitando o acesso a partir de qualquer nodo.

Este subsistema também é formado pelos serviços *Discoverer, ResourceBroker, Gateway, StdStreams, Logger* e *Dynamic Configurator*. Estes serviços embora componham a infra-estrutura de suporte à execução, e deste modo participem das computações em geral, apresentam uma relação indireta com o SACH.

#### 2.2.5.2 Subsistema de Reconhecimento de Contexto e Adaptação

O middleware EXEHDA apresenta um suporte à adaptação que está associado à operação do Subsistema de Reconhecimento de Contexto e Adaptação. O mesmo subsistema proporciona serviços desde a extração da informação bruta sobre as características dinâmicas e estáticas dos recursos que compõem o ambiente pervasivo, passando pela identificação em alto nível dos elementos de contexto, até o disparo das ações

de adaptação em reação a modificações no estado de tais elementos de contexto. O subsistema é composto pelos seguintes serviços (YAMIN, 2004). Este subsistema também é formado pelos serviços *Collector*, *Deflector*, *ContextManager*, *AdaptEngine* e *Scheduler*. Os quais não tem interface direta com o SACH.

#### 2.2.5.3 Subsistema de Comunicação

Tanto a mobilidade de *hardware* como a de *software*, na maior parte das vezes, não possibilita a interação contínua entre os componentes da aplicação distribuída. As desconexões ocorrem constantemente, por motivo de links sem fio que podem existir ou por uma estratégia de economizar energia nos dispositivos móveis. Este subsistema oferece mecanismos que apresentam estes aspectos da Computação Pervasiva (YAMIN, 2004). O subsistema é composto pelos seguintes serviços:

#### **WORB**

O objetivo do serviço *WORB* é de simplificar a construção de serviços distribuídos. Este serviço possibilita aos programadores focalizarem os esforços no refinamento da semântica distribuída integrada ao serviço em desenvolvimento, abstraindo aspectos de baixo nível relativos ao tratamento de comunicações em rede. Este serviço oferece também um modelo de comunicação que se baseia nas invocações remotas de método, similar ao *Remote Method Invocaction* - RMI, porém sem exigir a manutenção da conexão durante toda a execução da chamada remota.

Este subsistema também é formado pelos serviços *Dispatcher* e *CCManager*, os quais se relacionam de forma indireta com o SACH.

#### 2.2.5.4 Subsistema de Acesso Pervasivo

O acesso a dados e códigos em qualquer lugar, a qualquer tempo, na Computação Pervasiva necessita de um suporte do middleware. Os serviços que fazem parte deste subsistema no EXEHDA são: *BDA*, *AVU*, *SessionManager* e *Gatekeeper* (YAMIN, 2004). O subsistema é composto pelos seguintes serviços:

#### **BDA**

Um ambiente de Computação Pervasiva tem por características a possibilidade do usuário, disparar aplicações a partir de qualquer nodo integrante do sistema e, após esse disparo, ter uma mobilidade parcial ou integral de tais aplicações em resposta as modificações em seu contexto de execução, como, por exemplo, a movimentação do usuário ou alteração na condição de carga dos dispositivos atualmente em uso pela aplicação.

Com isso a capacidade de instalação de código sob demanda é uma necessidade prescindível à execução de aplicações para a Computação Pervasiva. Seria impossível manter todo o universo de *software* disponível instalado e atualizado em todos os dispositivos do sistema. Entretanto, a implementação do mecanismo de instalação sob demanda, necessita da existência de um repositório de código que forneça a mesma visão do *software* disponibilizado a partir de qualquer dispositivo do ambiente pervasivo, mesmo após migrações.

Com isso, outras funcionalidades para o repositório pervasivo são necessárias. Considerando as diversas aplicações disponibilizadas segue linhas de evolução indepen-

dentes, o suporte a controle de versões é oportuno na direção da manutenção da operacionalidade das diferentes aplicações.

Este subsistema também é formado pelos serviços *AVU*, *SessionManager* e *Gate-keeper*, os quais não são usados diretamente pelo SACH.

#### 2.2.6 Conclusão

Este capítulo, apresenta as evoluções e definições com relação ao paradigma da Computação Pervasiva ou Obíqua, bem como, outras definições com relação a Computação em Grade, Computação com Consciência de Contexto e também apresenta o *middleware* EXEHDA desenvolvido para promover o suporte à execução de aplicações para a Computação Pervasiva, principalmente em relação aos problemas de heterogenidade, mobilidade física e lógica, disponibilidade de dados e serviços e adaptação do contexto com relação a aplicação e serviços. Este capítulo descreve a definição do *middleware*, a sua arquitetura, os aspectos de modelagem, a organização do ambiente pervasivo e dos serviços, como é formado o núcleo e no final descreve resumidamente alguns dos serviços que são utilizados de forma direta no SACH e apenas relaciona os outros serviços que não são diretamente usados.

# 3 COMPUTAÇÃO RECONFIGURÁVEL

Neste capítulo são discutidos vários tópicos com relação as arquiteturas reconfiguráveis. Primeiramente é abordada uma breve introdução sobre a classificação das soluções de *hardware* em função da implementação, relatando suas vantagens e desvantagens. Na seção 3.2 apresenta as definições da Computação Reconfigurável. Já na seção 3.3 é descrita uma abordagem geral em relação ao FPGA (*Field Programmable Gate Array*), apresentando a arquitetura do mesmo, as vantagens e desvantagens na utilização, a classificação conforme o modo de configuração e granularidade dos dispositivos, tipos de FPGAs com reconfiguração dinâmica total e parcial como os da família *Virtex II Pro*, as aplicações do FPGA e, finalizando, a conclusão do capítulo.

## 3.1 Introdução

Atualmente percebe-se a ocorrência de um crescimento considerável na utilização de computadores. As soluções de *hardware* podem ser classificadas em função da sua implementação em dois grandes grupos (SILVA MARTINS et al., 2005):

- *Hardware* fixo;

- Hardware programável através de software.

A escolha entre *hardware* fixo e programável através de *software* envolve uma escolha entre desempenho e flexibilidade. *Hardware* fixo é mais eficiente e atinge melhor desempenho e menor consumo. No entanto, não permite a flexibilidade de atualização que o *hardware* programável através de *software*, disponibiliza.

Geralmente estes tipos de implementações são denominadas como: soluções em *hardware* e soluções em *software*.

As desvantagens relacionadas com o desempenho, flexibilidade e custo de cada um desses tipos de implementações de soluções abordadas anteriormente são os principais problemas que deram origem ou motivaram o surgimento da computação reconfigurável.

A falta de uma maior flexibilização e a sub-utilização com relação as aplicações diversas são os principais problemas ou deficiências do paradigma de *hardware* fixo. O motivo dessas deficiências é que o dispositivo fixo não pode ser alterado após a sua fabricação e também por não se conseguir adaptá-lo em certas situações que ocorrem durante as execuções de diversas tarefas computacionais.

Já no paradigma de *software* (*hardware* programável mais *software*), o desempenho é a principal deficiência. Mesmo com a grande flexibilidade para a execução de

qualquer tipo de trabalho que envolva processamento computacional, registra-se menor desempenho para executar certos tipos de tarefas e operações. Caso essas operações sejam executadas em um dispositivo de *hardware* fixo, o tempo de execução seria menor, pois não haveria necessidade de buscar instruções na memória, decodificá-las, buscar dados, e executar as operações requeridas. Além disso, a execução mais eficiente em *hardware* também tende a consumir menos energia.

Quando ocorre um aumento do número de operações mais críticas, isto é, operações que não podem parar de funcionar ou que não podem perder os dados, verificase um acréscimo do tempo de execução e por conseqüência o desempenho através dos dispositivos de *hardware* programável mais *software* pode ser insatisfatório. Devido a este motivo, são utilizados os dispositivos com *hardware* fixo para conseguir um aumento satisfatório da velocidade de algumas operações ou aplicações.

Entretanto, apesar das deficiências, os dois paradigmas possuem suas aplicações mais indicadas e recomendadas. Para escolher uma delas irá depender das características de cada projeto.

Existe ainda a necessidade de que haja um desenvolvimento de novos modelos e tipos de implementações de soluções computacionais. Devido a este fato, necessita-se de um novo tipo de implementação intermediária entre as tradicionais soluções em *hardware* fixo e *software* (*Hardware* Programável mais *Software*). Com o uso desse novo tipo de implementação computacional, será possível alcançar ou aproximar o desempenho das soluções implementadas em *hardware* fixo e da flexibilidade das soluções implementadas em *hardware* programável e *software* (SILVA MARTINS et al., 2005).

Então, surge a terceira forma intermediária para implementar soluções de reconfiguração de *hardware* chamadas de Arquiteturas Reconfiguráveis. Com o uso desse novo tipo de implementação computacional, é possível aproximar ou até mesmo alcançar o desempenho das soluções implementadas em *hardware* fixo com uma flexibilidade similar àquela encontrada nas soluções implementadas em *hardware* programável por *software* (SILVA MARTINS et al., 2005).

As soluções baseadas em arquiteturas reconfiguráveis agregam o desempenho de um *hardware* fixo com a flexibilidade de um *hardware* programável, solucionando problemas mais complexos.

## 3.2 Definições da Computação Reconfigurável

A Computação Reconfigurável é uma solução intermediária entre as soluções de *hardware* e *software*, associada a uma melhor flexibilidade, generalidade, eficiência, custo e um desempenho que não chega a ser igual a de um processador de propósito geral, mas se aproxima. Outro fato importante que deve ser mencionado, é que este tipo de solução requer menos potência e consequentemente o consumo de energia é menor do que nas soluções de *hardware* fixo onde a potência é maior.

Dentre os motivos necessários para estudar a computação reconfigurável, destacam-se os seguintes:

- Demanda computacional das aplicações;

- Inadequação de alguns modelos e estilos de computação atuais em termos de desempenho e flexibilidade;

- Posição e interesse das principais empresas e universidades do mundo;

- Evolução dos dispositivos computacionais em termos de arquitetura e tecnologia.

Na Computação Reconfigurável, os agentes de *hardware* de propósito geral são configurados para executar tarefas específicas, podendo também serem reconfigurados sob demanda para realizar outras tarefas específicas em alguns casos (RECCONFIG-URABLE, 2007).

A Computação Reconfigurável também pode ser considerado como um paradigma da computação, no qual circuitos integrados programáveis são utilizados juntamente com *software* para reconfigurar dinamicamente dispositivos lógicos programáveis chamados de FPGA - (*Field Programmable Gate Array*) (STAR BRIDGE SYSTEMS, 2007). Onde os FPGAs são dispositivos lógicos programáveis compostos por uma matriz de blocos lógicos, programáveis cercada de blocos de entrada e saída, e conectada por fios de interconexão também programáveis (MESQUITA, 2002).

A Computação Reconfigurável teve início na década de 60 (ESTRIN, 1960)(ESTRIN, 2002), porém apenas há pouco tempo começavam a surgir novas tecnologias que proporcionaram a sua implementação e aplicação na prática. O interesse deste novo paradigma começou no início dos anos 90 quando o número de portas lógicas dos FPGAs ultrapassou dez mil (GUCCIONE, 2001). A partir daí a Computação Reconfigurável, com a possibilidade de aumentar a velocidade de muitas aplicações, tornou-se um objeto de investigação intensiva. A característica mais importante é a capacidade de realizar computações em *hardware* com o objetivo de incrementar o desempenho, ficando ao mesmo tempo com a flexibilidade do *software* (COMPTON; HAUCK, 2002). Com a finalidade de atingir um desempenho elevado e suportar um conjunto enorme de aplicações, os sistemas reconfiguráveis são formados normalmente pela lógica reconfigurável e um processador de uso geral.

Para que se consiga executar a aplicação de uma maneira mais eficiente, aquelas partes que não são facilmente mapeadas na lógica reconfigurável são executadas em um processador hospedeiro, enquanto que as outras partes que necessita de uma computação muito intensiva e que podem se beneficiar da sua implementação de *hardware*, são executadas nos FPGAs como é mostrado na Figura 3.1 a estrutura de um sistema reconfigurável.

Figura 3.1: Estrutura de um Sistema Reconfigurável com Processador Hospedeiro (SKLIAROVA, 2004)

## 3.3 Dispositivos Lógicos Programáveis - FPGAs

Com o surgimento de novos tipos de dispositivos lógicos programáveis, os projetos de sistemas digitais, tiveram muitas alterações nas últimas décadas. Atualmente, uma quantidade considerável de sistemas digitais são implementados com o auxílio destes dispositivos com elevada densidade.

Com o crescimento atual do mercado, uma variedade enorme de dispositivos, está surgindo. Entretanto, esses dispositivos se diferem uns dos outros pelas características da tecnologia de programação e também pela granularidade dos principais elementos lógicos.

O FPGA é um dispositivo semicondutor que contém componentes básicos programáveis e interconexões programáveis. Estes componentes lógicos podem ser programados para expandir a funcionalidade de portas lógicas básicas (tais como portas AND, OR, XOR, etc.) ou funções combinatórias mais complexas, como decodificadores ou funções matemáticas.

Em muitos FPGAs, estes componentes lógicos programáveis (ou blocos lógicos, ou células) também incluem elementos de memória, que podem ser simples flip-flops ou módulos de memória completos.

Uma hierarquia de interconexões programáveis permite aos blocos lógicos de um FPGA serem interconectados pelo projetista do sistema como necessário. Estes blocos lógicos e interconexões podem ser programados de maneira tal que o FPGA pode executar qualquer função lógica (DUARTE, 2006).

### 3.3.1 Arquitetura de um FPGA

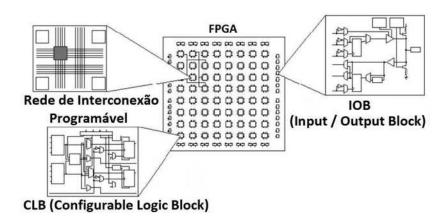

Um FPGA é formada por um arranjo de células configuráveis (ou blocos lógicos) contidos em um único *chip*. Cada uma dessas células, contém certa capacidade computacional para implementar funções lógicas e/ou realizar o roteamento para permitir a comunicação entre células. Essas operações podem acontecer simultaneamente no arranjo das células (BROWN; ROSE, 1996).

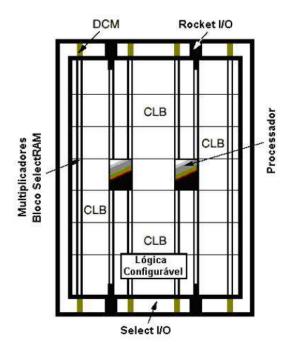

A arquitetura básica de um FPGA, ilustrada na Figura 3.2 (BROWN; ROSE, 1996), é composta por matrizes de blocos lógicos programáveis, cercadas de blocos de entrada e saída, sendo conectadas por fios programáveis de interconexão também programáveis (MESQUITA, 2002). Alguns FPGAs podem ter suas funções lógicas reprogramadas dinamicamente, através do envio de pacotes de *bitstream*.

A comunicação entre blocos é feita através dos recursos de interconexão. A borda externa do arranjo consiste de blocos especiais, capaz de realizar operações de entrada e saída (E/S). Atualmente, no mercado há um elevado número de tipos de arquiteturas de FPGAs. Por esse motivo, são definidos três principais aspectos para a arquitetura de uma FPGA, como:

- Tecnologia de programação;

- Arquitetura das células;

- Estrutura de roteamento.

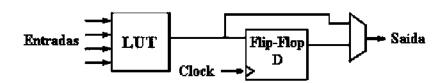

Estes aspectos influenciam diretamente no desempenho e densidade das diferentes arquiteturas de FPGA. Entretanto, não se pode afirmar que há uma melhor arquitetura, e sim a mais adequada para uma determinada aplicação. Genericamente, uma célula de FPGA típica é composta de uma LUT - (*Look-up Table*) de 4-entradas e um *flip-flop* como é ilustrado na Figura 3.3.

Figura 3.2: Estrutura Básica de um FPGA (BROWN; ROSE, 1996)

Figura 3.3: Célula Genérica da Maioria dos FPGAs (BROWN; ROSE, 1996)

No caso da célula da Figura 3.3, existe apenas uma saída, que pode ser a saída direta da *LUT* ou a saída vinda do registrador. A célula possui 4 entradas para a LUT e uma entrada de *clock*. A disposição das entradas e da saída da célula é ilustrada na Figura 3.4.

Figura 3.4: Localização das Entradas e Saídas de uma Célula (BROWN; ROSE, 1996)

Cada entrada é acessível de um lado da célula, enquanto que o pino de saída pode se conectar aos fios de roteamento em ambos os canais, à direita e abaixo da célula. Cada pino de saída da célula por sua vez pode conectar a qualquer um dos segmentos dos canais adjacentes a ele. A Figura 3.5 ilustra esta situação.

A arquitetura genérica de um FPGA consiste em uma cadeia de células e canais de roteamento, conforme mostra a Figura 3.6. Geralmente, todos os canais de roteamento

Figura 3.5: Ligação do Pino de Saída aos Segmentos do Canal de Roteamento (BROWN; ROSE, 1996)

possuem o mesmo comprimento, isto é, números de fios. Algumas arquiteturas possuem além da rede de roteamento, linhas globais que provêm conexões de alta velocidade, com poucos desvios, para todas as células da matriz da FPGA, suprindo sinais como clock, resets e outros tipos de sinais globais.

A implementação da célula ilustrada na Figura 3.6 não é única. Existem várias outras propostas de arquitetura, onde as células implementam lógicas de maior complexidade, tais como unidades lógicas aritméticas (ULAs), ou até mesmo núcleos de processamento completos como microprocessadores com módulos de memórias. Esta diferença no tamanho da célula é usualmente referida como granularidade.

Figura 3.6: Estrutura Genérica de um FPGA (COMPTON; HAUCK, 2002)

#### 3.3.2 Vantagens e Desvantagens dos FPGAs

#### Vantagens:

- Ter uma arquitetura flexível que possibilita a utilização em muitas aplicações;

- Conseguem unificar várias estruturas heterogêneas como: blocos de memória, que permite a implementação de sistemas completos em um único encapsulamento;

- O consumo de energia é uma vantagem muito importante em alguns sistemas. Os FPGAs são dispositivos baseados em PROM, EPROM e SRAM onde requerem menos potência que os dispositivos baseados em EEPROM e FLASH, que necessitam de maior potência e com isso ocorre um consumo maior.

#### **Desvantagens:**

- Tempo de configuração: é o tempo para carregar uma configuração no FPGA, sendo um fator que pode ser um impecílho para sua utilização em sistemas dinamicamente reconfiguráveis;

- Compatibilidade em relação a novos dispositivos: para obter benefícios de uma nova família de FPGAs, os sistemas desenvolvidos devem ser resintetizados e muitas vezes até mesmo reescritos;

- Restrições de tamanho: atualmente os FPGAs disponíveis no mercado somente permitem que sejam implementados núcleos de tamanho limitado e consequentemente as funcionalidades disponíveis nos dispositivos se tornam pequenas;

- Tempo de compilação: no caso as tarefas de síntese, roteamento e posicionamento consomem muito mais tempo que a compilação de *software* dos processadores de propósito geral (MESQUITA, 2002).

#### 3.3.3 Classificação dos FPGAs

Atualmente, os FPGAs apresentam um número considerável de arquiteturas, tendo cada fabricante implementado um modelo próprio. Existe, no entanto, vários pontos comuns entre as diversas arquiteturas, sendo por isso possível agrupá-las tendo em consideração certas características.

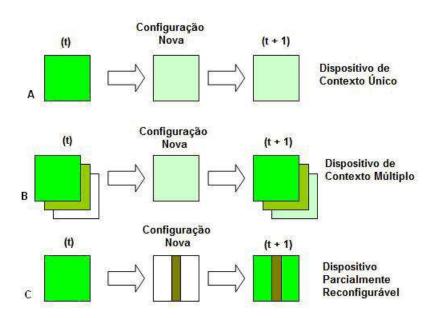

Uma das possibilidades de classificação dos FPGAs, é apresentado na Figura 3.7, com relação aos modos de configuração que pode ser realizado neste tipo de arquitetura. A classificação pode ser configurável ou reconfigurável, reconfigurável estático ou dinâmico (SANCHEZ et al., 1999) e o dinâmico pode ser parcial ou total (GERICOTA et al., 2003).

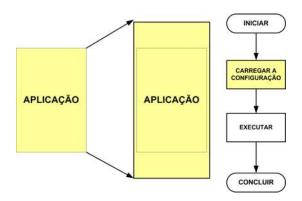

**A Reconfiguração Estática:** o funcionamento do FPGA ocorre permanentemente, após ser configurada conforme Figura 3.8. Certamente, o modo estático não proporciona grande flexibilidade, mas permite um bom desempenho através da utilização do *hardware* otimizado para qualquer aplicação (SKLIAROVA; FERRARI, 2001).

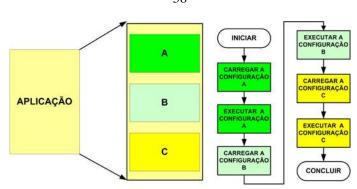

A Reconfiguração Dinâmica: algumas vezes é necessário ativar configurações diferentes de acordo com a necessidade de uma aplicação. Certamente isto acarretará mais seções de aplicação a serem mapeadas em *hardware* do que poderá caber em uma FPGA. Contudo, grande parte da aplicação pode ser acelerada em um sistema reconfigurável, conseguindo assim um desempenho mais alto.

Figura 3.7: Classificação das FPGAs em Função dos Modos de Configuração (GERICOTA et al., 2003)

Figura 3.8: Reconfiguração Estática (SKLIAROVA; FERRARI, 2001)

Este termo é chamado de reconfiguração dinâmica a que está agregada a noção de *hardware* virtual. Neste caso, os recursos disponíveis no FPGA são bastante menores que o conjunto de recursos necessários para todas as configurações. Mas em vez de reduzir o número de configurações mapeadas, estas são transferidas para o FPGA de acordo com a necessidade atual (COMPTON; HAUCK, 2002).

Uma das vantagens dos sistemas reconfiguráveis dinamicamente comparando-os com os sistemas programáveis só no início da aplicação, é a potencialidade de efetuar otimizações do *hardware* com base na informação determinada durante a execução.

Outros termos atualmente encontrados na literatura que se referem à Reconfiguração Dinâmica são *Run-Time Reconfiguration - RTR*, *Real-Time Reconfiguration*, *On-The-Fly Reconfiguration* e *In-Circuit Reconfiguration*. Todas essas expressões podem ser traduzidas também como reconfiguração em tempo de execução (LYSAGHT; DUNLOP, 1993).

A **Reconfiguração Dinâmica** pode ser dividida em: Reconfiguração Global e Reconfiguração Parcial.

A **Reconfiguração Global** é quando uma reserva de todos os recursos de *hardware* é feita para cada fase de execução. Depois que uma fase é concluída, todos os recursos da FPGA são reconfigurados para uma próxima fase ilustrado na Figura 3.9.

Figura 3.9: Reconfiguração Dinâmica Global (SKLIAROVA; FERRARI, 2001)

Os FPGAs são classificados como dinamicamente reconfiguráveis, se seus circuitos internos de armazenamento da configuração podem ser atualizados seletivamente, sem prejudicar o funcionamento da lógica restante que pode estar em operação. Estes dispositivos podem assim ser reconfigurados seletivamente enquanto estiverem ativos.

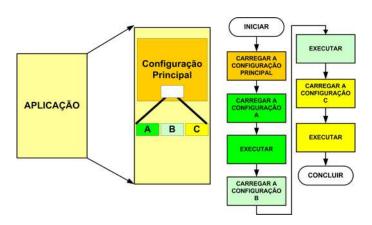

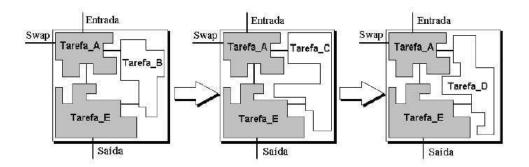

A **Reconfiguração Parcial** é quando acontece a modificação seletiva dos recursos de *hardware* ao longo da execução de uma aplicação, ilustrada na Figura 3.10. Esta flexibilidade permite que o *hardware* seja mais personalizado com relação às necessidades correntes da aplicação. Esta reconfiguração exige que só os recursos selecionados sejam reprogramados, o que resulta em um *overhead* de configuração menor do que no caso anterior.

Um dispositivo é definido como reconfigurável parcialmente se é possível reconfigurá-lo seletivamente, enquanto o resto do dispositivo permanece inativo, mas retém sua configuração. Caso o dispositivo só possa ser reconfigurado por completo, mesmo que na própria placa do sistema, ou fora dela como com dispositivos EPROMs, ele é considerado apenas reconfigurável, pois, não permanece ativo em nenhum dos casos, por não permitir configuração seletiva (LYSAGHT; DUNLOP, 1993).