# Uma Metodologia de Verificação Funcional para Circuitos Digitais

## Karina Rocha Gomes da Silva

Tese de Doutorado submetida à Coordenação dos Cursos de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Campina Grande como parte dos requisitos necessários para obtenção do grau de Doutor em Ciências no domínio da Engenharia Elétrica.

Área de Concentração: Processamento da Informação

Prof. Elmar Uwe Kurt Melcher Dr.

(Orientador)

Prof. Wolfgang Rosenstiel Dr.

(Co-Orientador)

Campina Grande, Paraíba, Brasil ©Karina Rocha Gomes da Silva, Fevereiro de 2007

## **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

#### Resumo

O advento das novas tecnologias VLSI e metodologias de projetos de *System On a Chip* (SoC) têm trazido um crescimento explosivo à complexidade dos circuitos eletrônicos. Como um resultado desse crescimento, a verificação funcional tem se tornado o maior gargalo no fluxo de projetos de hardware. Assim, novos métodos são requeridos para permitir que a verificação funcional seja realizada de forma mais rápida, fácil e que permita uma maior reusabilidade.

Esse trabalho propõe a criação de uma nova metodologia para verificação funcional de componentes digitais integráveis, que permite o acompanhamento do fluxo de projeto, de forma que o testbench (ambiente de simulação) seja gerado antes da implementação do dispositivo sendo verificado (*Design Under Verification* - DUV), tornando o processo de verificação funcional mais rápido e o testbench mais confiável, devido a ele ser verificado antes do início da verificação funcional do DUV.

#### **Abstract**

The advent of new VLSI technology and SoC design methodologies, has brought an explosive growth in the complexity of modern electronic circuits. As a result, functional verification has become the major bottleneck in any design flow. New methods are required that allow for easier, quicker and more reusable verification.

In this work is proposed a novel functional verification methodology to digital components, which follows the project flow, allowing the testbench (simulation environment) to be generated before the Design Under verification implementation. In this way, the functional verification process become faster and the verification engineer can trust in the testbench, because it is verified before the DUV's functional verificationDUV.

# Conteúdo

| 1                         | Intr | odução   |                                 | 1  |

|---------------------------|------|----------|---------------------------------|----|

|                           | 1.1  | Motiva   | ação e contexto                 | 1  |

|                           |      | 1.1.1    | Especificação do hardware       | 2  |

|                           |      | 1.1.2    | Especificação da verificação    | 3  |

|                           |      | 1.1.3    | Implementação do testbench      | 4  |

|                           |      | 1.1.4    | Implementação RTL               | 5  |

|                           |      | 1.1.5    | Verificação Funcional           | 5  |

|                           |      | 1.1.6    | Síntese                         | 6  |

|                           |      | 1.1.7    | Simulação pós-síntese           | 6  |

|                           |      | 1.1.8    | Prototipação                    | 6  |

|                           | 1.2  | Declar   | ração do problema               | 6  |

|                           | 1.3  | Organi   | ização                          | 8  |

| 2                         | Con  | ceitos d | le Verificação Funcional        | 10 |

|                           | 2.1  | Dispos   | sitivo a ser verificado         | 10 |

|                           | 2.2  | Tipos o  | de verificação                  | 11 |

|                           |      | 2.2.1    | Verificação estática            | 11 |

|                           |      | 2.2.2    | Verificação dinâmica            | 11 |

|                           |      | 2.2.3    | Verificação híbrida             | 12 |

| 2.3 Verificação funcional |      | Verific  | ação funcional                  | 12 |

|                           |      | 2.3.1    | Black-box, grey-box e white-box | 14 |

|                           |      | 2.3.2    | Testbench                       | 15 |

|                           |      | 2.3.3    | Cobertura                       | 17 |

|                           |      | 2.3.4    | Geração de estímulos            | 22 |

|   | 2.4  | Systen   | 1C                                                               | 26 |

|---|------|----------|------------------------------------------------------------------|----|

|   | 2.5  | Consid   | lerações sobre conceitos de verificação funcional                | 29 |

| 3 | Met  | odologia | a VeriSC                                                         | 30 |

|   | 3.1  | Constr   | ução do testbench                                                | 30 |

|   |      | 3.1.1    | Templates                                                        | 32 |

|   |      | 3.1.2    | Source                                                           | 42 |

|   |      | 3.1.3    | DUV (Design Under Verification)                                  | 47 |

|   |      | 3.1.4    | TDriver                                                          | 47 |

|   |      | 3.1.5    | Reset_driver                                                     | 50 |

|   |      | 3.1.6    | TMonitor                                                         | 52 |

|   |      | 3.1.7    | Checker                                                          | 53 |

|   |      | 3.1.8    | Arquivo de estrutura                                             | 54 |

|   |      | 3.1.9    | Modelo de Referência                                             | 55 |

|   |      | 3.1.10   | FIFO Buffer (First In First Out)                                 | 57 |

|   |      | 3.1.11   | Pré-source                                                       | 57 |

|   |      | 3.1.12   | Sink                                                             | 57 |

|   | 3.2  | Metod    | ologia                                                           | 57 |

|   |      | 3.2.1    | Testbench para o DUV completo (primeiro passo)                   | 59 |

|   |      | 3.2.2    | Decomposição hierárquica do Modelo de Referência (segundo passo) | 61 |

|   |      | 3.2.3    | Testbench para cada bloco do DUV (terceiro passo)                | 62 |

|   |      | 3.2.4    | Substituição do DUV completo (último passo)                      | 64 |

|   | 3.3  | Cobert   | ura funcional                                                    | 65 |

|   |      | 3.3.1    | Exemplo de descrição do modelo de cobertura                      | 67 |

|   |      | 3.3.2    | Biblioteca BVE-COVER                                             | 68 |

|   | 3.4  | Resum    | no da metodologia VeriSC                                         | 73 |

| 4 | Resi | ıltados  |                                                                  | 76 |

|   | 4.1  | Resulta  | ados da metodologia tradicional VeriSC1                          | 76 |

|   |      | 4.1.1    | Decodificador MP3                                                | 77 |

|   |      | 4.1.2    | Decodificador MPEG4                                              | 78 |

|   | 4.2  | Resulta  | ados da metodologia VeriSC                                       | 80 |

|   |      | 4.2.1     | Decodificador de Bitstream                                    | 80  |

|---|------|-----------|---------------------------------------------------------------|-----|

|   |      | 4.2.2     | Resultados obtidos nos cursos de verificação                  | 82  |

|   |      | 4.2.3     | Resultados obtidos com o projeto DigiSeal                     | 83  |

|   | 4.3  | Resulta   | ados obtidos com biblioteca BVE-COVER                         | 86  |

|   |      | 4.3.1     | Experimentos                                                  | 87  |

| 5 | Con  | clusão    |                                                               | 89  |

|   | 5.1  | Contrib   | puições                                                       | 89  |

|   | 5.2  | Traball   | nos futuros                                                   | 90  |

| A | еТВ  | c tool: A | A Transaction Level Testbenches Generator                     | 96  |

|   | A.1  | Introdu   | action                                                        | 96  |

|   | A.2  | VeriSC    | 2 Methodology                                                 | 97  |

|   |      | A.2.1     | The testbench implementation steps                            | 99  |

|   | A.3  | еТВс Т    | Cool                                                          | 102 |

|   |      | A.3.1     | eTBc tool implementation                                      | 104 |

|   | A.4  | Results   | 8                                                             | 104 |

| В | Ana  | lysis ab  | out VeriSC2 methodology taking in account VSI Alliance patter | n   |

|   | repo | rt        |                                                               | 107 |

|   | B.1  | Function  | onal Verification Deliverables                                | 107 |

|   |      | B.1.1     | Documentation                                                 | 108 |

|   |      | B.1.2     | Testbench                                                     | 108 |

|   |      | B.1.3     | Drivers                                                       | 109 |

|   |      | B.1.4     | Monitors                                                      | 110 |

|   |      | B.1.5     | Assertions                                                    | 110 |

|   |      | B.1.6     | Functional Coverage                                           | 110 |

|   |      | B.1.7     | Code Coverage                                                 | 111 |

|   |      | B.1.8     | Formal Methods                                                | 112 |

|   |      | B.1.9     | Documentation                                                 | 112 |

|   |      | B.1.10    | Behavioural Models                                            | 113 |

|   |      | B.1.11    | Behavioural Models for Memory                                 | 114 |

|     | B.1.12   | Detailed Behavioural Models for I/O Pads                    | 14 |

|-----|----------|-------------------------------------------------------------|----|

|     | B.1.13   | Stimulus                                                    | 14 |

|     | B.1.14   | Scripts                                                     | 14 |

|     | B.1.15   | Stub Model                                                  | 14 |

|     | B.1.16   | Functional Verification Certificate                         | 14 |

| B.2 | Reuse o  | of Functional Verification Deliverables in SoC Verification | 14 |

|     | B.2.1    | DUV Re-Verification                                         | 15 |

|     | B.2.2    | DUV Re-Verification in a SoC                                | 15 |

| B.3 | Function | onal Verification Deliverables Rules                        | 15 |

|     | B.3.1    | Drivers                                                     | 15 |

|     | B.3.2    | Monitors                                                    | 16 |

|     | B.3.3    | Assertions                                                  | 17 |

|     | B.3.4    | Functional Coverage                                         | 17 |

|     | B.3.5    | Code Coverage                                               | 18 |

|     | B.3.6    | Formal Methods                                              | 18 |

|     | B.3.7    | Documentation                                               | 18 |

|     | B.3.8    | Behavioural Models                                          | 18 |

|     | B.3.9    | Scripts                                                     | 18 |

|     | B.3.10   | Stub Model                                                  | 19 |

|     | B.3.11   | Functional Verification Certificate                         | 19 |

## Lista de Símbolos

BFM - Bus-functional model

DUV - Design Under Verification

IP - Intellectual property

OSCI - Open SystemC Initiative

RTL - Register Transfer Level

SBCCI - Symposium on Integrated Circuits and Systems Design

SCV - SystemC Verification Library

SDL - Specification Description Language

SOC - System on a chip

TLM - Transaction Level Modelling

TLN - Transaction Level Netlist

VHDL - VHSIC Hardware Description Language

HDL - Hardware Description Language

VLSI - Very Large Scale Integration

FIFO - First In First Out

eTBc - Easy Testbench Creator

VSIA - VSI Alliance

BVE-COVER - Brazil-IP Verification Extension

COMET - Coverage measurement tool

# Lista de Figuras

| 1.1  | Etapas para o desenvolvimento de hardware                        | 2  |

|------|------------------------------------------------------------------|----|

| 2.1  | Diagrama de projeto                                              | 13 |

| 2.2  | Esquema de um testbench genérico                                 | 15 |

| 2.3  | Fluxo de projeto do trabalho de Hu                               | 27 |

| 2.4  | Diagrama de blocos do <i>testbench</i> do trabalho de Randjic    | 28 |

| 3.1  | Diagrama do testbench da metodologia VeriSC                      | 31 |

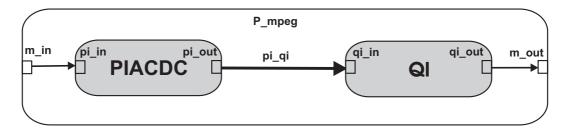

| 3.2  | Exemplo de um DUV ( <i>P_mpeg</i> ) formado por parte do MPEG4   | 32 |

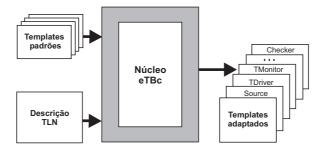

| 3.3  | Esquema da ferramenta eTBc                                       | 34 |

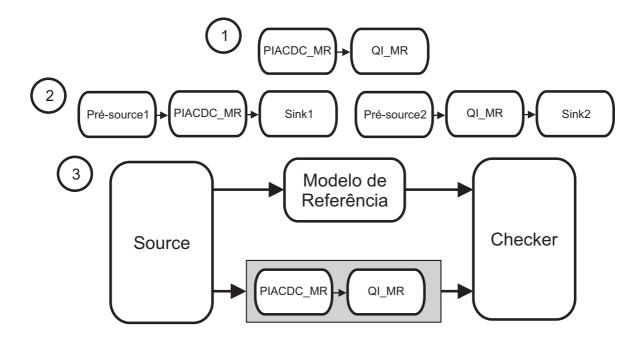

| 3.4  | Exemplo da divisão do <i>P_mpeg</i> em blocos                    | 59 |

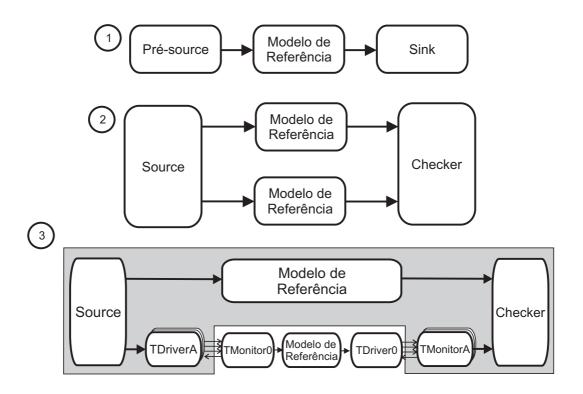

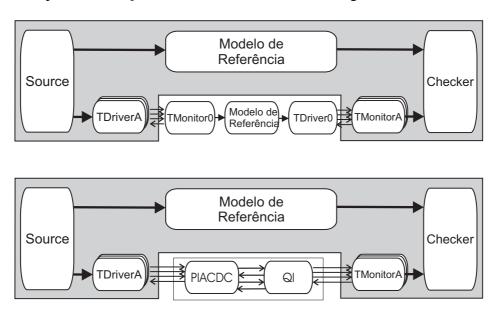

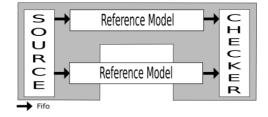

| 3.5  | Testbench para o DUV completo (primeiro passo)                   | 60 |

| 3.6  | Substituição do DUV por TMonitor, Modelo de Referência e TDriver | 61 |

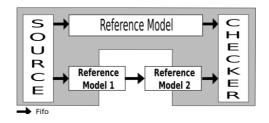

| 3.7  | Decomposição hierárquica do Modelo de Referência (segundo passo) | 62 |

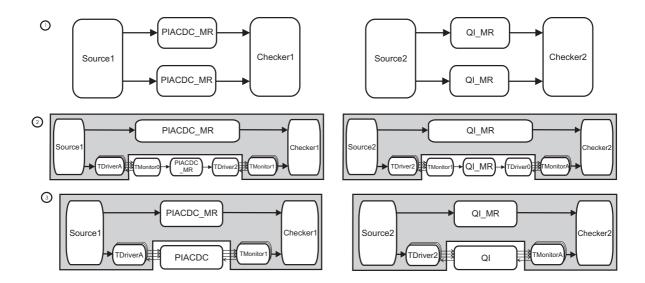

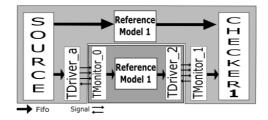

| 3.8  | Testbenches para cada bloco do DUV: PIACDC e QI (terceiro passo) | 63 |

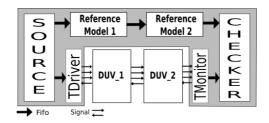

| 3.9  | Substituição do DUV completo (último passo)                      | 64 |

| 3.10 | Locais para medir cobertura funcional                            | 66 |

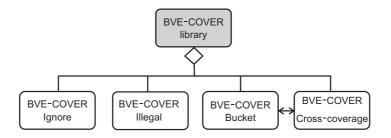

| 3.11 | Componentes da biblioteca de cobertura BVE-COVER                 | 69 |

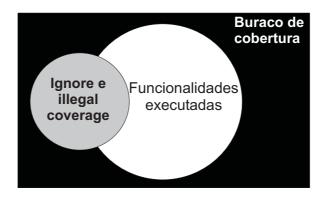

| 3.12 | Análise do buraco de cobertura                                   | 72 |

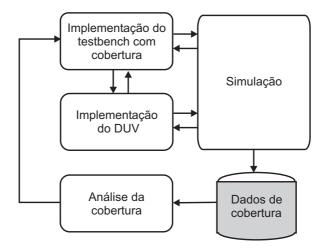

| 3.13 | Fluxo de verificação                                             | 73 |

| 3.14 | Fluxo de cobertura                                               | 75 |

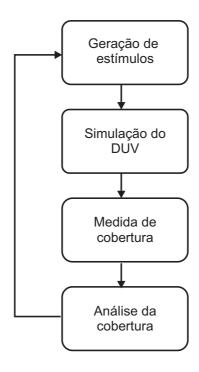

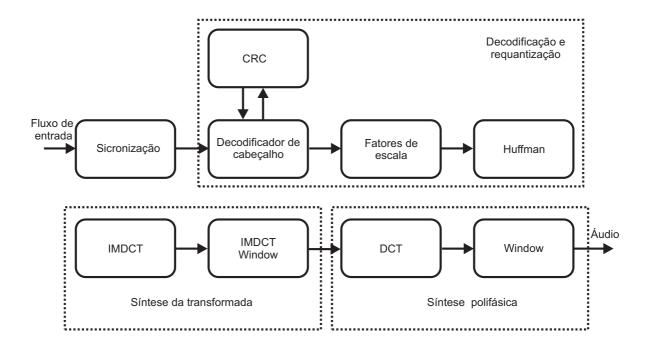

| 4.1  | Decodificador MP3                                                | 78 |

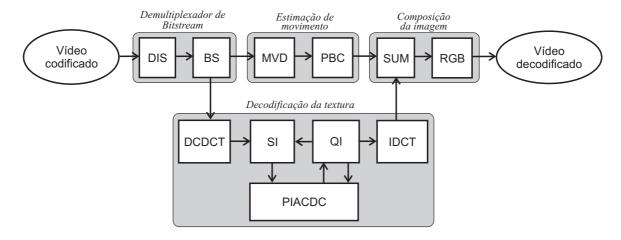

| 4.2  | Decodificador MPEG4                                              | 79 |

| 43   | Bloco esquemático do DigiSeal                                    | 84 |

| 4.4 | Comparação entre DigiSeal e MPEG4                   | 85  |

|-----|-----------------------------------------------------|-----|

| 4.5 | Gráfico do overhead da biblioteca de cobertura      | 88  |

| A.1 | General Testbench schema                            | 98  |

| A.2 | Testing Source and Checker                          | 99  |

| A.3 | Testbench construction for the top level DUV        | 100 |

| A.4 | Hierarchical decomposition of the RM                | 101 |

| A.5 | Testbench implementation for module DUV_1           | 101 |

| A.6 | Replace the top level DUV (Last Step)               | 102 |

| A.7 | eTBc tool - architecture diagram                    | 103 |

| B.1 | Testbench to functional verification according VSIA | 109 |

| B.2 | Testbench to functional verification                | 109 |

## Lista de Tabelas

| 3.1 | Modelo de cobertura                                                     | 68  |

|-----|-------------------------------------------------------------------------|-----|

| 4.1 | Comparação entre metodologia VeriSC e metodologia tradicional VeriSC1 . | 82  |

| 4.2 | Comparação entre DigiSeal e MPEG4                                       | 84  |

| A.1 | 3MBIP Features                                                          | 106 |

## Capítulo 1

## Introdução

Esse trabalho é apresentado como uma contribuição para a área de circuitos integrados digitais. Especificamente, o trabalho aborda o tema de verificação de circuitos digitais síncronos, utilizando a técnica de verificação funcional, realizada através de simulação.

O foco do trabalho consiste em introduzir uma nova metodologia de verificação funcional de circuitos digitais integrados, denominada VeriSC.

De acordo com alguns autores [5; 29] a fase de verificação consiste em cerca de 70% de todos os recursos do projeto. Portanto, uma proposta de fluxo de projeto que não leve em consideração as necessidades da verificação como uma fase prioritária, pode se mostrar bastante inadequada. Nesse contexto, o trabalho aqui apresentado, vem contribuir apresentando uma proposta que priorize as necessidades da fase de verificação, de forma a torná-la mais rápida e confiável na eliminação de erros do projeto.

O restante desse capítulo é apresentado da seguinte forma: situar e motivar o trabalho de verificação dentro de um projeto de implementação de hardware; declarar o problema abordado nesse trabalho e dar uma visão geral de como se encontra estruturado o restante do documento.

## 1.1 Motivação e contexto

A implementação de um *Intellectual Property core* (IP core) consiste na criação de um componente de hardware que desempenhe uma determinada funcionalidade. Esse componente deve permitir a integração em um ambiente onde ele possa interagir com os demais compo-

nentes para formar um sistema.

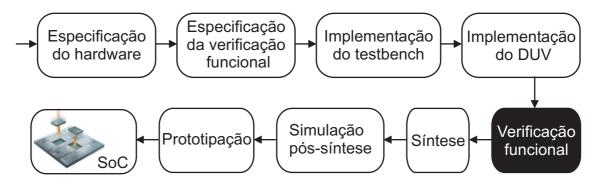

Para que essa integração seja possível, é necessário que esse IP core contenha a menor quantidade de falhas possível. Essa confiabilidade vai depender de como é realizado o processo de geração do produto final. Esse processo é composto de fases. Não se tem um consenso entre os trabalhos da área sobre os elementos conceituais de cada fase. Nem mesmo a delimitação de cada fase vem a estabelecer um consenso. No entanto, para que o leitor possa se orientar com relação ao processo de desenvolvimento de hardware e possa contextualizar o trabalho de verificação aqui relatado, serão descritas as fases necessárias para a obtenção do hardware, de acordo com os conceitos adotados para a realização desse trabalho. Essas fases são mostradas na Figura 1.1.

Figura 1.1: Etapas para o desenvolvimento de hardware

#### 1.1.1 Especificação do hardware

Várias fases precedem a implementação de um código *Register Transfer Level* (RTL). Em particular, é necessário obter uma descrição completa do que se deseja construir, denominada de especificação do hardware.

A especificação do hardware é fundamental para o entendimento das necessidades do dispositivo a ser desenvolvido. Nessa fase são estudados todos os requisitos do mesmo. Tais requisitos são documentados, através da definição exata de cada funcionalidade que o hardware final deve executar. Essa especificação pode ser feita em um documento texto inicialmente. Existe a possibilidade de se construir uma especificação executável a partir dessa especificação em formato de texto.

A especificação deve ter um alto nível de abstração, no qual ainda não tenham

sido tomadas decisões em relação à implementação das funcionalidades, em termos da arquitetura-alvo a ser adotada, nem sobre os componentes de hardware ou software a serem selecionados. Ela contém detalhes de alto nível, tais como funcionalidades a serem executadas, bem como informações de baixo nível, tais como especificação e descrição de pinos a serem usados.

É necessário que a especificação do hardware seja realizada por alguém que conheça os detalhes da aplicação visada. Normalmente quem faz essa especificação é o engenheiro de projeto. Outro fator importante é que qualquer mudança que ocorra dentro dessa especificação deve ser repassada para a especificação da verificação.

#### 1.1.2 Especificação da verificação

A especificação da verificação é muito importante para guiar o processo de verificação de um dispositivo. É nessa especificação onde são documentados os aspectos importantes que devem ser verificados em um determinado dispositivo. Todas as funcionalidades devem ser consideradas. O documento deve ser feito em formato de texto e normalmente quem faz essa especificação é o engenheiro de verificação, mas todos os participantes do projeto devem ser consultados. O plano de cobertura faz parte da especificação da verificação.

O plano de verificação é um conjunto de documentos que fornece os objetivos, componentes e detalhes da verificação. Esse plano é uma parte crítica para obter o sucesso durante a verificação. Tal plano precisa lidar com uma gama de questões, indo desde objetivos de alto-nível até a identificação e documentação de variáveis. O plano de verificação também serve como uma especificação funcional para o ambiente de verificação, tal como o estabelecimento de quais os tipos de estímulos que serão utilizados para a verificação do projeto. Esse plano deve ser dinâmico e refletir o estado presente do projeto. Ele deve ser revisto e atualizado sempre que algo for mudado no projeto, até mesmo após um novo erro ter sido encontrado.

É importante que os pontos críticos dentro do projeto sejam discutidos por todos os membros da equipe, que esses pontos sejam definidos como críticos (*corner cases*) e que seja dada uma atenção especial para cada um desses pontos, pois eles podem ser fortes candidatos a apresentarem erros na verificação.

A parte do plano que trata da cobertura é responsável por determinar parâmetros de

medição para o progresso da simulação. Esses parâmetros devem ser estabelecidos pela equipe de verificação, levando-se em consideração quais as funcionalidades importantes que devem ser executadas durante a simulação e qual o tipo de cobertura será realizada para melhor poder constatar que essas funcionalidades foram efetivamente simuladas.

#### 1.1.3 Implementação do testbench

O testbench é o ambiente através do qual o dispositivo a ser verificado (*Design Under Verification* - DUV) será inserido, de forma que ele receba estímulos e que as respostas sejam comparadas com o resultado ideal.

O testbench deve ser implementado preferencialmente em um nível alto de abstração, o qual é denominado de nível de transação (*Transaction-level*). Esse nível de transação não se preocupa com detalhes de protocolos no nível de sinais. Ao invés disso, o seu foco é na comunicação entre blocos e na transferência de transações.

Uma transação é uma representação básica para a troca de informações entre dois blocos funcionais. Em outras palavras, é uma operação que inicia num determinado momento no tempo e termina em outro, sendo caracterizada pelo conjunto de instruções e dados necessários para realizar a operação. Um exemplo de uma transação poderia ser uma transmissão de um pacote ethernet. Ela é definida pelo seu tempo inicial, tempo final e atributos [7]. Uma transação pode ser simples como uma leitura de memória ou complexa como a transferência de um pacote inteiro de dados através de um canal de comunicação.

O testbench se comunica com o DUV através de algum protocolo que consiga converter dados no nível de transação para dados no nível de sinais. O testbench deve ser composto de um módulo capaz de gerar os tipos de estímulos necessários para a verificação do DUV. Um bom testbench precisa comparar automaticamente o resultado vindo do DUV com o resultado ideal, que se encontra na especificação.

Um dos problemas que podem ocorrer na verificação funcional pode ser causado por erro de implementação do testbench. Por esse motivo, o testbench deve ser um ambiente com a quantidade mínima de erros. Sendo assim, é importante que seja realizada uma implementação bem feita do testbench.

#### 1.1.4 Implementação RTL

O código RTL é um código escrito em um nível mais baixo de abstração, o nível de sinais. Nesse nível, todas as operações são controladas por ciclos de relógios (*clocks*). Normalmente esse código é implementado em uma linguagem de descrição de hardware, tal como VHDL, Verilog, SystemC, entre outras.

A implementação RTL é o modelo que nas fases seguintes será convertido em hardware, por um procedimento em grande parte automatizado. Um aspecto importante que deve ser respeitado é que os erros precisam ser captados ainda no código RTL, pois quanto mais cedo erros forem detectados, menos recursos são gastos para a correção dos mesmos.

#### 1.1.5 Verificação Funcional

Verificação é algumas vezes confundido com outros termos. Para que não exista nenhuma dúvida com relação ao que venha ser a verificação funcional será adotado um conceito aceito pela comunidade de verificação e adotado na bibliografia. "Verificação funcional é um processo usado para demonstrar que o objetivo do projeto é preservado em sua implementação"[5]. A verificação funcional deve ser realizada através da comparação de dois modelos, o modelo sendo desenvolvido e o modelo ideal que reflete a especificação.

A verificação funcional é realizada através de simulação. Durante a simulação, são inseridos estímulos na entrada do DUV e esses estímulos são coletados em sua saída e comparados com os resultados esperados (resultados ideais). No trabalho aqui apresentado, essa comparação é feita automaticamente através da comparação dos resultados com um Modelo de Referência. O Modelo de Referência é uma implementação executável e por definição reflete a especificação.

Os estímulos devem ser escolhidos cuidadosamente, de forma que eles possam vir a exercitar as funcionalidades desejadas. A verificação somente está terminada quando todas as funcionalidades especificadas forem executadas. Essas funcionalidades estão documentadas no modelo de cobertura. Por isso, a verificação estará terminada somente quando todos os critérios de cobertura forem atingidos. Esse processo de dirigir os estímulos de acordo com a cobertura e determinar o término da simulação pelos critérios de cobertura é denominado de verificação dirigida por cobertura.

#### 1.1.6 Síntese

A síntese de RTL é realizada através da conversão de uma descrição RTL em um conjunto de registradores e lógica combinacional. Assim que o código RTL é sintetizado, é gerada uma *netlist* em nível de portas lógicas.

#### 1.1.7 Simulação pós-síntese

Assim que a síntese é realizada, é necessário fazer uma simulação que é denominada simulação pós-síntese. A partir de então, aspectos específicos do dispositivo, como por exemplo, atrasos das portas lógicas, passam a ser considerados durante a execução. Nessa fase, tanto aspectos de funcionalidade, quanto de tempo são levados em consideração durante a simulação.

A simulação pós-síntese é essencial para determinar se os requisitos de tempo são respeitados e se pode ser alcançada uma performance melhor do dispositivo, usando circuitos mais otimizados.

### 1.1.8 Prototipação

Vencida a etapa de simulação pós-síntese, pode-se passar para da prototipação. Essa etapa consiste na implantação do *netlist* gerado pela síntese em algum dispositivo de hardware.

A prototipação de um IP core digital é tipicamente feita em FPGA e pode adicionalmente ser feita em silício.

### 1.2 Declaração do problema

De acordo com o trabalho de Dueñas [13], 65% dos IP cores falham em sua primeira prototipação em silício e 70% destes casos são devidos a uma verificação funcional mal feita. Por isso, a qualidade de dispositivos e o tempo de desenvolvimento de um projeto dependem muito de como a verificação é realizada. Uma verificação incompleta resulta em uma qualidade ruim ou falha no dispositivo, o que vem a causar erros durante o seu uso. Além disso, qualquer problema funcional ou comportamental que escape da fase de verificação do

projeto poderá não ser detectado nas fases de prototipação e irá emergir somente depois que o primeiro silício esteja integrado no sistema alvo [8].

Outro grande problema a ser considerado é o reuso do IP core em outros projetos. É comum que empresas comprem um IP core pronto para integrar em seus projetos de SoC. O maior obstáculo do reuso é a confiabilidade. Os engenheiros têm dúvidas em incorporar em seus projetos, partes de outros projetos que eles não conheçam e/ou nas quais eles não confiem. No entanto, a confiabilidade não é algo que pode ser adicionado ao projeto no final dele. Essa confiabilidade precisa ser construída através de boas práticas de projeto. Essa confiabilidade pode também ser demonstrada através de um bom processo de verificação [5]

Com relação ao tempo de projeto, deve-se considerar que o tempo total de finalização de um projeto é muito significativo porque determina o momento de introdução do produto no mercado (*time to market*). Esse problema de tempo ocorre, em parte, devido ao engenheiro de verificação precisar esperar até que o engenheiro de projeto termine a implementação para iniciar a verificação. Isso faz com que aumente o tempo para que o projeto fique pronto.

Outro fator a ser considerado em um projeto é saber qual o momento em que a verificação do projeto está completa.

Na literatura, existem vários trabalhos relacionados com verificação. No entanto, a maioria deles aborda a verificação funcional parcialmente, sem conseguir englobar todos os aspectos necessários para realizar uma verificação funcional completa. Os trabalhos de [20], [3] e [25] introduzem técnicas para definir critérios de cobertura funcional. Os trabalhos de [28] e [22], definem formas de melhorar os vetores de testes. Esses trabalhos serão discutidos no Capítulo 2.

A declaração do nosso problema consiste de alguns pontos que podem ser assim resumidos:

a) A verificação funcional consome um esforço considerável, estimado em 70% dos recursos do projeto completo; b) Muitas vezes o testbench não é projetado para ser reusável; c) Algumas abordagens fazem a decomposição hierárquica do projeto sem considerar o processo de verificação funcional, causando um esforço extra para implementar o testbench e/ou mais testbenches precisam ser criados; d) A verificação começa somente quando todo o RTL hierárquico já foi implementado e e) Testbenches são depurados juntamente com o código RTL no momento da verificação funcional. Quando um erro aparece durante a si-

mulação, ele pode ser devido a um erro de implementação do código RTL, porém pode ser também um erro no testbench.

Um grande desafio vem da necessidade de adaptar o testbench para o dispositivo que está sendo verificado (DUV), porque o DUV normalmente é implementado sem considerar a verificação [5]. O DUV deve ser implementado de forma a facilitar o processo de verificação, pois o maior esforço de projeto se encontra exatamente na fase de verificação. Por esse motivo, o DUV deve ser adaptado ao ambiente de verificação. Uma forma para melhor adaptar o projeto ao *testbench* é criar o testbench antes da criação do projeto, dessa forma a verificação pode influenciar no fluxo de implementação do projeto.

Diante do exposto, a idéia central defendida nesse trabalho, pode ser declarada da seguinte forma:

Criação de uma metodologia de verificação funcional, para verificar componentes digitais síncronos, através da comparação do DUV com seu modelo de referência, permitindo a criação do testbench antes mesmo da implementação do DUV, de forma a facilitar a verificação do mesmo e dando ênfase à fase de verificação. Com isso, a metodologia se propõe a minimizar o tempo total de verificação e encontrar erros mais cedo, quando o DUV começa a ser implementado.

De forma a realizar esse intento, usando a metodologia VeriSC é possível fazer a verificação do RTL em todas as fases de sua implementação, até mesmo no início. Além disso, essa metodologia propõe o reuso dos próprios elementos do testbench para criar os testbenches hierárquicos e para testar os próprios componentes do testbench e assegurar que ele não contenha erros.

## 1.3 Organização

Esse documento está organizado da seguinte forma:

O Capítulo 2 apresenta os conceitos fundamentais referentes à verificação funcional, definindo dessa forma, as nomenclaturas e conceitos adotados nesse trabalho, bem como alguns trabalhos relacionados.

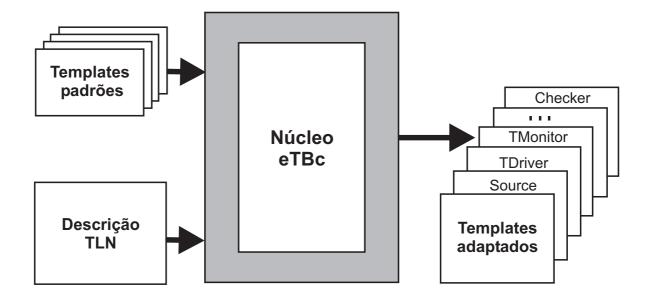

O Capítulo 3 apresenta a metodologia VeriSC, que é a proposta resultante desse trabalho de doutorado. O Capítulo apresenta todos os passos necessários para se criar um testbench

baseado nessa metodologia. Esse Capítulo mostra a biblioteca de cobertura funcional BVE-COVER, bem como uma introdução à ferramenta de geração de testbenches eTBc (*Easy Testbench Creator*).

- O Capítulo 4 mostra os resultados obtidos pelo trabalho de doutorado.

- O Capítulo 5 apresenta as conclusões e sugere alguns trabalhos futuros.

## Capítulo 2

## Conceitos de Verificação Funcional

No capítulo anterior, foram descritas as fases de um projeto de hardware, de forma a dar ao leitor uma visão geral do contexto para a apresentação da metodologia de verificação VeriSC. As demais fases de implementação de hardware estão diretamente ligadas à verificação e são influenciadas por essa fase, no entanto, não serão abordadas profundamente no escopo desse documento.

Esse capítulo relata os conceitos básicos no qual se baseia esse trabalho de forma a facilitar o entendimento e os trabalhos relacionados da área. A descrição dos trabalhos relacionados não possui a pretensão de esgotar o assunto e discutir todos os trabalhos relacionados, mas sim de dar uma visão geral dos vários aspectos abordados por outros pesquisadores da área.

### 2.1 Dispositivo a ser verificado

A literatura adota nomenclaturas diferentes para denominar o dispositivo a ser verificado. Nesse trabalho, esse dispositivo será denominado DUV (*Device Under Verification*).

O dispositivo a ser verificado pode ser implementado em níveis diferentes de abstração. Esse dispositivo pode começar a ser implementado a partir de um modelo comportamental e ter a sua implementação refinada até um nível de portas lógicas. No entanto, nesse trabalho, será considerado um dispositivo implementado no nível RTL (*Register Transfer Level*) ou linguagem de descrição de hardware. A metodologia aqui apresentada pode ser usada pelos demais níveis de abstração, da mesma forma.

## 2.2 Tipos de verificação

Os erros lógicos nos dispositivos são causados pelas discrepâncias ocorridas entre o comportamento pretendido e o comportamento observado. Esses erros podem ocorrer devido à especificação ambígua, interpretação errada da especificação ou devido a algum erro inserido na implementação do DUV. Esses erros podem ser captados através da verificação, que pode ser realizada de forma estática, dinâmica ou híbrida.

#### 2.2.1 Verificação estática

Entre a verificação estática, também chamada de verificação formal, de acordo com a definição de Bergeron [5] temos: verificação de modelos, verificação de equivalência e prova de teoremas.

A verificação de modelos demonstra que propriedades definidas pelo usuário nunca são violadas para todas as possíveis sequências de entradas. A verificação de equivalência, por sua vez, compara dois modelos para determinar se eles são logicamente equivalentes ou não. Finalmente, a prova de teoremas demonstra que o teorema está provado ou não pode ser provado.

A verificação formal pode provar a inexistência de erros através de equações matemáticas e verificação de modelos. No entanto, esse processo pode ser complicado e podem ocorrer limitações do tamanho do circuito a ser verificado.

#### 2.2.2 Verificação dinâmica

A verificação dinâmica, também denominada verificação funcional, é realizada através de simulação. Verificação funcional não prova a ausência de erros e sim a presença dos mesmos. No entanto, não há limitações de tamanho de modelos a serem verificados, desde que não haja empecilho com relação ao tempo gasto na simulação. Além disso, existem métodos para certificar quanto das funcionalidades de um projeto foram testadas, o que pode dar uma certa garantia de quanto a verificação foi abrangente. Esses métodos são chamados de cobertura.

#### 2.2.3 Verificação híbrida

A verificação híbrida, também conhecida como semi-formal, combina técnicas das verificações estática e dinâmica, tentando sobrepor as restrições de capacidade impostas pelos métodos estáticos e as limitações de completude dos métodos dinâmicos.

## 2.3 Verificação funcional

A verificação funcional foi a técnica escolhida para esse trabalho. O conceito de verificação funcional adotado nesse trabalho se baseia no livro de Bergeron [5] e possui a seguinte definição: verificação funcional é um método utilizado para comparar o DUV com sua especificação.

O ponto de partida de um projeto de verificação é que exista uma especificação, considerada o modelo ideal e essa especificação deve ser respeitada durante toda a fase de projeto. A verificação funcional é um processo que acompanha o dispositivo em busca de uma completa verificação de todas as suas funcionalidades especificadas.

Um aspecto importante é decidir a granularidade do circuito a ser verificado. Quando se faz a verificação de um projeto, ele é normalmente dividido em blocos para facilitar a verificação do mesmo. O processo de verificação funcional torna-se mais complexo quando empregado em um bloco muito grande, por ser mais difícil encontrar um erro ao fazer a simulação do projeto inteiro de uma única vez. Quando o projeto é muito grande, ao aparecer um erro, é necessário fazer uma investigação de todo o modelo para descobrir onde está a causa desse erro. Com um modelo menor, essa investigação se torna mais fácil. Por outro lado, com essa divisão, mais testbenches devem ser criados para a verificação de cada bloco em que o DUV foi dividido. Para efeito de comparação, o Modelo de Referência e o DUV devem ser divididos da mesma forma para possibilitar a verificação. Considerações maiores sobre o número de hierarquias a serem empregadas e o tamanho adequado de um DUV podem ser encontrados na literatura [5].

Em um projeto de hardware é necessário que a implementação do dispositivo a ser verificado e a verificação sejam feitos por pessoas diferentes, respectivamente pelos engenheiros de projeto e verificação. Isso é necessário para que o erro introduzido por algum deles não seja absorvido pelo outro. É aconselhável que eles tenham o mínimo contato possível.

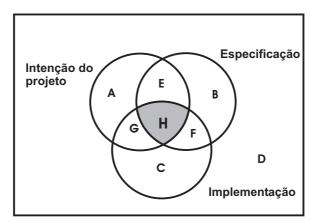

Com relação à sua concepção, existem três aspectos da verificação funcional que devem ser cuidadosamente observados: intenção do projeto, especificação e implementação. De acordo com Piziali [29] esses aspectos podem ser representados através do diagrama da Figura 2.1.

Figura 2.1: Diagrama de projeto

Esse diagrama é composto de três círculos que se sobrepõem. Cada círculo representa um aspecto do projeto.

O círculo intenção do projeto (A, E, H, G) representa o comportamento do projeto, da forma como o engenheiro de projeto o imagina. O círculo especificação (B, F, H, E) representa a documentação da especificação funcional do dispositivo. O círculo implementação (F, C, G, H) é a parte do projeto que o engenheiro consegue implementar a partir da especificação. Além disso, o comportamento não pretendido, não especificado e não implementado, está representado fora do círculo, com a letra D.

Nessa figura, é importante observar que os círculos se sobrepõem em algumas áreas, onde existem pontos comuns. Um exemplo desses pontos comuns é o ponto simbolizado pela letra E. Nesse ponto, estão todos os aspectos capturados pela intenção e especificação do projeto e não satisfeitos pela implementação. Outro exemplo pode ser visto na letra F. Ele mostra aspectos especificados, implementados, mas que não estavam contidos na intenção do engenheiro. No entanto, o mais importante desses espaços é representado pela letra H, pois aí se encontra a sobreposição dos três círculos, representando a interconexão do intento do projeto, a sua especificação e a implementação. Isso quer dizer que os três aspectos do projeto foram cobertos nessa área. Quanto maior for a área da interconexão dos três

círculos, melhor será o projeto construído. Um modelo ideal seria que os três círculos se sobrepusessem de forma integral.

#### 2.3.1 Black-box, grey-box e white-box

Do ponto de vista da visibilidade de um testbench para a verificação funcional, existem três abordagens: Black-box, grey-box e white-box.

A abordagem black-box permite que a verificação funcional seja realizada sem nenhum conhecimento da implementação real do DUV. A verificação é acompanhada nas interfaces do DUV, sem acesso direto aos estados internos dele e sem conhecimento de sua estrutura e implementação. Essa abordagem possui a vantagem de não depender de qualquer detalhe de implementação. Mesmo que o DUV seja modificado durante a fase de verificação, o testbench não precisa ser alterado se a interface não for mudada. O ponto negativo dessa abordagem é que se perde um pouco do controle da parte interna da implementação do DUV, uma vez que não se tenha acesso aos detalhes de implementação.

Com a abordagem white-box, é possível ter uma visibilidade e controlabilidade completa da estrutura interna do DUV. A vantagem de se usar white-box é que se pode testar diretamente funções do dispositivo sendo verificado, uma vez que se tem acesso a ele e rapidamente localizar o local onde ocorreu uma falha. A desvantagem dessa abordagem é que ela é altamente acoplada com detalhes de verificação. Uma vez que o DUV seja modificado, todo o testbench deve ser modificado também. Além disso, é necessário ter conhecimento de detalhes de implementação para criar cenários de testes e saber quais as respostas que devem ser esperadas.

A abordagem grey-box possui características das duas abordagens. Ela procura resolver o problema da falta de controlabilidade do black-box e da dependência de implementação do white-box. Um exemplo de um caso de teste típico grey-box pode ser usado para aumentar as métricas de cobertura. Nesse caso, os estímulos são projetados para linhas de código específicas ou para verificar funcionalidades específicas.

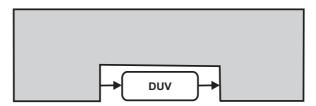

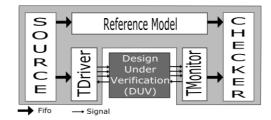

#### 2.3.2 Testbench

A verificação funcional utiliza simulação para verificar o DUV. Para que essa simulação seja possível, é necessário que haja um ambiente de verificação que possa receber o DUV, inserir estímulos e comparar suas respostas com as respostas de um modelo ideal. Esse ambiente é denominado de testbench.

Em uma simulação, o DUV tem seus resultados comparados com os resultados da especificação. Essa especificação pode ser implementada em um modelo executável. Esse modelo recebe várias denominações, tais como Golden Model e Modelo de Referência. Para a verificação funcional, esse modelo é considerado como sendo a implementação da especificação e por isso sendo livre de erros. Nesse trabalho a denominação usada será Modelo de Referência.

A Figura 2.2 mostra a estrutura genérica de um testbench. Nessa figura, o testbench é representado pelo U invertido, ou seja, a região que envolve o DUV.

Figura 2.2: Esquema de um testbench genérico

Um bom testbench deve possuir as seguintes características básicas: ser dirigido por coberturas, possuir randomicidade direcionada, ser autoverificável e baseado em transações [5].

- O testbench é dirigido por coberturas se o seu tempo de simulação e estímulos escolhidos dependem de critérios de cobertura pré-estabelecidos. Durante a especificação da verificação são traçadas todas as metas de cobertura que devem ser alcançadas durante a simulação. Cobertura é um dispositivo para detectar se todas as funcionalidades especificadas foram testadas e será explicado mais adiante.

- Ele possui randomicidade controlada quando são utilizados estímulos randômicos direcionados para testar todas as funcionalidades do projeto e atingir uma determinada cobertura especificada. Os estímulos randômicos não são completamente randômicos,

a randomicidade é direcionada para atingir valores determinados para um determinado bloco do DUV. É importante observar que esses estímulos possuem a facilidade de uma vez que eles sejam colocados para simular, vão gerar valores dentro da distribuição de probabilidade escolhida e somente vão parar de gerar valores uma vez que a cobertura funcional for atingida. Caso se perceba que a cobertura não foi atingida dentro de um determinado tempo e que ela não está progredindo, deve-se mudar a distribuição de probabilidade de acordo com as funcionalidades não atingidas na cobertura para que as funcionalidades não exercitadas venham a ser exercitadas e a cobertura atingida.

- Além disso, o testbench deve possuir autoverificação, ou seja, ele deve ter mecanismos que permitam que ele verifique automaticamente as respostas obtidas da simulação com as respostas esperadas pela especificação do projeto. O trabalho de verificar manualmente todos os resultados obtidos da simulação é muito árduo e propenso a erros, pois é necessário comparar cada saída do DUV com o resultado esperado. Dessa forma, o testbench deve ter uma forma de fazer essa comparação de forma automática, evitando assim esse trabalho manual. O Modelo de Referência é muito importante nessa operação de autoverificação, pois ele permite que os resultados do DUV possam ser automaticamente comparados com os resultados de um modelo ideal, diminuindo as possibilidades de que um erro causado por uma comparação mal feita venha a ocorrer.

- O testbench também não possui entradas e nem saídas, imprime mensagens quando o DUV apresenta comportamento inesperado e pode criar arquivos de logs para uma análise posterior.

- Finalmente, o testbench deve ser implementado no nível de transações. Uma transação

é uma transferência de informações de alto nível, de dados ou controle, entre o

testbench e o DUV sobre uma interface.

É muito importante que esses estímulos sejam criados em um alto nível de abstração para que o trabalho seja realizado de forma mais eficiente, sem se preocupar com detalhes de baixo nível, pois os testes são realizados em um nível de sistema. Essa capacidade melhora a depuração e análise da cobertura, apresentando informações em termos de transação e seus relacionamentos ao invés de sinais e formas de onda.

O testbench possui um nível de implementação diferente do DUV, pois o DUV é implementado no nível de sinais e eles se comunicam com protocolos no nível de sinais.

A metodologia de verificação baseada em transação foi introduzida em 1998 por Richard Goering [18] e integrada em um uma ferramenta de verificação em 1999 [36]. metodologia foi primeiramente usada no laboratório da Cadence [40] e sua descrição pode ser encontrada no trabalho de Brahme [7] "The transaction-based Verification Methodology". Nesse trabalho é apresentada a metodologia para se trabalhar com transações. Basicamente ela é dividida em duas partes: a camada de cima que lida com as transações sem se preocupar com detalhes específicos de protocolos no nível de sinais e a camada de baixo que faz o mapeamento entre o nível de transação e os protocolos nos níveis de sinais. Com o uso dessa metodologia existem ganhos com reuso, ferramentas de depuração, facilidade de implementação e entendimento por parte dos desenvolvedores. O artigo mostra também os passos utilizados para realizar uma verificação funcional completa, utilizando a biblioteca de C++ Testbuilder. Ele aborda todos os principais conceitos para realizar uma verificação funcional completa, tais como: simulação no nível de transações, geração de todos os tipos de estímulos, inclusive o randômico direcionado, autoverificação e coberturas. Além disso, ele mostra que uma verificação deve ter uma forma de ordenamento das transações, tais como FIFOs e semáforos.

O trabalho proposto nesse documento de tese, também utiliza todos esses conceitos de verificação funcional descritos na metodologia do trabalho de Brahme, embora utilize o *Testbuilder-SC* no lugar do *C++ Testbuilder*. Difere também na abordagem, pois gera o testbench antes do DUV, ao contrário da forma apresentada no trabalho de Brahme.

#### 2.3.3 Cobertura

Na verificação funcional, um grande problema é saber quando parar a simulação de forma que a verificação esteja completa, ou seja, quando o DUV está totalmente verificado. Esse problema decorre do fato de que a simulação em si não consegue afirmar se todas as funcionalidades implementadas foram verificadas. É muito importante que exista um dispositivo para detectar se todas as funcionalidades especificadas foram testadas.

Pode-se tentar resolver esse problema de testar as funcionalidades especificadas através

do uso de geradores de testes randômicos. Os geradores de testes randômicos estão se tornando cada vez mais avançados e realmente tem ajudado a melhorar a qualidade da verificação dos dispositivos, pois eles geram valores aleatórios, que se simulados durante um tempo suficiente, podem cobrir todos os valores necessários para estimular o dispositivo. Porém esses geradores de testes sozinhos não podem garantir e nem mostrar quanto das funcionalidades especificadas foram testadas ou ainda quando elas foram testadas mais de uma vez. Para responder a pergunta se todas as funcionalidades especificadas foram testadas, tem sido usada cobertura funcional.

Cobertura Funcional é uma técnica usada para medir o progresso da simulação e reportar quais as funcionalidades deixaram de ser testadas. Cobertura pode ajudar no monitoramento da qualidade de testes e direcionar esses testes para criar geradores que cobrem áreas que não foram adequadamente testadas. A parte do espaço de cobertura não testado é chamada de buraco de cobertura.

Uma das formas de realização da cobertura funcional é através do modelo de cobertura *cross-product* ou também denominado de cross-coverage. Esse modelo é criado testando-se todas as possibilidades existentes dentro de um conjunto de funcionalidades definidas. Por exemplo, o par de funcionalidades <pedido, resposta>, onde pedido é um dos possíveis pedidos que podem ser mandados para a memória (ex. escrita de memória, leitura de memória, etc) e resposta é uma das possíveis respostas (aceita, não aceita, rejeita, etc). O espaço de cross-coverage é formado pelo produto cartesiano de todas essas funcionalidades e deve ter cada uma delas testada.

Um problema que deve ser descoberto pela cobertura funcional é o buraco de cobertura. O buraco de cobertura é definido como sendo as funcionalidades que não foram testadas durante a simulação do dispositivo.

Esse buraco de cobertura pode ter três causas:

- Funcionalidades não exercitadas porque o simulador precisa de mais tempo para exercitá-las.

- Funcionalidades não exercitadas porque não foram gerados estímulos suficientes para estimular todas as funcionalidades do DUV.

- Existem erros no dispositivo que não permitem que as funcionalidades sejam testadas.

O buraco de cobertura deve ser descoberto e solucionado, pois ele pode levar a uma verificação incompleta.

A principal técnica para mostrar que uma simulação obteve sucesso, é analisar a cobertura. Isso significa criar uma lista de tarefas (funcionalidades especificadas a serem testadas) e observar se cada uma dessas funcionalidades foi testada durante a fase de simulação.

O primeiro passo para implementar a cobertura funcional é criar um modelo de cobertura. O modelo de cobertura faz parte da especificação da verificação e é o documento que deve se ter como base para a implementação da cobertura funcional. Não é recomendado que se inicie a cobertura funcional diretamente na implementação do código da cobertura. Inicialmente deve-se ter certeza de ter entendido toda a funcionalidade do dispositivo a ser verificado e estar certo de ter extraído todas as informações que devem ser verificadas no mesmo.

O modelo de cobertura consiste em isolar os atributos "interessantes" e construir a sua história. Entenda-se aqui por atributos interessantes, todos aqueles que devem ser analisados no momento de se fazer uma análise de cobertura funcional, por serem considerados difícieis ou propensos a erros. Além disso, devem ser definidas restrições para o modelo. As restrições são partes da simulação, são combinações de atributos que nunca devem ocorrer. Caso a parte de atributos definidos como ilegais seja simulada, isso pode demonstrar que existe um erro na implementação do projeto.

Alguns autores discutem e oferecem soluções para a cobertura funcional e para a análise e solução dos buracos de coberturas identificados na verificação do DUV.

No trabalho de Lachish [25] "Hole Analysis for Functional Coverage Data" são descritos métodos para descobrir, reportar e analisar grandes espaços não cobertos, ou seja, buracos de cobertura. Esses buracos de cobertura são calculados baseando-se nos espaços de cobertura criados através do modelo de cobertura funcional *cross-product*.

Os buracos de cobertura agrupam propriedades que não foram cobertas e que compartilhem propriedades em comum. Basicamente, essa técnica busca encontrar tarefas não cobertas que tenham valores comuns em alguns de seus atributos e achar também algum denominador comum nos valores dos atributos que os distinguem.

Nesse artigo, o espaço de cobertura é composto de quatro componentes:

• Descrição semântica do modelo (história do modelo);

- Lista de atributos mencionados na história;

- Conjunto de todos os valores possíveis para cada atributo;

- Lista de restrições e combinações nos valores de atributos do cross-coverage.

Cada atributo pode ser particionado em um ou mais conjuntos de valores similares semanticamente. Os modelos de cobertura funcionais podem ser black\_box ou white\_box. Esses modelos podem ser também aplicados em um ponto no tempo ou modelos temporais, cujas tarefas correspondem a um estado da aplicação.

As três formas propostas para a descoberta e análise desses buracos de coberturas são as seguintes:

- Buracos agregados. Esse tipo de buraco é descoberto entre tarefas que não são quantitativamente similares. Por exemplo, entre tarefas que possuem a mesma distancia de Hamming entre elas (o número de atributos nos quais os dois buracos diferem é igual).

- Buracos particionados. Essa segunda técnica agrupa buracos que são conceitualmente similares. Valores que são agrupados juntos, normalmente são analisados juntos e buracos que são descobertos em um valor, podem ocorrer para o grupo todo.

- Buracos projetados. Esses buracos são definidos baseados no grupo a que eles pertençam. A dimensão desse buraco projetado é o numero de atributos que não possuem valores específicos. O artigo mostra um algoritmo que possui o objetivo de encontrar a dimensão maior do buraco de cobertura e esse buraco de maior dimensão será o antecessor de todos os outros relacionados a esse e que possuem a dimensão menor.

Uma idéia quando se está implementando o modelo de cobertura é separá-lo da ferramenta de análise, como no trabalho de Grinwald [20] "User defined coverage: a tool supported methodology for design verification", onde o foco principal é separar o modelo de cobertura da ferramenta para fazer a análise posterior.

De acordo com o trabalho, tendo uma ferramenta independente do modelo de cobertura, pode-se elaborar um modelo de cobertura que mais se encaixe dentro do dispositivo que se deseja verificar, pois o usuário pode mudar o escopo ou a profundidade da cobertura durante

o processo de verificação. Isso se deve ao fato de que, em algumas ferramentas, o modelo de cobertura é tão genérico que não consegue ser aplicado para uma necessidade específica, sendo necessário por isso que o usuário implemente a sua própria ferramenta de cobertura. A ferramenta de análise utilizada nesse trabalho é denominada COMET (Coverage measurement tool). Essa ferramenta gera todas as funcionalidades que são comuns tanto para modelos de cobertura específicos como para modelos genéricos, tais como relatórios de tarefas e relatórios de eventos ilegais. Esses relatórios mostram o progresso de cada atributo e o progresso da cobertura como uma função do tempo. O modelo de cobertura criado é baseado em atributos. Ele é dividido em duas partes: *snapshot* e temporal. O *snapshot* se preocupa somente com eventos instantâneos, enquanto o temporal pode fazer o cruzamento de dois eventos em tempos distintos.

O trabalho de Asaf [3] "Defining Coverage Views to Improve Functional Coverage Analysis", visa resolver o problema causado pela grande dimensão da cobertura funcional em uma verificação. Um dos problemas que ocorrem ao tentar implementar a cobertura funcional é causado pela tentativa de cobrir todos os casos da cobertura de uma só vez, o que torna o número de eventos a serem cobertos muito grande e difícil de analisar. A solução apresentada nesse trabalho é definir vistas para a realização de cobertura funcional *cross product*, enfocando em partes específicas do modelo. A cobertura *cross-product* compreende todas as possíveis combinações de valores para um dado conjunto de atributos.

No trabalho são apresentadas as três operações básicas para a definição de vistas de cobertura funcional. Essas operações, utilizadas na restrição e seleção do que deve ser analisado na cobertura, são: projeção, seleção e agrupamento. Na projeção os dados cobertos são projetados em um subconjunto de valores escolhidos do *cross-product*. Essa operação deve ser realizada porque procurar erros em todos os valores gerados pode ser muito incômodo e propenso a erros. A segunda operação seleciona eventos específicos, isso permite ignorar partes que não são interessantes para a verificação. Essa operação permite selecionar e filtrar eventos. A terceira operação cobre eventos juntos, podendo agrupar sempre eventos que pertençam a uma mesma classe de funcionalidades e podendo olhar suas respostas combinadas, por exemplo, agrupar sempre eventos de E/S. Usando vistas definidas para cobertura pode-se facilitar bastante o trabalho da realização da cobertura funcional de componentes muito grandes.

Outro problema que se encontra diretamente ligado à cobertura é a geração de estímulos. Os estímulos devem ser gerados de forma a direcionar a simulação para alcançar os critérios de cobertura estabelecidos para que a simulação exercite todas as funcionalidades especificadas.

#### 2.3.4 Geração de estímulos

Durante a simulação para a realização da verificação funcional, o DUV deve ser estimulado por uma ampla variedade de combinações de valores. O ideal é que sejam previstas situações que venham a testar todas suas funcionalidades. De forma a conseguir esse objetivo, o DUV deve ser simulado com os seguintes estímulos: estímulos citados na especificação, situações críticas, estímulos randômicos e casos de testes reais. Com o uso desses estímulos, a simulação deve atingir a cobertura proposta na especificação da cobertura. Caso essa cobertura não seja alcançada, é importante que esses estímulos sejam mudados de forma a alcançar tal cobertura.

A geração de estímulos pode ser feita de forma manual ou através de alguma ferramenta. A geração manual pode ser pouco eficiente para alcançar a cobertura, pois nem sempre cobre todas as possibilidades necessárias. A geração através de ferramentas especializadas possui uma chance maior de detectar erros, que possam até mesmo escapar da especificação. Existem diversos trabalhos que procuram melhorar a qualidade dos estímulos em uma verificação, esses trabalhos focam principalmente na geração de estímulos e na obtenção de uma boa cobertura para a simulação.

O trabalho de Ferrandi "Functional Verification for SystemC Descriptions using Constraint solving" [14] apresenta uma solução para a criação de vetores de testes para o DUV, através da técnica de ATPG (*Automatic Test Pattern Generation*), baseada em controlabilidade e observabilidade. O DUV é descrito como sendo uma máquina de estados finitos. O método para realizar essa geração de testes é baseado na simulação de uma seqüência de entradas. O algoritmo proposto introduz o conceito de seqüência de transição, como sendo um caminho finito, para resolver o problema de ter que gerar um número infinito de caminhos. De acordo com as técnicas mostradas no algoritmo a seguir, pode ser obtido um conjunto de seqüências, onde cada seqüência é um conjunto ordenado de restrições. Esse algoritmo ajuda a alcançar o maior caminho de cobertura possível.

O algoritmo de geração de testes é composto de cinco tarefas principais:

- Aquisição de dados: Todas as informações sobre o sistema são processadas. Essas informações são as listas de portas, sentença, instruções condicionais e transições. Elas são obtidas para a análise do código fonte em SystemC;

- Análises das transições: Consiste em encontrar os estados iniciais e finais de cada transição;

- Enumeração de seqüência: Enumera vários caminhos de execução em potenciais no SystemC, para os quais, vetores de teste são necessários.

- Análises de seqüências e produção de restrições: para cada seqüência considerada, um conjunto de restrições é produzido. Esse conjunto de restrições corresponde a todas as instruções condicionais que devem ter como resultado o valor TRUE durante a execução da seqüência. Quando essas restrições são aplicadas para variáveis e sinais (não para portas), não é possível forçar o valor das variáveis e sinais para um dado valor, portanto deve-se retroceder no código, até encontrar qual porta ou constante deu origem a essa seqüência de variáveis e sinais.

- Resolvedor de restrições e extração de testes: Finalmente, o resolvedor de restrições gera uma solução, caso exista, para satisfazer um conjunto de restrições associado com a seqüência.

Esse trabalho possui o foco voltado para a geração de vetores de teste com o objetivo de alcançar um critério de cobertura. Ele utiliza o resolvedor de restrições denominado GProlog. No entanto, não existe nenhuma especificação de como os critérios de cobertura podem ser medidos.

Outro exemplo de geração de estímulos aliado com a controlabilidade da cobertura pode ser visto no trabalho de Benjamin "A study in Coverage-Driven Test Generation" [4]. Nesse trabalho, o autor descreve a importância da cobertura para a geração de estímulos. Além disso, ele apresenta uma metodologia para verificação funcional que se diferencia das demais através da forma de geração de estímulos. Essa metodologia é híbrida, são integrados os métodos de simulação e verificação de modelos (formal).

O gerador de testes dirigido pela cobertura é um programa que acha um caminho através de uma máquina de estados finitos do projeto e seu objetivo é achar um caminho que satisfaça cada tarefa do modelo. O autor denominou esses caminhos de testes abstratos. Ele utiliza algoritmos para essa geração de testes abstratos, utilizando modelos de cobertura de transição e modelos de coberturas de estados. Esses algoritmos são implementados na ferramenta GOTCHA. Os resultados de testes esperados são produzidos por um simulador arquitetural, que é o Modelo de Referência para a verificação. Isso significa que nenhum teste gerado contém erros.

O autor define também testes concretos. Esses testes são seqüências de instruções que forçam o projeto através de um caminho pré-definido nos testes abstratos, formando a especificação de testes. Esses testes são utilizados na simulação do DUV.

O trabalho de Dudani [28] "High Level Functional Verification Closure" também aborda formas de gerar testes para preencher o espaço existente entre a cobertura real obtida através de dados de testes fornecidos e os objetivos de cobertura requeridos. Porém a solução adotada é baseada na implementação de quatro técnicas muito importantes para melhorar a eficiência da verificação: especificação de *assertions*; cobertura funcional; simulação randômica e *testbenches* reativos. Nesse trabalho são discutidas as seguintes definições:

- Especificação de *assertions*: *Assertions* normalmente são chamadas de checker ou monitor. Elas são a descrição do comportamento esperado quando o projeto é estimulado com uma entrada. Para verificar uma característica do DUV, primeiro a sua funcionalidade precisa ser entendida, depois ela precisa ser explicitamente descrita e finalmente as condições sob as quais o comportamento é aplicado precisam ser estabelecidas. Essa descrição é implementada em uma *assertion*.

- Cobertura funcional: A cobertura funcional é baseada na funcionalidade do projeto. Ela mede quanto da funcionalidade do projeto está sendo verificada. Usando assertions como ponto inicial da cobertura funcional, pode-se descrever cenários funcionais mais elaborados, para capturar corner cases e todas as combinações de dados e controle.

- Simulação randômica: a simulação randômica é criada para exercitar as funcionalidades básicas do projeto. Simulações randômicas podem ser manipuladas para exercitar

áreas críticas e são normalmente ajustadas através de "tentativa e erro".

• *Testbenches* reativos: Normalmente os estímulos randômicos são ajustados manualmente trocando a "semente" de geração. O uso de cobertura funcional durante a verificação pode dar um *feedback* de quais as funcionalidades que ainda precisam ser verificadas. O *testbench* reativo funciona de forma que o *feedback* recebido da cobertura funcional dirige o *testbench* para fazer os ajustes necessários para criar estímulos mais efetivos para a verificação funcional.

Alguns trabalhos são discutidos como forma de implementação de cada uma dessas definições e no final é proposta uma metodologia baseada nesses trabalhos. A metodologia usa *assertions* para exercitar vários caminhos dentro de um cenário e a cobertura funcional enumera esses caminhos e monitora cada um deles. No final, têm-se quais os caminhos que foram exercitados, com o objetivo de encontrar erros não cobertos pela simulação. Os testes são direcionados com o feedback da cobertura.

No trabalho de Hekmatpour [22] "Coverage-Directed Management and Optimization of Random Functional Verification" são propostos métodos para melhorar a qualidade dos geradores de testes nos vários estágios da verificação funcional. Ele descreve métodos para calibrar o gerador de testes e melhorar a cobertura funcional. O trabalho propõe que a cobertura de 100% dos testes seja feita através das seguintes técnicas:

- Uso de gerador de testes baseado em modelos, onde o gerador de teste utiliza randomicidade e controle. O usuário deve poder enriquecer a saída do gerador por um conhecimento prévio dos testes;

- Utilização da randomicidade de forma a controlar a quantidade de erros sendo encontrada. Quando essa quantidade for decrescendo, mudar a randomicidade de forma controlada para capturar novos erros;

- Geração de testes randômicos de forma incremental. Sempre entre um teste e outro deve ser feita uma análise da cobertura.

- Utilização de testes randômicos dirigidos pelos erros encontrados. Essa técnica deve ser utilizada para garantir que esse erro não volte a acontecer e que não há mais nenhum erro próximo a esse e/ou relacionado a ele.

- Existência de um plano de verificação dinâmico, que reflita o estado presente do projeto. Ele deve ser revisto e atualizado sempre que algo seja mudado no projeto, até mesmo após um novo erro ser encontrado.

- Escolha dos requisitos para o gerador de testes. Deve-se elaborar um plano para o gerador de testes.

- Deve-se calibrar o gerador de testes. Para isso é necessário desenvolver um qualificador, que possa detectar que o comportamento do gerador de testes está consistente, de acordo com o esperado.

- Gerenciamento da verificação, guiando-se pela cobertura.

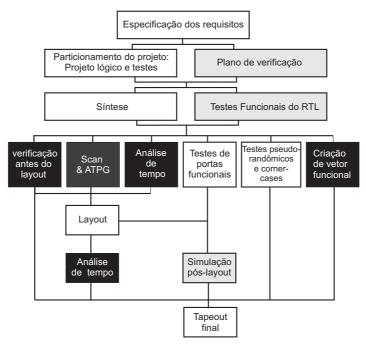

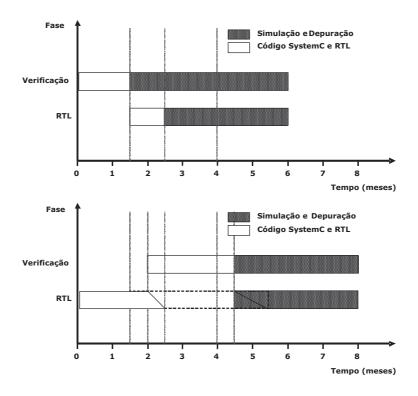

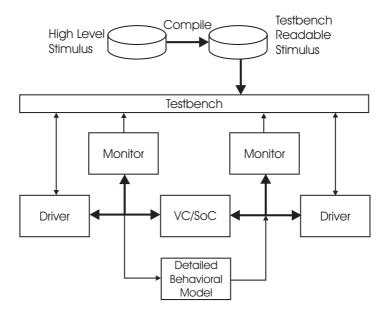

A metodologia, apresentada no trabalho de Hu [23] "A Methodology for Design Verification", é um fluxo de projeto para a verificação funcional de componentes de hardware, que vai desde a especificação até a prototipação do projeto. Nessa metodologia são definidos papéis para os engenheiros de projeto e verificação e cada parte do projeto é definido de acordo com a metodologia proposta por eles. Há uma proposta de paralelização do trabalho dos engenheiros de projeto e verificação para uma maximização e melhor aproveitamento do tempo da equipe. Na Figura 2.3 o fluxo de projeto é dividido entre as equipes de projeto e verificação. As partes cinzas são as tarefas do engenheiro de verificação, as partes brancas são as atividades do engenheiro de projeto e os quadros pretos são as atividades realizadas por ambos.

Com a apresentação desses trabalhos é possível observar que existem diversas formas de criação de testes para estimular o DUV durante a verificação funcional, bem como diferentes abordagens que podem ser empregadas durante essa verificação.

A próxima Seção mostra a biblioteca de classes SystemC, utilizada nesse trabalho para a construção do testbench para a verificação funcional.

# 2.4 SystemC

SystemC [6; 21] é uma biblioteca de classes da linguagem de programação C++ padronizada pela OSCI (*Open SystemC Initiative*), uma organização composta por uma variedade de companhias, universidades e indivíduos. Ela é orientada a objetos e estende a capacidade do C++

Figura 2.3: Fluxo de projeto do trabalho de Hu

para permitir a modelagem de hardware. Para isso, ela adiciona importantes conceitos como concorrência, eventos e tipos de dados de hardware, tais como sinais, portas e módulos.

Para permitir que o SystemC tivesse recursos para a verificação, foi criada uma biblioteca de classes chamada de *SystemC Verification Library*-SCV. A biblioteca SCV fornece suporte para: criação de APIs para a verificação baseada em transações, randomização direcionada, manipulação de exceções e outras características de verificação. A SCV permite programação no nível de transações, uma metodologia que habilita abstração de alto nível, reutilização de código e alta velocidade de simulação.

Outro fator importante para a escolha do SystemC está descrito no trabalho de Fin [15] "SystemC: a homogenous environment to test embedded systems". Esse trabalho mostra que SystemC pode ser usado para geração de testes para verificação funcional, descrever módulos em diferentes níveis, tais como módulos em RTL e módulos de software, sendo possível passar de um nível de abstração para o outro sempre usando a representação do SystemC. Com essa possibilidade torna-se viável o procedimento de teste aplicável para todas as fases de projeto.

No trabalho de Randjic [30] "Complex ASICs Verification With SystemC" é descrita uma forma de verificação do processador de rede *PcomP*, através da biblioteca de C++,

# SystemC.

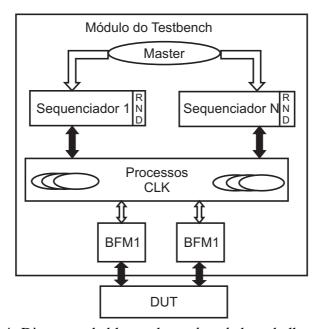

O dispositivo *PcomP* é um processador de comunicação totalmente programável. O DUV é ligado ao *testbench* via funções BFM (*Bus Functional Model*) que representam APIs, como mostrado na Figura 2.4. O módulo Master é responsável pelos parâmetros de entrada e por iniciar os testes apropriados, chamando os devidos seqüenciadores. O seqüenciador, por sua vez, prepara os dados de entrada para os processos stimuli/checker, faz uma análise dos dados, espera a execução e retorna os dados do processo. Os dados passados para o módulo CLK podem ser gerados utilizando muitos tipos de randomização. Os seqüenciadores obtêm esses dados do processo Master. Todos os dados de geração e controle são deixados para o bloco RND. A troca de dados entre seqüenciadores e CLK é feita via FIFOs. Em seguida, o processo CLK chama as funções BFM e faz todas as ações necessárias nos parâmetros. Elas usualmente estimulam e checam o comportamento do DUV. Os dados de entrada são lidos de um arquivo de entrada e os dados de saída são escritos em um arquivo de saída.

Através desse método chegou-se a conclusão de que é possível realizar qualquer teste funcional chamando o processo CLK de forma apropriada.

Figura 2.4: Diagrama de blocos do testbench do trabalho de Randjic

O trabalho descrito em [34], faz a comparação entre dois métodos de verificação hierárquicos: o método desenvolvido pelo VeriSC1, trabalho realizado no início do meu trabalho de doutorado e descrito em [12] e um método de aceleração da simulação, baseado em um filtro para retirar estímulos redundantes na simulação do código RTL e acelerar o processo de verificação. O trabalho relata que a simulação do Modelo de Referência é mais rápida que a simulação do DUV. Por isso, ele propõe que o Modelo de Referência seja simulado com os dados e que esses dados sejam analisados, de forma a verificar se eles são ou não redundantes (já atingiram a cobertura esperada). Os dados redundantes são então enviados para um filtro, o qual vai impedir que o RTL venha a ser simulado com esses dados redundantes.

# 2.5 Considerações sobre conceitos de verificação funcional

Todos os trabalhos apresentados no estado da arte implementam o DUV antes do testbench para a realização da verificação funcional. Isso faz com que a parte de maior impacto em um projeto de componentes digitais, a verificação funcional, não seja priorizada no momento da implementação do DUV. Muitos trabalhos [32; 3; 14; 4; 16; 28; 35] são específicos para uma parte da metodologia de verificação funcional, tal como a elaboração de estímulos eficientes ou implementação de cobertura funcional para tentar exercitar ao máximo as funcionalidades do projeto. As ferramentas comerciais são mais completas na sua abordagem [41; 10; 19; 40], no entanto são somente plataformas para verificação, não possuem uma metodologia para guiar a verificação funcional, embora contenha todos os requisitos para realizá-la.

A metodologia VeriSC, apresentada neste trabalho de doutorado, diverge do fluxo de verificação tradicional dos trabalhos apresentados no estado da arte, propondo um fluxo de verificação funcional melhor integrado no desenvolvimento do projeto.

# Capítulo 3

# Metodologia VeriSC

A metodologia de verificação VeriSC pode ser aplicada para a verificação funcional de DUVs digitais síncronos que utilizam um único sinal de relógio. O fato da utilização de um único relógio não inviabiliza a aplicação em circuitos maiores que tenham mais de um relógio, se este pode ser dividido em vários circuitos com um único relógio.

A metodologia VeriSC é composta de um novo fluxo de verificação, que não se inicia pela implementação do DUV. Nesse fluxo, a implementação do testbench e do Modelo de Referência antecedem a implementação do DUV. Para permitir que o testbench seja implementado antes do DUV, a metodologia implementa um mecanismo para simular a presença do DUV com os próprios elementos do testbench, sem a necessidade da geração de código adicional que não é reutilizado depois. Com esse fluxo, todas as partes do testbench podem estar prontas antes do início desenvolvimento do DUV. Esse fluxo será explicado na Seção 3.2.

A metodologia oferece vários templates para a criação do testbench, que serão explicados na próxima seção.

# 3.1 Construção do testbench

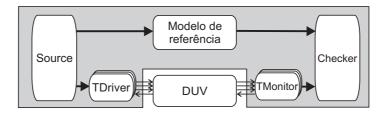

O testbench é o ambiente de simulação no qual o DUV é inserido para realizar a verificação. Esse ambiente estimula o DUV e compara suas respostas com as respostas de um modelo ideal. O testbench da metodologia VeriSC é implementado no nível de transações.

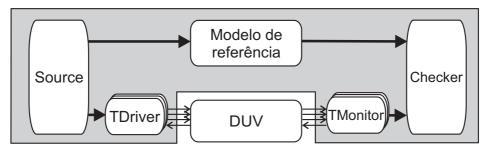

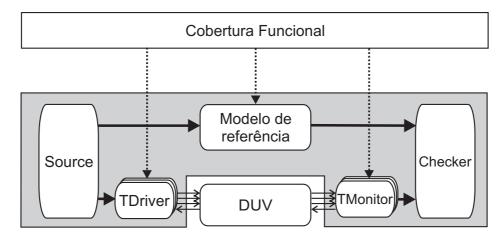

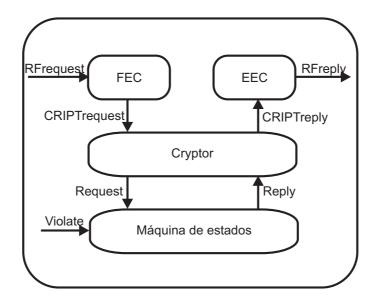

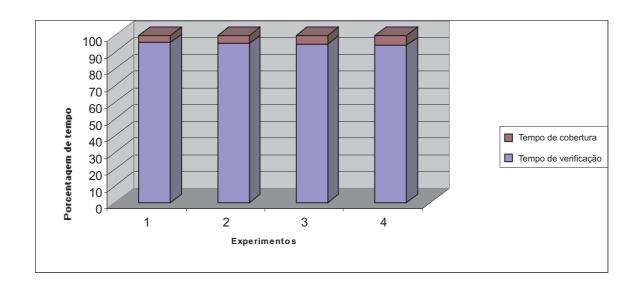

Na Figura 3.1 pode-se ver a composição do testbench que será usado nesse trabalho. O

testbench é a parte da figura em forma de U invertido. Ele é composto pelos seguintes blocos: Source, TDriver(s), TMonitor(es), Modelo de Referência e Checker, sendo que cada bloco do testbench é ligado ao outro por FIFO(s), representadas na figura como setas mais largas. O testbench é ligado ao DUV por interfaces formadas por sinais, representados na figura por setas mais finas.

Figura 3.1: Diagrama do testbench da metodologia VeriSC

O testbench da metodologia VeriSC possui as seguintes características básicas:

- É dirigido por coberturas. A verificação funcional deve parar apenas quando os critérios de cobertura funcional forem alcançados. Além disso, os estímulos são direcionados pelo progresso da cobertura funcional. Se a cobertura não estiver evoluindo, os estímulos devem ser mudados e direcionados para que a cobertura funcional seja atingida.

- Possui randomicidade direcionada. Os estímulos randômicos são direcionados para que a cobertura seja atingida, como explicado anteriormente.

- É autoverificável. O testbench compara automaticamente os resultados vindos do Modelo de Referência e do DUV. Essa verificação ocorre no módulo Checker.

- O testbench é baseado em transações. Os estímulos gerados pelo módulo Source do testbench são todos no nível de transações.

Essas características fazem com que a metodologia permita a criação de um testbench compatível com o estado da arte [5] e de cenários de testes que possibilitem exercitar as funcionalidades especificadas em um plano de verificação [11].

O testbench deve simular ao mesmo tempo o Modelo de Referência e o DUV e comparar se as respostas de ambos são equivalentes. O DUV precisa ser implementado em nível de sinais (RTL) e o Modelo de Referência em nível de transações para facilitar a sua depuração e implementação.

# 3.1.1 Templates

A metodologia VeriSC estabelece uma implementação padrão para cada elemento do testbench. Esse padrão pode ser usado como um roteiro para a geração do testbench, sendo que as partes específicas e particulares a cada DUV devem ser manualmente implementadas pelo engenheiro de verificação. Essa padronização dos elementos do testbench viabiliza o reuso, diminui a quantidade de erros no código e diminui o tempo de implementação, já que várias partes do testbench já se encontram semiprontas.

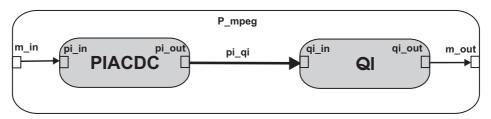

Exemplos dos templates serão mostrados no decorrer dessa seção. Para entender melhor o funcionamento dos templates, será utilizado um exemplo, que é parte do decodificador MPEG4, desenvolvido pelo projeto BrazilIP [24]. Esse exemplo é um DUV composto por dois blocos: Predição Inversa AC/DC *PIACDC* e Quantização Inversa *QI*, como apresentado na Figura 3.2. Essa figura mostra os dois blocos e suas interfaces.

Figura 3.2: Exemplo de um DUV (*P\_mpeg*) formado por parte do MPEG4