### MÁRCIO GERMANO PERISSATTO

### SIMULADOR DE MULTIPROCESSADORES SUPERESCALARES COM MEMÓRIA COMPARTILHADA: SMS-MC

MARINGÁ

# **Livros Grátis**

http://www.livrosgratis.com.br

Milhares de livros grátis para download.

#### MÁRCIO GERMANO PERISSATTO

### SIMULADOR DE MULTIPROCESSADORES SUPERESCALARES COM MEMÓRIA COMPARTILHADA: SMS-MC

Dissertação apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Estadual de Maringá, como requisito parcial para obtenção do grau de Mestre em Ciência da Computação.

Orientador: Prof. Dr. João Angelo Martini

MARINGÁ

# Dados Internacionais de Catalogação-na-Publicação (CIP) (Biblioteca Central - UEM, Maringá – PR., Brasil)

Perissatto, Márcio Germano

P446s Simulador de multiprocessadores superescalares com

memória compartilhada : SMS-MC / Márcio Germano Perissatto.

-- Maringá : [s.n.], 2007.

88 f. : il., figs.

Orientador : Prof. Dr. João Angelo Martini. Dissertação (mestrado) - Universidade Estadual de Maringá. Programa de Pós-Graduação em Ciência da Computação, 2007.

1. Simulador de multiprocessadores superescalares de memória compartilhada. 2. Memória compartilhada. 3. Coerência de cache. 4. SimpleScalar. 5. SMS-MC. 6. Arquitetura de computadores. I. Universidade Estadual de Maringá. Programa de Pós-Graduação em Ciência da Computação. II. Título.

CDD 22.ed. 004.22

#### MÁRCIO GERMANO PERISSATTO

### SIMULADOR DE MULTIPROCESSADORES SUPERESCALARES COM MEMÓRIA COMPARTILHADA: SMS-MC

Dissertação apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Estadual de Maringá, como requisito parcial para obtenção do grau de Mestre em Ciência da Computação.

| Aprovado em 04/09/2007.                                                     |  |

|-----------------------------------------------------------------------------|--|

| BANCA EXAMINADORA                                                           |  |

| Prof. Dr. João Angelo Martini<br>Universidade Estadual de Maringá – DIN/UEM |  |

Prof. Dr. José Hiroki Saito Universidade Federal de São Carlos – DC/UFSCar

Prof. Dr. Ronaldo Augusto de Lara Gonçalves Universidade Estadual de Maringá – DIN/UEM

## Agradecimentos

Dedico meus sinceros agradecimentos para:

- Deus, pelo dom da vida;

- meus pais, por abrirem as portas deste mundo maravilhoso e me ensinarem o caminho dos estudos;

- a minha esposa Emília, pela revisão e incentivo neste trabalho;

- o professor doutor João Angelo Martini, pela orientação e incentivo;

- o professor doutor Ronaldo A. L. Gonçalves, pela ajuda nos momentos de dúvida na codificação e pela confiança;

- a coordenadora do curso de Mestrado em Ciência da Computação, professora doutora

Itana Maria Gimenez, pelo apoio sempre manifestado;

- o professor doutor Candido Ferreira Xavier, pela oportunidade de ingressar no mundo da computação paralela;

- ao meu grande amigo Bruno de Pádua Melo pela força no Inglês nas horas difíceis;

- a Rede de Supermercados São Francisco, empresa no qual trabalho, pela apoio para a conclusão deste curso;

- todos os colegas do Mestrado em Ciência da Computação da UEM.

"Ele não sabia que era impossível. Foi lá e fez."

Jean Cocteau

### Resumo

A busca por maior poder computacional tem motivado diversos pesquisadores da área de Arquitetura de Computadores a dedicar grandes esforços para vencer as limitações físicas impostas pelos equipamentos disponíveis atualmente.

O estudo de máquinas paralelas é foco de esforços de diversos pesquisadores desta área, assim como a simulação destas máquinas paralelas.

Desta forma, apresentamos neste trabalho o projeto e implementação de um Simulador de Multiprocessadores Superescalares de Memória Compartilhada (SMS-MC), baseado na estrutura do simulador SimpleScalar, um consagrado simulador de Arquitetura de Computadores.

O simulador permite realizar diversas análises relacionadas à memória compartilhada e protocolos de coerência de *cache*, gerando estatísticas para os *benchmarks* que nele podem ser executados.

Apresentamos ainda alguns *benchmarks* que foram desenvolvidos para demonstrar a utilização do simulador, mostrando suas funcionalidades e possibilidades de uso.

Finalizamos este trabalho apresentando algumas possíveis expansões para o simulador SMS-MC, que podem ser implementadas para aumentar a abrangência da ferramenta.

Palavras-Chaves: Memória Compartilhada, Coerência de Cache, SimpleScalar.

### Abstract

The quest for more computational power have motivated several researchers in the computer architecture area to dedicate a large amount of effort in overcoming the physical barriers imposed by the current available equipments.

The study of parallel machines is the focus of the efforts of many researchers in this area, and so is the simulation of these parallel machines.

We introduce in this work, the project and the implementation of a superscalar multiprocessor simulator with shared memory (SMS-MC), based on the SimpleScalar simulator structure, a well known simulator for computer architecture.

The simulator allows us to perform numerous analises over the shared memory and the cache coherence protocols, generating statistics for the benchmarks that can later be used in the simulator.

We present here some of the benchmarks that were developed to demonstrate the usage of the simulator, showing its functions and its uses.

We conclude this work by presenting some expansion possibilities for the SMS-MC simulator, which can be implemented to improve.

**Key words:** Shared Memory, Cache Coherence, SimpleScalar.

# Sumário

### Lista de Figuras

### Lista de Tabelas

| 1 | Intr | odução               |                               | p. 19 |  |  |  |

|---|------|----------------------|-------------------------------|-------|--|--|--|

| 2 | Arq  | quiteturas Paralelas |                               |       |  |  |  |

|   | 2.1  | Taxono               | omia de Flynn                 | p. 23 |  |  |  |

|   | 2.2  | Alguns               | s exemplos práticos           | p. 28 |  |  |  |

|   |      | 2.2.1                | Arquitetura FLASH             | p. 28 |  |  |  |

|   |      | 2.2.2                | Hydra                         | p. 28 |  |  |  |

|   |      | 2.2.3                | TRIPS                         | p. 29 |  |  |  |

|   |      | 2.2.4                | Simultaneous Multithreading   | p. 29 |  |  |  |

|   |      | 2.2.5                | Projeto Wisconsin Wind Tunnel | p. 29 |  |  |  |

|   |      | 2.2.6                | Projeto MIT Alewife           | p. 30 |  |  |  |

| 3 | Men  | nória C              | ompartilhada                  | p. 31 |  |  |  |

|   | 3.1  | Coerêr               | ncia de Cache                 | p. 32 |  |  |  |

|   |      | 3.1.1                | Directory Protocols           | p. 33 |  |  |  |

|   |      | 3.1.2                | Snoopy Protocols              | p. 34 |  |  |  |

|   | 3.2  | Polític              | as de Coerência               | p. 35 |  |  |  |

|   | 3.3  | O Prot               | ocolo Ilinois MESI            | p. 37 |  |  |  |

|   | 3.4  | O Prot               | ocolo Firefly                 | p. 38 |  |  |  |

| 4  | Sim    | uladores                                             | p. 41 |

|----|--------|------------------------------------------------------|-------|

|    | 4.1    | Trabalhos Relacionados                               | p. 42 |

|    | 4.2    | O Simulador SimpleScalar                             | p. 43 |

|    | 4.3    | Os Simuladores MULTIPROC e SMS                       | p. 44 |

| 5  | O si   | mulador SMS-MC                                       | p. 47 |

|    | 5.1    | Características                                      | p. 48 |

|    | 5.2    | Diferenciais                                         | p. 49 |

|    | 5.3    | Metodologia                                          | p. 49 |

|    |        | 5.3.1 Implementação da Memória Compartilhada         | p. 50 |

|    | 5.4    | Funcionamento do MESI                                | p. 51 |

|    |        | 5.4.1 Read hit                                       | p. 52 |

|    |        | 5.4.2 Read miss                                      | p. 52 |

|    |        | 5.4.3 Write hit                                      | p. 53 |

|    |        | 5.4.4 Write miss                                     | p. 54 |

|    | 5.5    | Implementação                                        | p. 54 |

|    | 5.6    | Utilização do Simulador                              | p. 57 |

| 6  | Exp    | erimentos e Resultados                               | p. 63 |

|    | 6.1    | Aplicativos simulados                                | p. 64 |

|    | 6.2    | Apresentação dos Resultados                          | p. 65 |

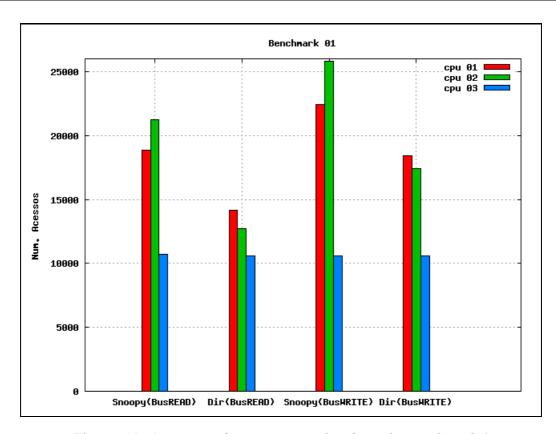

|    |        | 6.2.1 Benchmark 1: "Randomize"                       | p. 65 |

|    |        | 6.2.2 Benchmark 2: Produto de Vetores"               | p. 68 |

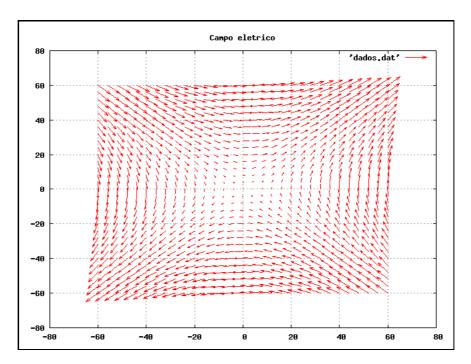

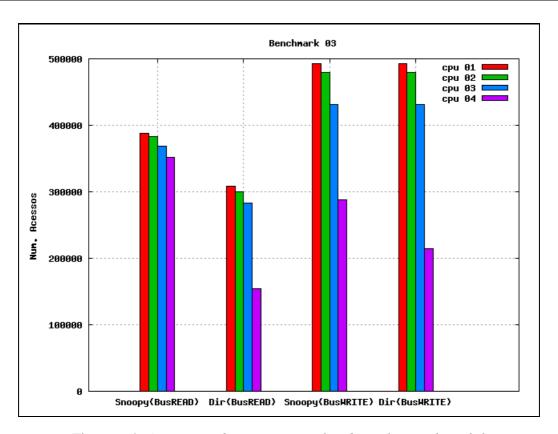

|    |        | 6.2.3 Benchmark 3: "Cálculo do Campo Elétrico"       | p. 71 |

|    |        | 6.2.4 Benchmark 4: "Versão customizada do Whetstone" | p. 74 |

| 7  | Con    | clusões e Trabalhos Futuros                          | p. 83 |

| Re | eferên | acias Bibliográficas                                 | p. 85 |

# Lista de Figuras

| 2.1 | Arquitetura SISD                                                                | p. 24 |

|-----|---------------------------------------------------------------------------------|-------|

| 2.2 | Arquitetura SIMD                                                                | p. 25 |

| 2.3 | Arquitetura MISD                                                                | p. 25 |

| 2.4 | Arquitetura MIMD                                                                | p. 26 |

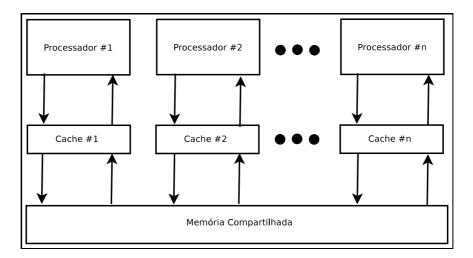

| 3.1 | Memória Compartilhada com Cache Individual por Processador                      | p. 32 |

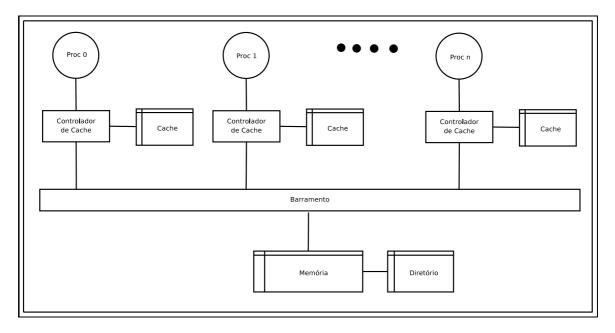

| 3.2 | Estrutura básica de uma cache que utiliza protocolo baseado em diretórios       | p. 33 |

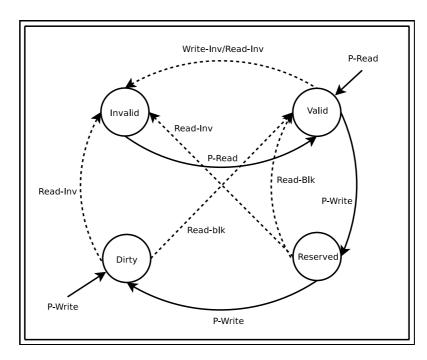

| 3.3 | Diagrama de Transições de estados dos protocolos com política write-invalidate. | p. 35 |

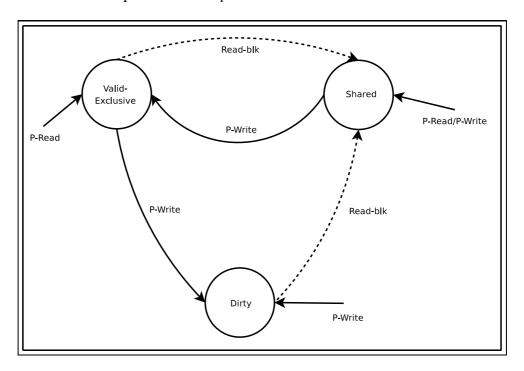

| 3.4 | Diagrama de Transições de estados dos protocolos com política write-update.     | p. 39 |

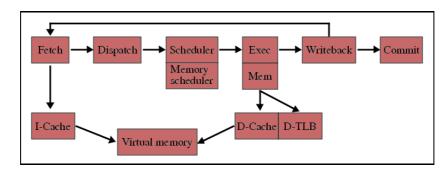

| 4.1 | Estrutura modular do sim-outorder - SimpleScalar                                | p. 44 |

| 6.1 | Acessos ao barramento realizados pelo Benchmark 1                               | p. 68 |

| 6.2 | Acessos ao barramento realizados pelo Benchmark 2                               | p. 71 |

| 6.3 | Gráfico do Campo Elétrico gerado pela aproximação de cargas elétricas           | p. 72 |

| 6.4 | Acessos ao barramento realizados pelo Benchmark 3                               | p. 75 |

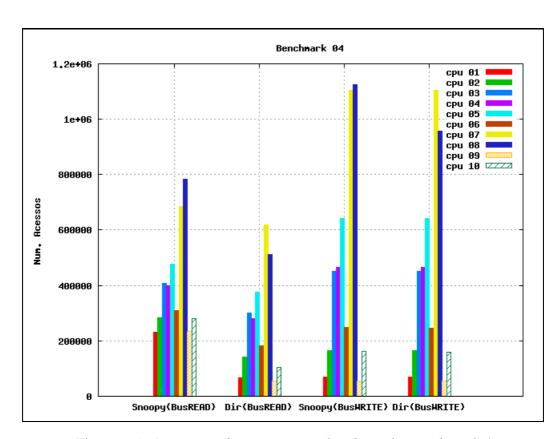

| 6.5 | Acessos ao barramento realizados pelo Benchmark 4                               | p. 79 |

# Lista de Tabelas

| 6.1 | Resultados do Benchmark 1                            | p. 67 |

|-----|------------------------------------------------------|-------|

| 6.2 | Resultados do Benchmark 2                            | p. 70 |

| 6.3 | Resultados do Benchmark 3                            | p. 80 |

| 6.4 | Resultados do Benchmark 4 para o Protocolo Snoopy    | p. 81 |

| 6.5 | Resultados do Benchmark 4 para o Protocolo Directory | p. 82 |

Neste capítulo apresentamos uma motivação para o estudo de arquiteturas paralelas, assim como uma classificação das mesmas baseada no sub-sistema de memória. Apresentamos também uma sucinta motivação ao uso de simuladores e uma visão geral da seqüência deste trabalho.

O aumento do poder de processamento tem sido cada vez mais almejado por diversas áreas da computação. Enquanto alguns pesquisadores buscam melhorar as técnicas empregadas no desenvolvimento dos processadores, tentando aumentar o desempenho (otimizando os circuitos lógicos internos), outros buscam melhorar técnicas de utilização destes *hardwares*, tentando na maioria das vezes agrupar equipamentos de menores portes visando obter maior capacidade computacional no conjunto do que com os *hardwares* isolados. Outros ainda buscam também dividir as tarefas em sub-tarefas menores, para que possam ser executadas em *hardwares* com diversos processadores, objetivando concluir o processamento num tempo menor.

Na área de Arquiteturas Paralelas busca-se fornecer meios e técnicas de utilizar *hardwares* com diversos processadores para conseguir o desempenho esperado. Máquinas Paralelas são foco de pesquisa, pois são capazes de atender a demanda de uma vasta gama de aplicações que requisitam alto desempenho.

Máquinas Paralelas podem ser classificadas em três categorias, com base no sub-sistema de memória:

- Memória Distribuída ( (NITZBERG; LO, 1991), (ZHOU et al., 1992), (MILTON, 1998) ): Neste modelo cada processador da arquitetura possui sua própria memória local, de forma que o programa executado em cada processador possui um espaço de endereçamento local, invisível aos outros processadores. Todas as tarefas de comunicação inter-processos devem ser feitas via troca de mensagens e fica a cargo do programador gerenciar este trânsito dos dados;

- Memória Compartilhada ( (COX et al., 1994), (DING; BHUYAN, 1992), (LEBLANC;

MARKATOS, 1992) ): Neste modelo todos os processadores compartilham o mesmo espaço de endereçamento, tornando possível que dados manipulados por um processador sejam visíveis aos demais processadores. As rotinas de comunicação inter-processos são feitas através do acesso a variáveis compartilhadas, o que permite que o programador não se preocupe com a forma na qual os dados trafegam entre os processadores ;

• Memória Compartilhada Distribuída ( (STUMM; ZHOU, 1990), (HENNESSY; HEINRICH; GUPTA, 1999), (DWARKADAS et al., 1999) ): Neste modelo, cada processador possui uma memória local, entretanto consegue acessar os espaços de endereçamento dos demais processadores. Todas as tarefas de movimentação e acesso aos dados são implementadas diretamente pelo *hardware*, utilizando rotinas de envio e recepção de mensagens. Este modelo tem sido foco de diversas pesquisas atuais (GOLAB et al., 2007), (ROGERS; PRVULOVIC; SOLIHIN, 2006), (GOLAB; HENDLER; WOELFEL, 2006), (ZHANG et al., 2006), (BARTON et al., 2006), (BASUMALLIK; EIGENMANN, 2006), (MALEN; LOTTIANUX, 2002), (THANALAPATI; DANDAMUDI, 2001), (STOLLER, 1998), (CIERNIAK; LI, 1995), pois busca associar as melhores qualidades dos modelos de memória compartilhada e memória distribuída, adicionando a possibilidade do programador poder distribuir os dados nas memórias locais da maneira que for mais interessante.

Diversos *hardwares* já são equipados com mais de um processador, mas devido ao custo nem sempre são acessíveis à maioria dos estudantes e até mesmo a algumas organizações de ensino, principalmente públicas. Desta forma, torna-se difícil investigar as técnicas e o funcionamento dessas arquiteturas multiprocessadas sem possuir um equipamento para trabalhar e realizar testes.

Tentando resolver este problema da dificuldade de se ter uma máquina paralela para pesquisas é que surge a idéia de se utilizar simuladores de arquiteturas, de memória, de redes de interconexão etc.

Dentro de um grande universo de simuladores de arquitetura de computadores, o Simple-Scalar (AUSTIN; LARSON; ERNST, 2002) se destaca por ser um *toolkit* de simulação que permite simular diversos níveis de abstração, incluindo memória, *caches*, previsores de desvios, *pipelines* entre outros dispositivos de *hardware*. A ferramenta SimpleScalar tem prestígio internacional, sendo intensamente utilizada por renomados pesquisadores da área de arquitetura de computadores. Diversos pesquisadores baseiam seus experimentos nesse *toolkit*.

Neste contexto, o objetivo do presente trabalho consistiu em viabilizar uma ferramenta de simulação para Arquitetura Paralela com Memória Compartilhada denominada SMS-MC (Simulador de Multiprocessadores Superescalares com Memória Compartilhada), com base no

núcleo do SimpleScalar.

Nesta dissertação é apresentada uma contextualização sobre os fundamentos de sistemas multiprocessados, modelos de memória (mais especificamente o modelo de memória compartilhada), simulação, incluindo uma revisão sobre os principais trabalhos relacionados dentro do escopo de simulação de arquiteturas paralelas e memória compartilhada. São discutidos também os protocolos de coerência de *cache*, a modelagem e implementação do SMS-MC e os testes e resultados aplicados a este simulador.

A estrutura desta dissertação está organizada da seguinte forma: o capítulo 2 apresenta uma revisão sobre Arquiteturas Paralelas, detalhando sua importância e apresentando a principal taxonomia para Arquiteturas Paralelas; o capítulo 3 apresenta os modelos de memória disponíveis em Arquiteturas Paralelas, detalhando os principais tipos de protocolos utilizados; o capítulo 4 apresenta uma revisão sobre os trabalhos relacionados; o capítulo 5 apresenta o Simulador SMS-MC proposto neste trabalho, descrevendo sua funcionalidade, implementação e recursos disponíveis; o capítulo 6 apresenta os resultados obtidos com o uso do simulador proposto, incluindo alguns exemplos de *benchmarks* desenvolvidos para o mesmo; o capítulo 7 discute as conclusões da pesquisa, as perspectivas para o uso da ferramenta proposta e possíveis trabalhos futuros baseados na ferramenta apresentada.

.

# 2 Arquiteturas Paralelas

Neste capítulo apresentamos uma das taxonomias mais aceitas na área de arquitetura de computadores, a taxonomia de Flynn, incluindo suas estruturas e principais exemplos. Situamos o simulador apresentado neste trabalho dentro desta taxonomia e introduzimos o problema da coerência de cache nas máquinas paralelas com memória compartilhada e caches individuais.

É fácil notar que sistemas computacionais com elevado poder de processamento têm se tornado cada vez mais importantes e necessários nas atividades e pesquisas atuais. No entanto, com o constante crescimento deste poder computacional, cada vez mais a velocidade de processamento de instruções, acesso à memória e armazenamento está aproximando-se do seu limite físico.

Como tentativa de contornar este problema, pesquisadores buscam desenvolver novos métodos para atingir maior poder computacional, sendo um deles a tentativa de agrupar recursos computacionais (processadores, memórias) de maneira que possam trabalhar em sinergia, provendo maior poder computacional do que um único processador poderia fornecer. Quase que naturalmente o paralelismo torna-se uma das alternativas para a superação desta limitação.

Sendo as Arquiteturas Paralelas foco principal deste trabalho, faz-se necessária uma discussão acerca da taxonomia de Arquiteturas Paralelas.

### 2.1 Taxonomia de Flynn

Provavelmente a classificação de arquiteturas de computadores mais amplamente conhecida seja a sugerida por Flynn (FLYNN, 1972). A taxonomia de Flynn tem como base os conceitos de fluxo de instruções e fluxo de dados. A classificação de Flynn identifica quatro categorias de arquiteturas:

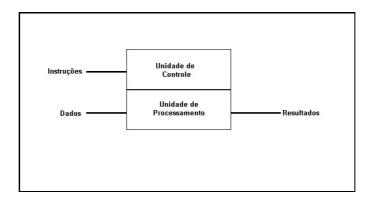

• SISD (Single Instruction / Single Data) : Este modelo representa as máquinas com

Figura 2.1: Arquitetura SISD

um único fluxo de instruções e um único fluxo de dados. Estas máquinas não exploram paralelismo de dados nem de instruções. A execução ocorre de forma seqüencial. Neste modelo inclui-se a máquina originalmente proposta por von Neumann, os PCs e alguns *mainframes*. A Figura 2.1 mostra a estrutura básica da classe SISD.

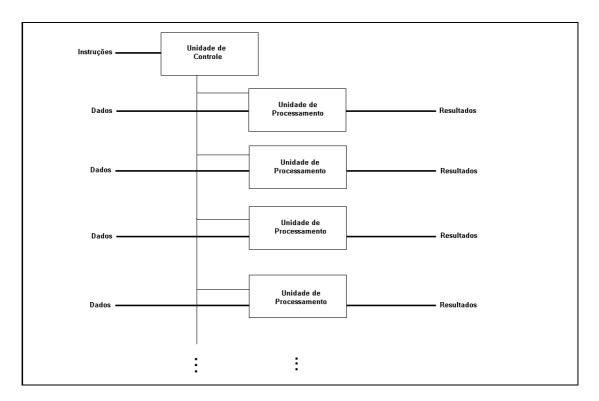

- SIMD (Single Instruction / Multiple Data): Este modelo inclui máquinas com vários processadores, capazes de executar uma mesma instrução sobre um conjunto de dados independente em cada processador. Alguns processadores, conhecidos como processadores vetoriais, enquadram-se nesta categoria, sendo utilizados principalmente em operações matemáticas que envolvam matrizes e vetores. A Figura 2.2 ilustra a estrutura desta classe de máquinas. Exemplos desta categoria são: ILLIAC-IV, PEPE, BSP, STARAN, MPP, DAP e CM-1.

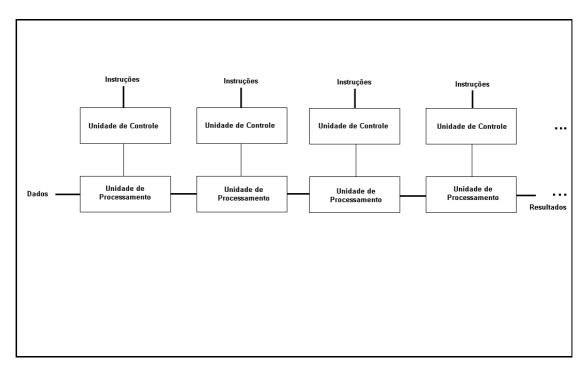

- MISD (Multiple Instruction / Single Data): Este modelo representa as máquinas capazes de executar diversas instruções sobre uma mesma seqüência de dados. Acredita-se que esta classe de máquinas seja praticamente vazia. A Figura 2.3 mostra a estrutura das máquinas da classe MISD.

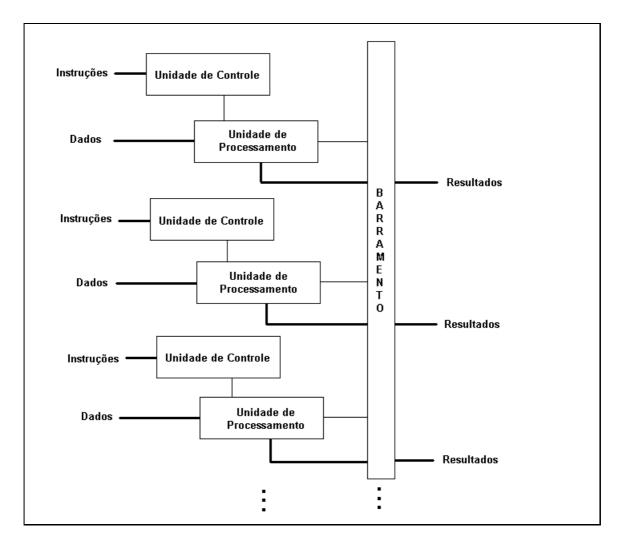

- MIMD (Multiple Instruction / Multiple Data): Este modelo, o mais avançado na taxonomia, representa as máquinas capazes de executar diferentes instruções sobre diferentes massas de dados. Nesta categoria enquadram-se praticamente todas as máquinas paralelas, que no geral utilizam diversos processadores e memórias, sendo controladas por um único núcleo de sistema operacional. A Figura 2.4 expõe a estrutura básica de uma máquina desta classe. Algumas características que subdividem as máquinas do modelo MIMD são: quantidade de processadores, redes de interconexão, tipos de memória e caches.

Figura 2.2: Arquitetura SIMD

Figura 2.3: Arquitetura MISD

Figura 2.4: Arquitetura MIMD

Neste trabalho, apresentamos a implementação de um simulador de arquiteturas que enquadra-se no modelo MIMD. Neste modelo são muito comuns dois tipos de sub-sistemas de memória: os baseados em memória distribuída e os baseados em memória compartilhada.

Os multicomputadores de memória distribuída são caracterizados pela presença de um espaço de endereçamento exclusivo a cada processador, que não pode ser acessado pelos outros processadores. Uma de suas vantagens é o baixo custo quando deseja-se ampliar a capacidade da memória, principalmente quando comparado com o outro modelo. Entretanto, quando utilizados com aplicações que exigem muita comunicação inter-processos, apresentam queda de desempenho.

Os sistemas com memória compartilhada possuem espaços de endereçamento comuns a todos os processadores. Estão sujeitos a diversos problemas relacionados a coerência dos dados, considerando que cada processador pode executar instruções independentes, tentando alterar o mesmo endereço de memória. Uma das principais vantagens deste tipo de máquina é que fornece um modelo de programação simples, facilitando o desenvolvimento de aplicativos paralelos.

Considerando a disputa que ocorre nos multiprocessadores de memória compartilhada pelo uso destes recursos compartilhados, a latência do acesso à memória tende a aumentar, prejudicando seu desempenho.

Uma das soluções diretas para este problema é o uso de *caches*, que podem ser tanto privadas quanto compartilhadas, sendo as caches privadas mais interessantes pois tendem a atender a maioria das referências à memória localmente.

Entretanto, a utilização de *caches* privadas introduz um outro problema no contexto, que é a "Coerência de Cache". Este problema ocorre devido à possibilidade de existirem múltiplas cópias de um mesmo dado em diferentes *caches* simultaneamente, possibilitando que haja uma visão inconsistente da memória.

Para solucionar este problema de "Coerência de Cache" podem ser utilizadas soluções baseadas em *software* ou *hardware*. Comercialmente os métodos baseados em *hardware* são mais utilizados, sendo conhecidos como "Protocolos de Coerência de Cache".

A implementação do simulador descrito neste trabalho inclui dois modelos de protocolos de coerência de *cache*, ou seja, duas soluções para coerência baseadas em *hardware*. A estrutura disponibilizada neste simulador permite que novos protocolos sejam incluídos sem qualquer interferência nos recursos que já estão disponíveis no mesmo.

### 2.2 Alguns exemplos práticos

Alguns projetos de máquinas paralelas vem sendo desenvolvidos por grupos de pesquisa no mundo todo. Apresentamos, a seguir, alguns exemplos que representam uma parte da pesquisa na área.

### 2.2.1 Arquitetura FLASH

A arquitetura FLASH (*FLexible Architecture for SHared memory*) (KUSKIN et al., 1994) foi um projeto desenvolvido pela Universidade de Stanford, com objetivo de fornecer um multi-processador escalável, capaz de suportar diversos modelos de comunicação, incluindo memória compartilhada e protocolos de troca de mensagens.

A chave deste projeto foi o desenvolvimento de um controlador, chamado MAGIC (*Memory And General Interconnect Controller*), que é um chip baseado no *Protocol Processor*, uma *engine* baseada no projeto do processador TORCH.

O MAGIC executa basicamente duas tarefas: movimentação de dados e manipulação de estados. Assim, ele explora a independência que existe entre as tarefas separando o controle do processamento dos dados.

O projeto FLASH foi desenvolvido pela Universidade de Stanford em parceria com o ITO (*Information Technology Office*) e colaboração da *MIPS Technologies*.

### 2.2.2 Hydra

Hydra (WULF, 1981) é o projeto de uma nova microarquitetura de multiprocessadores com caches compartilhadas, novos mecanismos de sincronização, tecnologia de circuitos integrados avançados e tecnologia de compiladores paralelos. No Hydra, quatro processadores de alto desempenho são integrados numa única pastilha.

O Hydra usa um único chip de cache compartilhada, melhorando assim o desempenho relativo à largura de banda e latência entre os múltiplos processadores. Utilizando um único chip, a comunicação inter-processos e a latência na sincronização são comparadas com implementações de multiprocessadores baseados em barramento.

#### **2.2.3 TRIPS**

O projeto TRIPS (SANKARALINGAM et al., 2006) é um projeto que visa desenvolver uma nova classe de tecnologia escalável e de multiprocessadores de alto desempenho chamados EDGE (*Explicit Data Graph Execution*) (BURGER et al., 2004).

O primeiro membro da arquitetura EDGE foi chamado de TRIPS, sendo desenvolvido na Universidade do Texas, em Austin. O TRIPS fornece concorrência de instruções de alto-nível e consequentemente alto desempenho, sem necessitar de mudanças no modelo de programação.

#### 2.2.4 Simultaneous Multithreading

O *Simultaneous Multithreading* (SMT) (Susan J. Eggers and Joel S. Emer and Henry M. Levy and Jack L. Lo and Rebecca L. Stamm and Dean M. Tullsen, 1997) é um modelo de processador que combina a tecnologia de *hardware multithreading* com processadores superescalares, permitindo que múltiplas *threads* tenham instruções executadas em cada ciclo.

Diferentemente de muitas outras arquiteturas *multithreads*, em que um único contexto está ativo num dado ciclo, o SMT permite que todos os contextos de *threads* possam simultaneamente competir por recursos.

O projeto do *Simultaneous Multithreading* foi desenvolvido pela Universidade de Washington.

### 2.2.5 Projeto Wisconsin Wind Tunnel

O projeto Wisconsin Wind Tunnel (REINHARDT et al., 1993) é focado no desenvolvimento de máquinas paralelas com suporte a memória compartilhada.

O projeto é dividido em três fases:

- a primeira fase examina as memórias compartilhadas colaborativas, que simplificam o hardware de memória compartilhada, permitindo ao software gerenciar a movimentação dos dados;

- a segunda fase propõe uma interface que permite aos programadores implementar e utilizar troca de mensagens, memória compartilhada ou uma combinação híbrida entre estes dois modelos de comunicação inter-processos;

• a terceira fase busca utilizar previsão e especulação para aumentar o desempenho, reduzindo a latência de comunicação.

### 2.2.6 Projeto MIT Alewife

O Alewife (AGARWAL et al., 1995) é um multiprocessador de grande escala que integra coerência de cache, memória compartilhada distribuída e troca de mensagens num único framework de hardware integrado.

Cada nó do Alewife usa uma unidade de inteiros *Sparcle* de 33MHz, 64KBytes de cache e 4MBytes de memória principal compartilhada. Os nós trocam mensagens entre si através de uma rede de interconexão *mesh*.

# 3 Memória Compartilhada

Neste capítulo apresentamos uma visão geral sobre memórias compartilhadas e o problema da coerência de cache que surge nesta arquitetura. Apresentamos algumas soluções baseadas em software e hardware. Os Directory Protocols e os Snoopy Protocols são apresentados e exemplificados. Dois exemplos de protocolos baseados nas políticas write-invalidate e write-update são descritos e detalhados.

Este tipo de memória, muito utilizada em máquinas multiprocessadas, permite que todos os processadores utilizem o mesmo espaço de endereçamento, facilitando o trabalho do programador, pois evita que ele tenha que se preocupar com a maneira com a qual os dados trafegam entre os processadores (como é o caso da memória distribuída), tornando mais simples as tarefas de comunicação inter-processos.

Entretanto, o programador precisa atentar-se à maneira como os dados são divididos entre os processadores, evitando que ocorram conflitos nos acessos e reduzindo as tarefas de sincronização.

Os sistemas de memória compartilhada podem ser implementados tanto com memórias centralizadas quanto com memórias distribuídas, sendo que em ambos os casos, geralmente existe uma memória *cache* associada a cada processador visando reduzir a latência.

Isso cria um outro tipo de problema nesta arquitetura: a coerência de *cache*. Como cada processador possui sua *cache* local, diversas cópias de um dado compartilhado podem existir. Para tratar este problema existem os protocolos de coerência de *cache*, que servem para realizar as operações nas *caches* locais de modo a manter a coerência dos dados.

Nestes sistemas de memória compartilhada, as operações de leitura / escrita precisam ser controladas para que os dados mantenham-se coerentes. Assim, instruções de leitura concorrentes podem ser executadas sem muita preocupação pelos programadores, entretanto, todas as operações de escrita em memória precisam ser implementadas de forma atômica, evitando que valores escritos sejam perdidos.

3.1 Coerência de Cache 32

Figura 3.1: Memória Compartilhada com Cache Individual por Processador

Estes controles que devem existir numa arquitetura de memória compartilhada retiram do programador a necessidade de preocupar-se com detalhes de acessos e transferências de dados, mas aumentam a complexidade do *hardware* que fará o controle destes acessos simultâneos.

#### 3.1 Coerência de Cache

Como explicado anteriormente, o problema da "Coerência de Cache" ocorre quando utilizase memória compartilhada com *caches* individuais nos múltiplos processadores. Desta forma, diversas cópias de um mesmo dado podem existir nas memórias *caches* simultaneamente. Caso os processadores realizem livremente atualizações em suas *caches*, uma visão inconsistente da memória será formada, o que pode induzir a um mal funcionamento do programa em execução.

As soluções para este problema podem ser desenvolvidas tanto em *software* quanto em *hardware*. As soluções baseadas em *software* limitam-se a separar os dados que podem ser alocados nas memórias *caches* e os que não podem. Resumidamente, um novo rótulo é adicionado aos endereços, dizendo se são "*cachebles*" ou "*non-cachebles*". Assim, dados compartilhados não podem ser armazenados nas *caches* dos processadores, garantindo que não existam diversas cópias deste mesmo dado.

As soluções baseadas em *hardware*, também conhecidas como "Protocolos de Coerência de Cache" são comercialmente mais utilizadas (STENSTRÖM, 1990). Estas soluções tratam o problema de coerência de *cache* utilizando reconhecimento dinâmico de inconsistência dos dados em tempo de execução. Uma das grandes vantagens deste tipo de implementação é que ela não exige qualquer responsabilidade do programador ou do compilador relativa à manutenção de coerência de *cache*.

3.1 Coerência de Cache 33

Entre os protocolos implementados em *hardware* existe ainda uma divisão, que representa a forma com que os dados são distribuídos entre os processadores: os *Directory Protocols* (baseados num diretório centralizado ou distribuído) e os *Snoopy Protocols* (baseados em barramento compartilhado).

Outra característica que diferencia os protocolos de coerência de cache é a quantidade de estados que cada protocolo implementa. Os protocolos mais simples e que apresentam desempenho um pouco reduzido possuem de três a cinco estados e exigem maior complexidade na tarefa de manter a coerência. Os protocolos mais elaborados possuem quantidades maiores de estados e oferecem um desempenho superior, exigindo menor complexidade para manter a coerência.

As próximas duas sub-seções discutem Directory Protocols e Snoopy Protocols.

#### 3.1.1 Directory Protocols

Este tipo de protocolo possui uma estrutura (em forma de diretório, tabela) que armazena informações sobre os dados contidos nas diversas *caches* locais, ou seja, possui toda a informação sobre em qual *cache* determinado dado está e qual o seu estado.

Sempre que uma nova requisição de leitura ou escrita é feita para uma memória *cache* local, o diretório é verificado para tomar-se as devidas ações nas *caches* remotas de modo a manter a coerência dos dados.

Figura 3.2: Estrutura básica de uma cache que utiliza protocolo baseado em diretórios.

De modo geral, os diretórios são armazenados na memória principal e representam cada

3.1 Coerência de Cache 34

bloco de memória como um mapa de *bits*, indicando a presença do bloco nas diversas *caches*. Cada *bit* deste vetor representa o estado do bloco em uma das *caches* locais.

A Figura 3.2 mostra a estrutura básica de um sistema com diversos processadores e suas respectivas *caches* locais, assim como a estrutura do protocolo baseado em diretórios.

Este tipo de protocolo apresenta a desvantagem de utilizar um único ponto central para pesquisa no diretório e ainda o elevado *overhead* de comunicação entre os controladores de *cache* locais e o diretório centralizado.

Por outro lado, diferentemente dos protocolos *Snoopy* (descritos a seguir), as operações realizadas pelo controlador de *cache* não precisam enviar mensagens utilizando *broadcast* para as demais *caches*, direcionando as mensagens somente para as *caches* que sabe-se conterem os dados compartilhados que estejam sendo manipulados no momento.

Um exemplo clássico deste protocolo é a implementação do DASH, criado pela Universidade de Stanford para seu multicomputador que usa uma rede bi-dimensional para comunicação entre os processadores (LENOSKI et al., 1990).

#### **3.1.2** Snoopy Protocols

Os *Snoopy Protocols* utilizam um barramento compartilhado onde enviam mensagens de *broadcast* para avisar as demais *caches* sobre suas operações nos dados. Todas as *caches* "escutam" as mensagens deste barramento e verificam seus dados para avaliar se necessitam realizar alguma ação para manter a coerência dos dados no sistema como um todo.

Antes de realizar qualquer operação sobre um dado na *cache*, o protocolo verifica se é necessário consultar as demais *caches* sobre seus estados e caso necessário encaminha as devidas mensagens pelo barramento. Dependendo das mensagem recebidas, o controlador da *cache* aguarda as confirmações das outras *caches* para que possa efetivar a operação.

A principal diferença entre uma *cache Snoopy* e uma *cache* em sistemas uni-processadores está no controlador de *cache* e o uso do barramento compartilhado. No caso das *caches Snoopy*, o controlador de *cache* é uma máquina de estados finitos que implementa um protocolo de coerência de *cache*. A Figura 3.3 mostra o diagrama de transições de estados que exemplifica o funcionamento da máquina de estados finitos utilizada na implementação dos protocolos *write-invalidate*.

Este tipo de protocolo difere dos baseados em diretório principalmente pelo fato de não utilizar um controle centralizado, sendo caracterizado pelo controle distribuído das *caches*.

Figura 3.3: Diagrama de Transições de estados dos protocolos com política write-invalidate.

#### 3.2 Políticas de Coerência

Os *Directory Protocols* e os *Snoopy Protocols* podem possuir duas políticas de escrita fundamentais:

- Write-Invalidate: Este tipo de implementação, também conhecida como "Baseada em Invalidação", envia mensagens de invalidação às demais caches caso uma operação de escrita seja solicitada na cache local. Permite que diversas caches possuam o dado no modo "leitura", mas somente uma cache com o dado no modo "escrita". Toda escrita em blocos compartilhados começa com a invalidação do mesmo dado em todas as outras caches. Depois que a cache obtém o privilégio de escrever no bloco, todas as demais escritas subseqüentes deste mesmo bloco que forem necessárias nesta mesma cache podem ser executadas até que outra cache solicite permissão de leitura ou escrita para este bloco. São exemplos de implementação deste tipo de protocolo: Synapse (RAINA, 1992), Berkeley (KATZ et al., 1985) e Ilinois MESI (Mark S. Papamarcos and Janak H. Patel, 1984).

- Write-Update: Este tipo de implementação, também conhecida como "Baseada em Atualização", envia mensagens com o dado atualizado para todas as demais caches, permitindo que o dado permaneça coerente em todas as caches do sistema. São exemplos de implementação deste protocolo: Firefly (THACKER; STEWART, 1987) e Dragon (ARCHIBALD; BAER, 1986).

O funcionamento dos protocolos baseados na política *write-invalidate*, geralmente implementados como protocolos de quatro estados (*MESI*, descrito nas seções seguintes) é baseado nas seguintes primitivas (STENSTRÖM, 1990):

- Read hit: sempre podem ser executados localmente nas caches, não ocorrendo qualquer mudança de estado na cache local ou nas caches remotas. Isto ocorre porque o dado válido já está disponível na cache local;

- Read miss: se nenhuma cópia alterada do dado existe em qualquer outra cache, o valor do dado na memória é o atual e válido. Este valor (da memória) é consistente e pode ser passado à cache que precisa do dado para fornecer a leitura solicitada por seu processador. Se uma cópia alterada do dado existir em qualquer outra cache, a cache com o dado alterado atualiza a memória e o dado é enviado para a cache solicitante. Neste último caso, ambas as caches terão dados válidos e a memória estará atualizada também, isto porque a operação era de leitura;

- Write hit: se a cópia do dado compartilhado está presente na cache e está no estado exclusivo ou alterado, então a operação de escrita pode ser realizada localmente na cache e o novo estado do bloco de dados da cache será alterado. Se o bloco de dados existe em alguma das outras caches remotas, uma mensagem solicitando a invalidação do bloco deve ser enviada para todos os outros controladores de cache, assim, a operação de escrita pode ser executada localmente e o novo estado passa a ser alterado;

- Write miss: o dado existe em alguma das caches remotas com o estado alterado, exigindo que o valor do dado na memória seja atualizado. Uma solicitação de invalidação de leitura é enviada a todas as caches, garantindo que ninguém possua qualquer cópia do dado, mesmo que em modo leitura, pois a cache local pretende realizar uma operação de escrita no bloco. Após as confirmações, o dado é atualizado localmente na cache e seu novo estado passa a ser alterado;

- *Replacement*: se o dado encontra-se alterado na *cache* este valor precisa ser atualizado na memória principal.

Já os protocolos baseados na política *write-update* funcionam baseados nas seguintes primitivas (STENSTRÖM, 1990):

Read hit: sempre podem ser executados localmente nas caches, não ocorrendo qualquer mudança de estado na cache local ou nas caches remotas. Isto ocorre porque o dado válido já está disponível na cache local;

- Read miss: caso hajam cópias compartilhadas do bloco, a cache com o dado válido fornece o dado para a cache que precisa do mesmo. Caso o estado do bloco seja alterado, a cache remota que possui o dado atualiza a memória (realizando um write-back) e muda o estado do bloco na sua cache para válido. Assim, a cache solicitante pode ler o bloco da memória e ambas passam a possuir o bloco com estado compartilhado;

- Write hit: se o bloco já existir na cache local, com os estados válido, exclusivo ou alterado, a operação de escrita pode ser realizada normalmente na cache local, e o novo estado do bloco passa a ser alterado. Se o estado do bloco é compartilhado, todas as outras cópias do bloco são atualizadas, incluindo a memória. Neste caso todas as caches que possuem o bloco passam a utilizar o estado compartilhado para o bloco;

- Write miss: o dado não está presente na cache local. Caso outras caches possuam o dado, ele é então atualizado na memória e devolvido à cache solicitante que pode então realizar sua atualização no valor do dado e novamente replicar sua alteração para todas as demais caches que possuam o bloco. Neste caso, todas as caches que possuem o bloco utilizam o estado compartilhado para ele. Caso nenhuma outra cache possua o dado no momento da solicitação de escrita, o controlador de cache lê o dado da memória, atualiza-o e utiliza o estado alterado na sua cópia do dado;

- *Replacement*: se o dado encontra-se alterado na *cache* este valor precisa ser atualizado na memória principal.

Os *Snoopy Protocols* são muito populares pela sua facilidade de implementação e utilizados em *Symmetric Multiprocessors Systems* como o Alliant FX da *Alliant Computer Systems* que utiliza políticas *write-invalidate* para manter a coerência de suas *caches* (STENSTRÖM, 1990).

Os *Snoopy Protocols* baseados em invalidação são utilizados em processadores das fabricantes Intel e AMD, duas das maiores fabricantes de processadores no mundo atualmente. O Ilinois MESI é uma das implementações desta categoria de protocolos que melhor representa a classe, sendo, portanto, detalhado de maneira mais aprofundada na seção seguinte. Este protocolo também é implementado no simulador SMS-MC.

### 3.3 O Protocolo Ilinois MESI

O protocolo MESI (também conhecido como *Protocolo de Ilinois*) possui este nome devido aos seus quatro possíveis estados: *Modified, Exclusive, Shared e Invalid.* É o principal repre-

sentante da categoria dos protocolos baseados em invalidação, podendo ser implementado tanto como um protocolo "*Snoopy*" quanto um protocolo "*Directory based*".

É um dos protocolos mais utilizados comercialmente, sendo inclusive utilizado pela Intel para suportar a implementação de *caches write-back* da linha *Pentium* em substituição às *caches write-through* da linha *486*.

Os estados utilizados no protocolo MESI possuem um significado específico para cada letra:

- Modified: Indica que a linha de dados da cache encontra-se modificada, divergindo do

conteúdo da memória. Neste estado, o dado está disponível somente na cache local.

- *Exclusive*: Indica que o dado encontra-se presente somente nesta *cache* e que possui o mesmo valor que existe fisicamente na memória.

- *Shared:* Indica que a linha da *cache* possui o mesmo valor que o conteúdo da memória e pode estar presente neste mesmo modo em alguma outra *cache* do sistema.

- *Invalid:* Neste estado, a linha de *cache* não possui dados válidos.

O funcionamento do *Ilinois MESI* segue a política *write-invalidate*, conforme descrita nas seções anteriores.

# 3.4 O Protocolo Firefly

Este protocolo, representante da categoria dos protocolos baseados em atualização, foi desenvolvido por um laboratório de pesquisas da *DEC* (*Digital Equipament Corporation*)<sup>1</sup> para uso em sua estação de trabalho multiprocessada *DEC Firefly - MicroVAX-2* (ARCHIBALD; BAER, 1986).

O protocolo é implementado com três estados: *Private, Shared e Dirty*.

- O estado "private" é utilizado quando o bloco de cache está presente somente na cache local e possui o mesmo valor que o da memória.

- O estado "shared" representa que o bloco de cache está presente em mais de uma cache e possui o mesmo valor que o da memória.

- O estado "dirty" é usado para representar que o bloco de cache está presente somente na cache local e seu valor difere do valor armazenado na memória.

<sup>&</sup>lt;sup>1</sup>Hoje este laboratório faz parte dos laboratórios da HP - Hewlett-Packard.

Para manter a consistência, este protocolo propaga a alteração de um dado para as demais *caches* todas as vezes que uma atualização ocorre, garantindo assim que todas as *caches* que possuem o dado estejam com a cópia mais recente dele.

O funcionamento do protocolo *Firefly* segue a política *write-update*, descrita nas seções anteriores.

O diagrama de estados deste protocolo é baseado na Figura 3.4, que mostra as transições de um protocolo baseado na política *write-update*.

Figura 3.4: Diagrama de Transições de estados dos protocolos com política write-update.

.

# 4 Simuladores

Neste capítulo apresentamos as motivações para o uso de simuladores no estudo de arquitetura de computadores. Descrevemos também alguns simuladores disponíveis nesta área, discutindo suas principais características.

Nem sempre se tem em mãos todos os materiais necessários para pesquisa ou estudo em determinada área. Isso torna-se ainda mais evidente quando estes materiais de estudo possuem custo muito elevado. Ainda existem os casos em que o que está sendo proposto nas pesquisas não existe atualmente no mercado.

Os simuladores são uma boa alternativa para estes e outros problemas. Podem ser empregados para suprir a falta de um equipamento ou até mesmo para testar o funcionamento e desempenho de algo que só existe ainda em projeto. Com isto, os pesquisadores podem executar seus programas e avaliar a corretude do modelo proposto sem que o *hardware* seja fisicamente implementado.

Assim, é comum o uso de simuladores nos projetos de novas arquiteturas, principalmente buscando avaliar as características de desempenho destes projetos, sem que seja construído fisicamente o protótipo do que se projetou. Este tipo de uso facilita o conhecimento e avaliação dos parâmetros arquiteturais, facilitando os ajustes antes que o protótipo real seja construído e avaliado.

Comum também é o uso de simuladores para o estudo de arquiteturas que não possuem fácil acesso, seja pelo custo ou pela escassez de exemplares do *hardware*.

Na área de Arquitetura de Computadores existem diversos simuladores disponíveis, cada qual abrangendo uma determinada sub-área da arquitetura, facilitando os estudos e avaliações de parâmetros de configuração de equipamentos.

### 4.1 Trabalhos Relacionados

Diversos simuladores têm sido desenvolvidos para prover suporte às pesquisas na área de Arquitetura de Computadores. Variam principalmente em complexidade e eficiência de execução, dependendo do nível de detalhamento que o simulador oferece.

O SimpleScalar (BURGER; AUSTIN, 1997), por exemplo, é um simulador dirigido por execução, cujas principais vantagens são a alta flexibilidade, portabilidade, desempenho e facilidade de expansão. A principal desvantagem deste simulador é que ele modela uma arquitetura monoprocessada.

Um outro simulador baseado no SimpleScalar, que mantém todas as suas características e adiciona a funcionalidade de simular um ambiente multiprocessado com memória distribuída é o MULTIPROC (GONÇALVES, 2000). Este simulador emula o funcionamento de diversos processadores (como numa arquitetura paralela), permitindo que vários aplicativos sejam executados simultaneamente em cada um dos processadores. Uma das dificuldades encontradas neste simulador é que ele não permite que os processos se comuniquem uns com os outros, além de simular somente o modelo de memória distribuída.

Para tratar a comunicação inter-processos no MULTIPROC, foi desenvolvido o simulador SMS (SANDRI; MARTINI; GONÇALVES, 2004), que toma como base o MULTIPROC e implementa rotinas de troca de mensagens entre os processos (programas simulados). Este simulador permite que os processos troquem informações entre si, mas mantém o modelo de memória distribuída.

Diversos outros simuladores foram desenvolvidos e são apresentados sucintamente a seguir.

O Limes (MAGDIC, 1997) implementa um simulador multiprocessado com memória compartilhada, utiliza *threads* para simular o multiprocessamento. Exige que a aplicação seja implementada com certas macros (desenvolvidas pelo *Argonne National Lab*) para definir o nível de paralelismo da mesma. Executa em ambientes Linux. Suporta o modelo de *threads* (processos leves) e implementa alguns protocolos de coerência de *cache* (WTI, Berkeley, Dragon e WIN). O grande diferencial deste simulador é que permite que os protocolos de coerência sejam descritos numa linguagem semelhante à VHDL, facilitando testes de novos protocolos.

O Proteus (BREWER et al., 1992) é um simulador bastante complexo; simula multiprocessadores, fornece bibliotecas de troca de mensagens e gerenciamento de memória e *threads*.

O RSIM (HUGHES et al., 2002) modela em detalhes uma arquitetura superescalar e é bastante utilizado nas simulações envolvendo *cache*. Foi desenvolvido seguindo a descrição do

processador MIPS R10000. Seu objetivo é considerar o modelo de memória e *cache* utilizados pelo processador na avaliação do desempenho da arquitetura.

O MINT (VEENSTRA J.E.; FOWLER, 1994) modela uma arquitetura MIPS (R3000 em específico) e também utiliza *threads* para simular um ambiente multiprocessado.

O ABSS (SUNADA; GLASCO; FLYNN, 1998) é principalmente utilizado para simulações de memória. Seus executáveis têm a restrição de executar em *hardware* Sparc UltraStation ou superiores que suportem o SPARC v9.

O Tango Lite (HERROD, 1993) simula um ambiente multiprocessado de memória compartilhada utilizando *threads*. Ele permite que os códigos sejam escritos em C e Fortran, suportando a plataforma MIPS R3000.

Naraig Manjikian, em alguns trabalhos (MANJIKIAN, 2001b) (MANJIKIAN, 2001a) discute também sobre alterações feitas por ele no código do SimpleScalar para suportar multiprocessamento utilizando *threads*. Ele implementa uma interface gráfica para visualizar os acessos à memória em sistemas monoprocessados e multiprocessados, assim como depurar códigos no simulador multiprocessado.

A utilização destes simuladores aplica-se tanto para a análise de desempenho das arquiteturas que eles representam quanto para a experimentação de parâmetros arquiteturais, como largura de barramento, métodos de acesso à memória e comunicação inter-processos.

### 4.2 O Simulador SimpleScalar

Como discutido anteriormente, diversos simuladores de arquiteturas encontram-se disponíveis atualmente, entretanto um dos mais difundidos e consolidado mundialmente é o *Toolkit Simple-Scalar*. Ele é utilizado amplamente nas maiores universidades e centros de pesquisa do mundo para investigações referentes à arquitetura de computadores.

Desenvolvido pela Universidade de Wisconsin-Madison, o *SimpleScalar* fornece um conjunto de simuladores e ferramentas para simulação que permitem ao usuário fazer diversos níveis de análise de desempenho em processadores superescalares. O simulador é disponibilizado gratuitamente pela Universidade para fins não comerciais.

O *Toolkit SimpleScalar* fornece diversos simuladores, com graus diferentes de especificidade, podendo ser utilizado para simulações envolvendo caches, previsores de desvio, acessos à memória, emissão de instruções fora de ordem, caches não-bloqueantes e execução expeculativa.

Figura 4.1: Estrutura modular do sim-outorder - SimpleScalar

O *SimpleScalar* fornece um compilador *gcc* específico que gera código *assembly Simple-Scalar* para aplicativos desenvolvidos em C, o que permite que *benchmarks* escritos em linguagem C possam ser compilados e testados no simulador.

A arquitetura do SimpleScalar é derivada do MIPS-IV ISA com algumas pequenas diferenças:

- operações de *load* e *store* suportam dois modos de endereçamento: registrador+registrador e auto-incremento/decremento:

- uma operação de raiz quadrada;

- um formato de instrução estendida de 64 bits.

O *SimpleScalar* usa um espaço de endereçamento de memória virtual com 31 *bits* de endereço. A arquitetura é toda definida num arquivo chamado *ss.def*, em que um conjunto de *macros* define cada uma das instruções.

O simulador mais detalhado disponível no *Toolkit* é o *sim-outorder*, que implementa emissão e execução de instruções fora de ordem baseado na técnica da "*Register Update Unit*" (SOHI, 1990), que faz uso dos *reorder buffers*.

Este simulador, assim como os demais do *Toolkit* é uma ferramenta modular, o que facilita a sua expansão, tornando-o um simulador muito utilizado como base para o desenvolvimento de novas ferramentas de simulação.

A estrutura modular do SimpleScalar sim-outorder pode ser vista na Figura 4.1.

### 4.3 Os Simuladores MULTIPROC e SMS

O simulador MULTIPROC foi desenvolvido tendo como base o *simulador sim-outorder*, do *Toolkit SimpleScalar*. Ele é baseado na replicação das estruturas do simulador *sim-outorder*,

comportando-se como um conjunto de simuladores sim-outorder executando paralelamente.

O SMS por sua vez, foi baseado no simulador MULTIPROC, que já implementava o multiprocessamento, entretanto não permitia que os processadores simulados trocassem informações entre si.

Assim, o SMS implementou rotinas que permitem aos processadores trocarem mensagens entre si, fornecendo um conjunto de bibliotecas que permite o envio e recepção destas mensagens.

Em ambos os simuladores, os espaços de endereçamento de memória e cache são individuais por processador, garantindo que cada processador simulado comporte-se como um processador exclusivo dentro da arquitetura simulada.

As estatísticas geradas por estes simuladores também foram modificadas para devolver os resultados sintetizados por unidade de processamento, fazendo com que cada um dos parâmetros estatísticos do *SimpleScalar* pudesse ser avaliado para cada CPU destes simuladores multiprocessados.

.

# 5 O simulador SMS-MC

Neste capítulo apresentamos os objetivos do desenvolvimento do simulador SMS-MC, assim como suas características e diferenciais. Apresentamos a metodologia utilizada no seu desenvolvimento e explicamos o funcionamento da política aplicada aos protocolos implementados. Descrevemos ainda os principais detalhes da implementação apresentando alguns trechos da estrutura do simulador.

O objetivo principal deste trabalho consistiu em viabilizar uma ferramenta de simulação para Arquiteturas Paralelas com Memória Compartilhada, baseada na estrutura do SimpleScalar e seus derivados (como o MULTIPROC e o SMS). Este simulador representa a classe das máquinas MIMD, segundo a Taxonomia de Flynn, e implementa alguns protocolos de coerência de *cache* para ilustrar a tecnologia envolvida.

O desenvolvimento de uma ferramenta com tais requisitos não poderia ser fundamentada sobre uma estrutura que não estivesse consolidada. Assim, baseado no SimpleScalar, um simulador difundido mundialmente e já consolidado na área de Arquitetura de Computadores, o SMS-MC tende a ter um maior potencial de utilização no ensino e pesquisa.

A ferramenta serve como apoio para avaliação de parâmetros referentes à coerência de *cache* e uso de memória compartilhada, gerando estatísticas úteis na avaliação das arquiteturas simuladas.

Além do propósito final que é permitir avaliação dos modelos de memória compartilhada e seus protocolos, a ferramenta também pode ser utilizada no ensino de desenvolvimento de aplicações paralelas, uma vez que permite a execução (simulação) de equipamentos com múltiplos processadores e diversos protocolos de coerência de *cache*.

Como é baseado numa arquitetura modular, o simulador SMS-MC permite ainda que novos protocolos de coerência de *cache* sejam implementados e inseridos no módulo de *cache*, facilitando a avaliação prática e fácil para possíveis novos protocolos.

5.1 Características 48

### 5.1 Características

O simulador SMS-MC possibilita a execução de diversos processos simultaneamente, cada qual sendo executado por um processador. Cada processador simulado possui uma memória local que é empregada para carregar o programa a ser executado e para a manipulação de variáveis não compartilhadas.

Um espaço de memória específico dentro do simulador disponibiliza a todos os processadores uma área compartilhada. Assim, cada programa (escrito em linguagem C e gerado com um compilador *cross-compiler*) pode declarar variáveis como compartilhadas, tornando-as visíveis para os demais processadores e programas em execução no simulador. É importante ressaltar que na implementação do SMS-MC disponibilizou-se somente *caches* de dados compartilhados, não permitindo a existência de *caches* de instruções compartilhadas, pois isto tomaria um tempo para a definição de primitivas para compartilhamento de código e alterações no código fonte do compilador utilizado para gerar os códigos executáveis do SMS-MC, o que não foi previsto no cronograma e nos objetivos deste trabalho.

Com a estrutura montada pelo simulador, nada impede que as *caches* de instruções possam suportar instruções compartilhadas; o que ainda não é possível no simulador é como definir estes trechos de código compartilhados dentro dos executáveis.

O simulador suporta parâmetros para ajustar o *delay* do acesso à memória compartilhada e o modelo de coerência de *cache* a ser simulado: *none* (nenhum), *snoopy* ou *directory* (baseado em diretórios). O modelo de coerência *none* é utilizado para as *caches* do simulador que não possuem dados compartilhados, como no caso de *caches* de instruções.

Ambos os protocolos de coerência de *cache* implementados no simulador utilizaram a política *write-invalidate* (*Snoopy* e *Directory*) e seguiram o modelo de quatro estados **MESI**. A principal diferença nas duas implementações deve-se ao fato da implementação do protocolo *Snoopy* realizar comunicação exclusivamente através de mensagens no barramento em *broad-cast* enquanto o protocolo *Directory* realiza comunicação através de mensagens aos processadores que realmente contêm os blocos de *caches* (semelhante a uma comunicação *multicast*).

Para permitir análises de desempenho de arquiteturas com diferentes protocolos de coerência de *cache* e memória compartilhada, o simulador SMS-MC gera um conjunto de estatísticas sobre todas as operações realizadas nas memórias *caches*, fornecendo valores para cada uma das operações realizadas nas transições de estados dos blocos das *caches* compartilhadas. Outras estatísticas, antes fornecidas pelo simulador SimpleScalar continuam sendo fornecidas pela ferramenta SMS-MC.

5.2 Diferenciais 49

### 5.2 Diferenciais

Baseado na arquitetura do SimpleScalar, o simulador proposto dispõe de um alto grau de detalhamento da arquitetura modelada. O multiprocessamento fornecido pelo simulador oferece uma alternativa para o uso de *threads*, visto que pode-se executar programas totalmente independentes no simulador e o mesmo irá simular vários processadores trabalhando de forma independente.

Como o simulador é baseado no SimpleScalar, praticamente todos os *benchmarks* desenvolvidos para o SimpleScalar podem facilmente ser adaptados para o simulador proposto, adicionando-se é claro as novas funcionalidades de memória compartilhada presentes no SMS-MC.

Assim, todo o nível de detalhamento que já pode ser obtido com o SimpleScalar, também está disponível neste novo simulador, como por exemplo a possibilidade de alterar as especificações das *caches* de dados e instruções, os parâmetros e modelos dos previsores de desvios, a largura dos barramentos de busca, entre outros.

Este simulador executa códigos compilados para a arquitetura PISA (*Portable Instruction Set Architecture*), um sub-conjunto das instruções da arquitetura MIPS. Logo, com um compilador *gcc* alterado para tal, pode-se compilar códigos C para serem testados diretamente no simulador, não ficando atrelado aos *benchmarks* já existentes.

Mantendo a modularidade do SimpleScalar, o SMS-MC re-implementa os módulos de memória e de *cache*, criando uma camada superior que oculta do processador qual o tipo de *cache* está sendo utilizada, fornecendo interfaces para que os dados compartilhados sejam manipulados. Facilmente novos modelos de *cache* e protocolos de coerência podem ser implementados e incorporados a esta camada de alto nível do módulo de *cache* do simulador, permitindo expandir ainda mais a utilização e abrangência do simulador.

# 5.3 Metodologia

A construção do simulador foi baseada no simulador SMS, que é um simulador de multiprocessadores de memória distribuída baseado no código do SimpleScalar.

O SimpleScalar é capaz de simular um processador MIPS, incluindo previsores de desvios, memória, *caches* e diversos outros parâmetros. O SMS é a versão multiprocessada do Simple-Scalar, permitindo que seja avaliada a execução de diversos processadores ao mesmo tempo, como numa máquina paralela.

5.3 Metodologia 50

Tomando como base o simulador SMS, que já simula o uso de múltiplos processadores, cada qual com sua memória e *cache* individuais, implementamos o simulador SMS-MC (Simulador de Multiprocessadores Superescalares de Memória Compartilhada), que fornece a funcionalidade de usar regiões de memória compartilhada, proporcionando um espaço de endereçamento que é comum a todos os processadores.

Dessa forma, criamos uma estrutura de memória específica para armazenar os dados que são compartilhados. Quando algum processador tenta acessar um dado (ou endereço) que é compartilhado, sua requisição é enviada para esta memória. Um desvio na rotina de inicialização do simulador foi criado para indicar ao simulador que carregue e organize os dados compartilhados nesta memória específica. Isto acontece através de uma interrupção.

As rotinas que efetuam leitura e escrita de dados na memória foram alteradas de forma a permitir que acessos à porção de memória compartilhada sejam efetuados de forma transparente para o processador e para o programador. Assim, quaisquer operações sobre os dados compartilhados são realizadas normalmente, como se fossem sobre variáveis exclusivas.

Uma biblioteca com funções para declarar variáveis compartilhadas e iniciar o modo "*me-mória compartilhada*" foi disponibilizada para que o programador possa desenvolver seus aplicativos fazendo uso do espaço de endereçamento compartilhado. Esta biblioteca deve ser incluída em todos os aplicativos (ou *benchmarks*) que são executados no simulador.

O simulador SMS-MC suporta dois protocolos de coerência de *cache*: um baseado na técnica *Snoopy* e outro baseado na técnica Directory. Ambos são implementações de protocolos de invalidação utilizando quatro estados<sup>1</sup>.

Baseado nas descrições do protocolo MESI, discutidas anteriormente, implementamos estes dois protocolos seguindo o roteiro de execução que é discutido em detalhes na Seção 5.4.

### 5.3.1 Implementação da Memória Compartilhada

Durante os testes na elaboração do projeto do SMS-MC notou-se que todas as variáveis declaradas no início do programa principal de qualquer *benchmark* desenvolvido para o simulador possuíam o mesmo endereço físico de memória. Assim, se as variáveis fossem declaradas com os mesmos nomes e na mesma ordem em todos os *benchmarks* simulados paralelamente, elas ocupariam exatamente as mesmas posições de memória.

Assim, desviando os acessos de leitura e escrita destes endereços de memória para uma

<sup>&</sup>lt;sup>1</sup>Os protocolos de coerência de *cache* que implementam quatro estados geralmente são conhecidos como protocolos MESI.

região de memória específica dentro do simulador, todos os processadores acessariam os mesmos dados, fornecendo a funcionalidade de memória compartilhada para estas variáveis.

Desta forma, definimos um *layout* para ser utilizado nas implementações de *benchmarks* do SMS-MC, que é caracterizado por um arquivo que contém todas as definições de variáveis compartilhadas (chamado *shared.def*), sendo incluído em todos os *benchmarks* exatamente na mesma posição (no início do programa principal), garantindo que todos os *benchmarks* possuam as mesmas variáveis definidas no arquivo *shared.def* exatamente nas mesmas posições.

A partir deste princípio, algumas macros foram definidas para serem utilizadas com objetivo de instruir ao simulador SMS-MC quais as posições físicas destas variáveis definidas no *shared.def* e quais os seus tamanhos. Um padrão para utilização destas macros foi definido, garantindo que elas sejam as primeiras instruções a serem executadas por um dos *benchmarks* em execução no simulador, inicializando as variáveis compartilhadas no SMS-MC.

Uma alteração na máquina de execução do simulador SMS-MC foi realizada para garantir que o simulador carregue todos os endereços de variáveis compartilhadas definidas no shared.def e informados pelas macros. Assim, enquanto todas as variáveis compartilhadas não tiverem sido carregadas nas devidas estruturas, o simulador executa operações NOP para os benchmarks aguardando que as operações de inicialização sejam executadas.

Dessa forma, realizando um desvio nas rotinas de *load* e *store*, podemos direcionar todas as operações nas posições de memória compartilhada para a nova região de memória que foi definida internamente no simulador justamente para conter os dados destas variáveis compartilhadas.

### 5.4 Funcionamento do MESI

No início de uma simulação, todos os blocos presentes na cache estão no estado "Invalid".

Quando um processador deseja realizar uma operação sobre um dado compartilhado, primeiramente verifica em sua *cache* se já possui este dado. Caso possua o dado no estado "*Exclusive*" ou "*Modified*", ele pode realizar normalmente a operação, considerando somente o tempo de acesso à *cache*. Neste caso, o estado do bloco deve ser alterado para "*Modified*" caso a operação seja de escrita.

Se o bloco na *cache* estiver com o estado "*Shared*" e a operação seja de leitura, a operação pode ocorrer normalmente, novamente com a latência do acesso à *cache*. Entretanto, caso o bloco esteja no estado "*Shared*" e a operação seja de escrita, o processador deve avisar todos

os demais processadores <sup>2</sup> que irá atualizar o dado, invalidando as demais cópias do dado em outras *caches*. Vale lembrar que caso alguma das outras *caches* possua o mesmo dado com o estado "*Modified*", ela deve realizar um *write-back* para armazenar o valor do dado na memória.

Na implementação de um protocolo MESI existem 4 situações básicas que devem ser tratadas:

- Read hit:

- Read miss:

- Write hit:

- Write miss.

Para tratar cada uma destas situações, algumas ações nas *caches* são necessárias e são detalhadas a seguir.

#### **5.4.1** Read hit

Esta situação ocorre numa *cache* local quando seu processador tenta executar uma operação de leitura num bloco que já está em *cache*.

O estado do bloco precisa ser "Exclusive", "Shared" ou "Modified" para que a operação seja executada com sucesso. Neste caso, o controlador de cache não precisa enviar nenhuma mensagem para as outras caches.

A única latência no processo será a do acesso ao dado na cache.

#### 5.4.2 Read miss

Esta situação ocorre numa *cache* local quando seu processador tenta executar uma operação de leitura num bloco que ainda não está na *cache*.

Neste caso, o controlador da *cache* precisa enviar uma mensagem às outras *caches* <sup>3</sup> para saber se alguma delas possui o bloco desejado e qual seu possível estado (*Modified*, *Exclusive*, *Shared* ou *Invalid*).

<sup>&</sup>lt;sup>2</sup>Neste caso, vale observar que se o protocolo estiver implementando um *Snoopy Protocol* ele avisará todas as demais caches remotas, numa operação de *broadcast*. Sendo o protocolo implementado baseado nos *Directory Protocols* somente serão notificadas as caches que possuem uma cópia do dado solicitado.

<sup>&</sup>lt;sup>3</sup>Esta mensagem só é necessária caso a implementação seja baseada nos *Snoopy Protocols*, pois neste caso não possui informação alguma sobre quais caches podem conter o bloco que está sendo manipulado.

Neste estado, três possíveis caminhos podem ser seguidos:

- Numa primeira situação, nenhuma das outras caches possui o bloco desejado. Assim, o controlador de cache lê o dado da memória e o armazena na cache com estado marcado como "Exclusive". A latência neste caso seria a de ler o dado da memória, mais os tempos de enviar uma mensagem para todas as demais caches e receber as devidas respostas delas.

- Numa segunda situação, pelo menos uma das caches possui o bloco no estado "Exclusive" ou "Shared". Neste caso, o controlador envia uma nova mensagem informando que deseja "compartilhar" o bloco. Em seguida lê o dado da memória e notifica as demais caches que possuem uma cópia do dado para que alterem o estado do bloco para "Shared". Nesta situação, a latência seria a de ler o dado da memória, enviar uma mensagem a todas as caches solicitando o estado do bloco e, enviar uma nova mensagem solicitando o compartilhamento do bloco.

- Numa terceira situação, uma das caches remotas retorna a informação de que possui o bloco com o estado "Modified". Neste caso, uma nova mensagem solicitando o compartilhamento do bloco é enviada, obrigando a cache que possui o dado alterado a realizar um write-back do dado e alterar o estado do mesmo para "Shared". A cache local pode então ler o bloco da memória e marcar o estado do mesmo como "Shared". Neste caso, a latência total seria a soma das latências de leitura do bloco da memória, mais o envio das mensagens solicitando o estado do bloco nas demais caches, mais o envio das mensagens de compartilhamento do bloco, mais o tempo de write-back do bloco modificado para a memória.

#### 5.4.3 Write hit

Esta situação ocorre numa *cache* local quando o seu processador tenta executar uma operação de escrita num bloco que já está na *cache*.

O estado do bloco precisa ser "Exclusive" ou "Modified" para que a operação possa ser concluída com sucesso. Neste caso, o controlador da cache não precisa enviar mensagens a nenhuma das outras caches. A latência para esta situação é a de executar uma operação de escrita num bloco local na cache.

5.5 Implementação 54

#### 5.4.4 Write miss

Esta situação ocorre numa *cache* local, por dois motivos, quando o processador tenta executar uma operação de escrita num bloco de *cache*:

- o bloco não está presente na *cache* local;

- o bloco está presente na cache local, mas com o estado "Shared".

Em ambas as situações, o controlador da *cache* envia mensagens para todas as outras *caches*, solicitando que invalidem suas cópias do bloco que deseja atualizar. Caso alguma das outras *caches* possua o dado com o estado "*Modified*", deve fazer uma operação *write-back* e marcar seu bloco localmente com o estado "*Invalid*".

Caso as outras *caches* possuam o dado, mas em outro estado diferente de "*Modified*", simplesmente marcam este bloco com o estado "*Invalid*". Assim, se o bloco estiver na *cache* local, mesmo com o estado "*Shared*", a operação de escrita é realizada, alterando o estado do bloco para "*Modified*". Se o bloco não estiver na *cache*, ele é então carregado da memória para a *cache* e a operação de escrita é realizada.

Neste caso, a latência do procedimento seria a de invalidar as demais *caches* e realizar a operação de escrita no bloco local da *cache*.

# 5.5 Implementação

O simulador SimpleScalar, base da implementação do SMS-MC, é um simulador desenvolvido em linguagem C e totalmente modularizado. O início da fase de implementação deste trabalho de mestrado conduziu um estudo aprofundado sobre a estrutura do SimpleScalar.

Sendo modularizado, os arquivos (ou módulos) responsáveis por memória e *cache* foram documentados e depurados para que a tarefa de customização desta parte do simulador pudesse ser executada de maneira mais efetiva.

Assim, alterações foram feitas basicamente em três arquivos: *memory.c/memory.h*, *ca-che.c/cache.h* e *sms-mc.c/sms-mc.h*.

Algumas estruturas novas foram definidas no arquivo *memory.h* para suportar o modelo de memória compartilhada, incluindo modificações em estruturas já existentes, como as *páginas de memória* compartilhadas, que podem ser notadas no fragmento Código 1, onde pode ser

5.5 Implementação 55

verificada a adição da variável ptab\_shared\_access representando a quantidade de acessos a páginas de dados compartilhados.

#### Código 1 Estruturas da memória definidas em memory.h

```

struct mem_t {

char *name;

struct mem_pte_t *ptab[MEM_PTAB_SIZE];

counter_t page_count;

counter_t ptab_misses;

counter_t nb_shared;

counter_t ptab_accesses;

counter_t ptab_accesses;

}

```

Outras estruturas foram definidas para implementação da região compartilhada de memória, que foi implementada através de uma lista dinâmica levando em consideração que endereços aleatórios podem ser compartilhados no simulador. Estas alterações podem ser visualizadas no fragmento Código 2, onde nota-se a estrutura dos nós da lista ligada utilizada para implementar a região de memória compartilhada.

#### Código 2 Estruturas da memória compartilhada definido em memory.h

```

struct nodo_shared{

md_addr_t address;

struct nodo_shared *next;

};

struct mem_t *shared;

```

No fragmento Código 3 temos três funções de apoio que foram definidas para auxílio na rotina de leitura e escrita da memória, com objetivo de facilitar a identificação de endereços compartilhados. Caso um endereço solicitado para as rotinas de leitura / escrita seja reconhecido como compartilhado, ocorre um desvio na rotina para a região de memória compartilhada.

#### Código 3 Rotinas de apoio definidas em memory. h e implementadas em memory. c

5.5 Implementação 56

Uma alteração foi realizada na função de inicialização do sistema de memória, sendo ela responsável por zerar as estatísticas de acesso à memória compartilhada, conforme pode ser visto no fragmento Código 4.

**Código 4** Rotinas de inicialização da memória, definidas em memory.h e implementadas em memory.c

```

void mem_init( struct mem_t *mem){

int i;

for (i=0; i < MEM_PTAB_SIZE; i++)

mem->ptab[i] = NULL;

mem->page_count = 0;

mem->ptab_misses = 0;

mem->ptab_accesses = 0;

mem->ptab_shared_access = 0;

mem->nb_shared = 0;

}

```

As principais alterações para disponibilizar o acesso à região compartilhada de memória do simulador SMS-MC foram realizadas na função mem\_access(), encontrada no arquivo *memory.c.* Toda vez que o acesso é solicitado para um determinado endereço (seja ele numa operação de leitura ou escrita), a rotina de leitura verifica através de uma rotina auxiliar (get\_bit\_shared()) se o endereço corresponde a um endereço de memória compartilhada. No caso negativo, o acesso ocorre normalmente, como qualquer outro acesso à memória disponibilizado no simulador. Entretanto, sendo um endereço de memória compartilhada, a rotina faz um desvio para o acesso à estrutura com a memória compartilhada. O fragmento Código 5 mostra a parte principal da implementação da função mem\_access().

Ainda no módulo de memória alterações foram executadas também no código da função que gera as estatísticas de acesso, chamada de mem\_reg\_stats(), incluindo algumas estatísticas referentes aos dados compartilhados, como pode ser visto no fragmento Código 6.

Para implementarmos os protocolos de coerência de cache, fez-se necessário alterações nos módulos cache.c e cache.h. Algumas estruturas foram definidas para representar os protocolos de coerência de *cache* e os estados de um determinado bloco da *cache*, conforme pode ser observado nos fragmentos Código 7 e Código 8.

As rotinas de geração de estatísticas da *cache* também foram alteradas de maneira a prover dados sobre os acessos, estados e o protocolo de coerência simulado. Alguns detalhes da alteração podem ser visualizados no fragmento Código 9.

A rotina utilizada para instanciar as *caches* foi readequada de maneira a suportar a seleção do protocolo a ser utilizado pela cache e zerar os contadores referentes aos acessos de memória

Código 5 Rotina de acesso à memória definida em memory. h e implementada em memory. c.

```

enum md_fault_type

mem_access( struct mem_t *mem, /* memory space to access */

enum mem_cmd cmd, /* Read (from sim mem) or Write */

md_addr_t addr,

/* target address to access */

/* host memory address to access */

void *vp,

int nbytes,

/* number of bytes to access */

/* slot number */

int sn)

{

byte_t *p = vp;

struct mem_pte_t *temp=NULL;

int _shared=0;

if(loaded_shared_vars) {

if( get_bit_shared(addr) ) {

_{shared} = 1;

mem->ptab_shared_access++;

} else {

_shared = 0;

}

}

switch (nbytes) {

case 1: if (cmd == Read) {

if( _shared ) *((byte_t *)p) = MEM_READ_BYTE(shared, addr)

else *((byte_t *)p) = MEM_READ_BYTE(mem, addr);

if( _shared ) MEM_WRITE_BYTE(shared, addr, *((byte_t *)p))

else MEM_WRITE_BYTE(mem, addr, *((byte_t *)p));

}

break;

}

return md_fault_none;

}

```

compartilhada, conforme o fragmento Código 10.

Para prover acesso à *cache* de dados compartilhados, implementando os dois protocolos de coerência de *cache* disponíveis no SMS-MC, alterações foram realizadas na função mem\_access(), direcionando o acesso para o módulo correspondente no simulador: *Directory* ou *Snoopy*. Estas alterações podem ser verificadas no fragmento Código 11.

# 5.6 Utilização do Simulador

Para utilização do simulador SMS-MC devemos seguir alguns procedimentos ao implementar os *benchmarks*:

**Código 6** Rotina de geração de estatísticas definida em memory.h e implementada em memory.c.

```

void mem_reg_stats( struct mem_t **mem,

struct stat_sdb_t *sdb)

{

char buf[512], buf1[512];

for (sn=0;sn<USED_SLOTS;sn++) {</pre>

sprintf(buf, "shared_bytes.cpu_%s", itoa(sn));

stat_reg_counter(sdb, buf, "total shared bytes",

&shared->nb_shared, shared->nb_shared, NULL,sn);

for (sn=0;sn<USED_SLOTS;sn++) {</pre>

sprintf(buf, "ptab_shared_access.cpu_%s", itoa(sn));

stat_reg_counter(sdb, buf, "total shared page table accesses",